使用客户规格书,制作屏参文件。

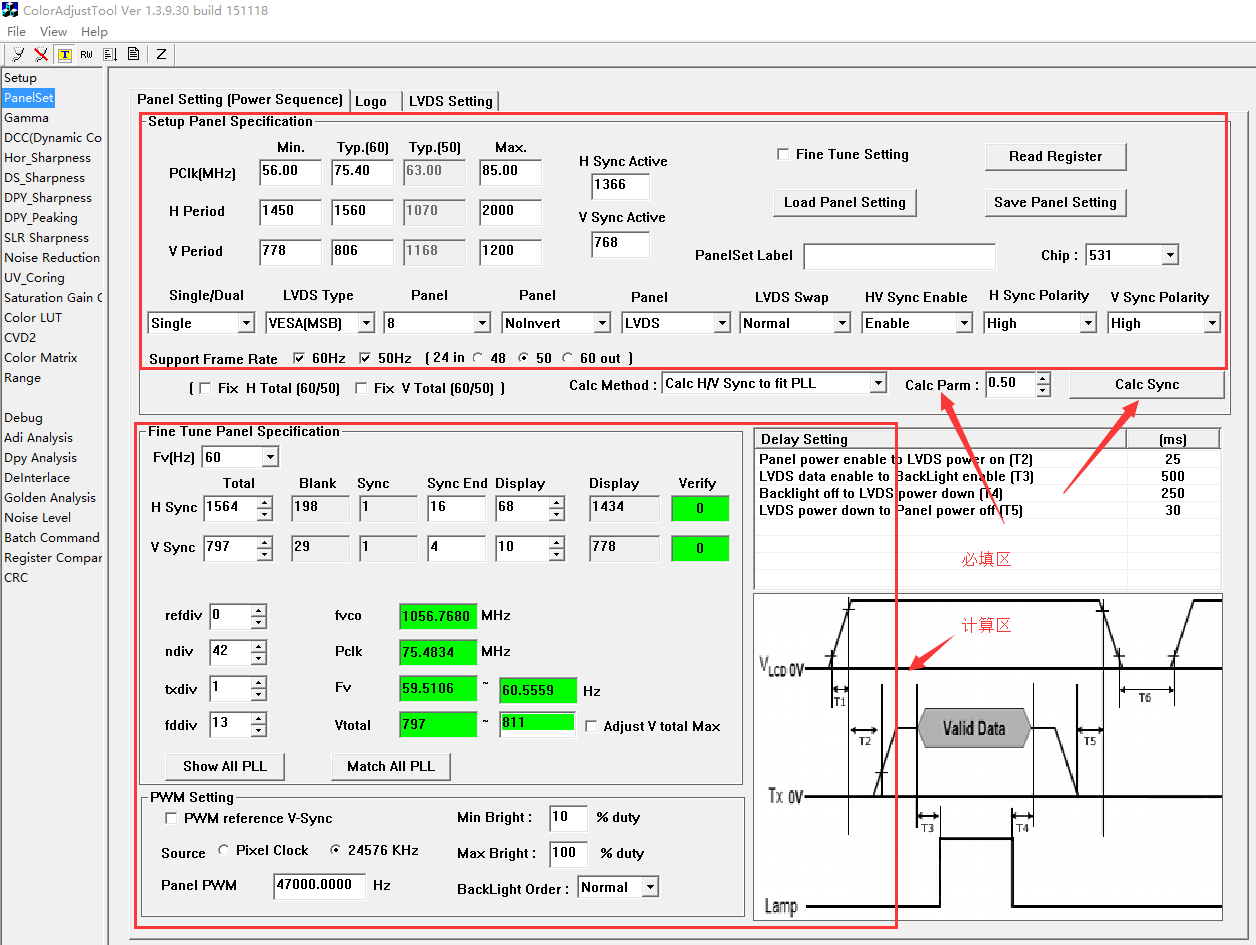

注意:,必填区和计算区,必填区根据屏参的SPEC填写,具体的屏参文件参数通过点击“Calc Sync”生成。

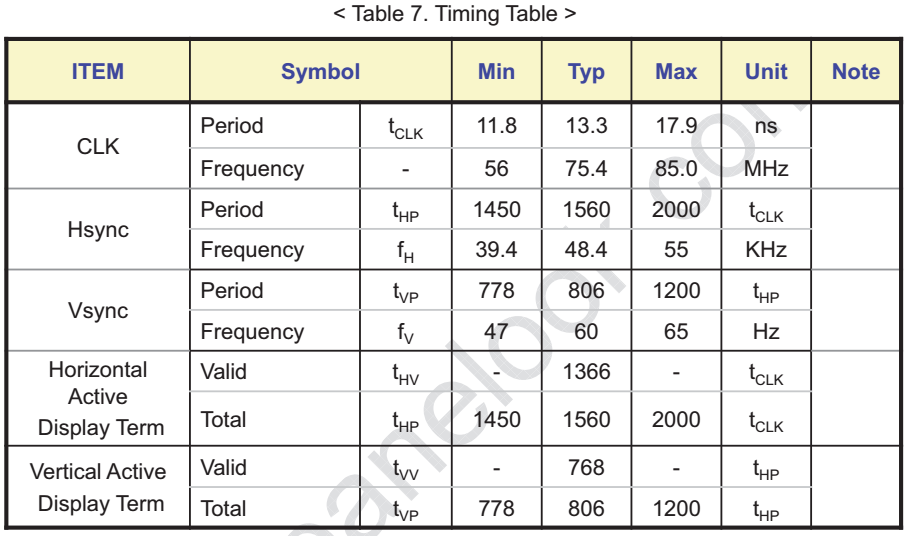

如:HV320WHB-N81的SPEC:

打开“ColorAdjustTool”

1、根据规格书的CLK/Hsync/Vsync/Horizontal Active/Vertical Active参数填写“必填区”

2、点击“Calc Sync”生成详细的参数

3、点击“Save Panel Setting”生成最终程序使用的“panel_setting.h”文件

注意:

a) PWM要调成47K

b) 勾选“Fine Tune Setting”可以在线调试装机市场的屏参。

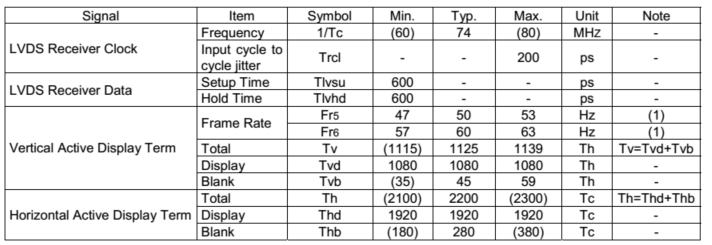

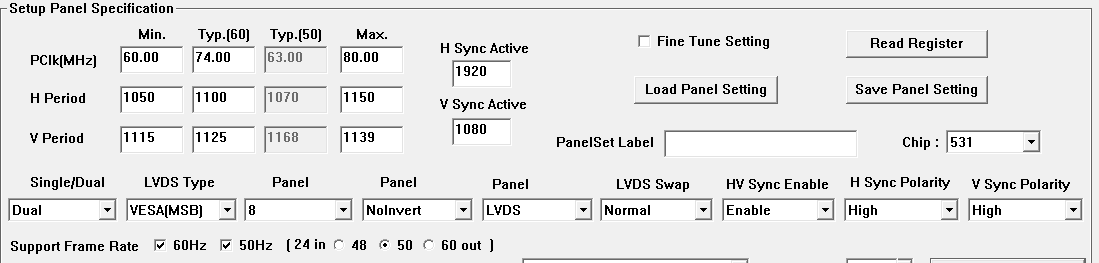

c) 工具计算区“H Period”,对于双路LVDS,填写的是单路的值,如1920X1080的屏参。

如:1920X1080:

对应工具参数如下:

“panel_setting.h”生成如下:

#define PANEL_TYPE "HV320WHB-N81" /******************************************************************************* * Power Sequence ********************************************************************************/ #define PANEL_POWERENABLE_TO_LVDS_POWERON_T2 25 #define PANEL_LVDS_DATAEN_TO_BLEN_T3 500 #define PANEL_BLOFF_TO_LVDS_POWER_DOWN_T4 250 #define PANEL_LVDS_POWER_DOWN_TO_PANEL_POWER_OFF_T5 30 /******************************************************************************* * Panel Spec(DEC) ********************************************************************************/ #define PANEL_PCLK 75.40 #define PANEL_PCLK_PAL 63.00 #define PANEL_PCLK_MAX 85.00 #define PANEL_PCLK_MIN 56.00 #define PANEL_WIDTH 1366 #define PANEL_HEIGHT 768 #define PANEL_MAX_HTOTAL 2000 #define PANEL_TYP_HTOTAL 1560 #define PANEL_TYP_HTOTAL_PAL 1070 #define PANEL_MIN_HTOTAL 1450 #define PANEL_MAX_VTOTAL 1200 #define PANEL_TYP_VTOTAL 806 #define PANEL_TYP_VTOTAL_PAL 1168 #define PANEL_MIN_VTOTAL 778 //0: NoInvert, 1: Invert #define PANEL_INVERT 0 //0: NoSwap, 1: Swap #define PANEL_LVDS_SWAP 0 //1: Single, 2: Dual #define PANEL_CHANNEL_NUM 1 //6: 6 bit, 8: 8 bit, 10: 10 bit, 12: 12 bit #define PANEL_COLOR_DEPTH 8 //0: JEDIA, 1: VESA(LSB), 2: VESA(MSB) #define PANEL_LVDS_TYPE 2 //0: LVDS, 1: DP #define PANEL_INTERFACE 0 //0: H/VSyncEn(default), 1:H/VSyncDis #define PANEL_HVSYNC_EN 0 //0: High Active, 1: Low Active #define PANEL_HSYNC_POLARITY 0 //0: High Active, 1: Low Active #define PANEL_VSYNC_POLARITY 0 /******************************************************************************* * Panel Setting ********************************************************************************/ //60Hz #define PANEL_PLL_REFDIV_60HZ 0 #define PANEL_PLL_NDIV_60HZ 42 #define PANEL_PLL_TXDIV_60HZ 1 #define PANEL_PLL_FDDIV_60HZ 13 #define PANEL_HSYNC_START_60HZ 1 #define PANEL_HSYNC_END_60HZ 8 #define PANEL_HVALID_START_60HZ 34 #define PANEL_HVALID_END_60HZ 717 #define PANEL_VSYNC_START_60HZ 1 #define PANEL_VSYNC_END_60HZ 4 #define PANEL_VVALID_START_60HZ 10 #define PANEL_VVALID_END_60HZ 778 #define PANEL_HTOTAL_60HZ 781 #define PANEL_VTOTAL_60HZ 796 #define PANEL_MAX_VTOTAL_60HZ 811 //50Hz #define PANEL_PLL_REFDIV_50HZ 0 #define PANEL_PLL_NDIV_50HZ 42 #define PANEL_PLL_TXDIV_50HZ 1 #define PANEL_PLL_FDDIV_50HZ 13 #define PANEL_HSYNC_START_50HZ 1 #define PANEL_HSYNC_END_50HZ 6 #define PANEL_HVALID_START_50HZ 24 #define PANEL_HVALID_END_50HZ 707 #define PANEL_VSYNC_START_50HZ 1 #define PANEL_VSYNC_END_50HZ 26 #define PANEL_VVALID_START_50HZ 76 #define PANEL_VVALID_END_50HZ 844 #define PANEL_HTOTAL_50HZ 752 #define PANEL_VTOTAL_50HZ 991 #define PANEL_MAX_VTOTAL_50HZ 1012 //48Hz #define PANEL_PLL_REFDIV_48HZ 0 #define PANEL_PLL_NDIV_48HZ 0 #define PANEL_PLL_TXDIV_48HZ 0 #define PANEL_PLL_FDDIV_48HZ 0 #define PANEL_HSYNC_START_48HZ 0 #define PANEL_HSYNC_END_48HZ 0 #define PANEL_HVALID_START_48HZ 0 #define PANEL_HVALID_END_48HZ 0 #define PANEL_VSYNC_START_48HZ 0 #define PANEL_VSYNC_END_48HZ 0 #define PANEL_VVALID_START_48HZ 0 #define PANEL_VVALID_END_48HZ 0 #define PANEL_HTOTAL_48HZ 0 #define PANEL_VTOTAL_48HZ 0 #define PANEL_MAX_VTOTAL_48HZ 0 /******************************************************************************* * Panel Backlight Mapping ********************************************************************************/ //Hz #define PANEL_PWM_FREQ 47000 //0 : NoInvert, 1 : Invert #define PANEL_BL_INVERT 0 //0 : NoRef VSync, 1 : RefVSync #define PANEL_PWM_REF_VSYNC 0 //0 : PixelClock, 1 : 24576KHz(default) #define PANEL_PWM_SRC 1 #define PANEL_PWM_DUTY_MIN 10 #define PANEL_PWM_DUTY_MAX 100

浙公网安备 33010602011771号

浙公网安备 33010602011771号