vivado时序约束小发现

随笔

近期在修改时序的时候,准备把约束文件里不生效的删除,发现 synthesis 下的 timing constraint 和 implementation 下的不太一样

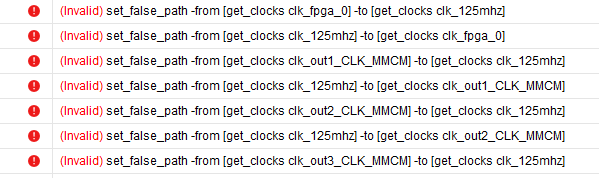

这是 synthesis 下部分的 invalid 约束,

但是 implementation 中并没有出现 invalid

分别在 synthesis 和 implementation 中使用 get_clocks 命令获取时钟,将不一样的部分加粗显示

synthesis 中时钟如下

clk_fpga_0 U_GEN_CLK_INST/U_CLK_MMCM_INST/inst/clk_in1 clkfbout_CLK_MMCM clk_out1_CLK_MMCM clk_out2_CLK_MMCM clk_out3_CLK_MMCM clk_out4_CLK_MMCM clk_out5_CLK_MMCM clk_out7_CLK_MMCM I_sys_clk_p I_RF_dclk_p ECG_R_clk_4m TT_R_clk_out TT_R_clk_out1 virt_clock_trig_400MHz clk_out6_CLK_MMCM

implementation 中时钟如下

clk_fpga_0 U_GEN_CLK_INST/U_CLK_MMCM_INST/inst/clk_in1 clkfbout_CLK_MMCM clk_out1_CLK_MMCM clk_out2_CLK_MMCM clk_out3_CLK_MMCM clk_out4_CLK_MMCM clk_out5_CLK_MMCM clk_out7_CLK_MMCM I_sys_clk_p I_RF_dclk_p ECG_R_clk_4m TT_R_clk_out TT_R_clk_out1 virt_clock_trig_400MHz mmcm_fb clk_125mhz clk_250mhz txoutclk_x0y0

clk_125mhz 是可以在 implementation 中直接使用 get_clocks 找到的

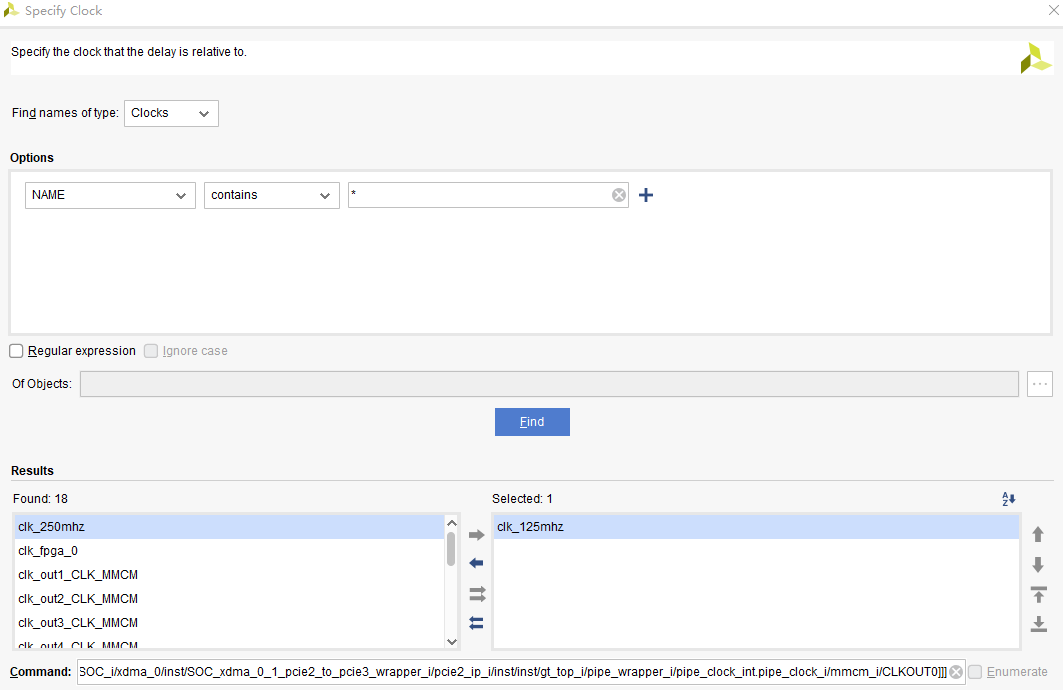

command 在添加 clk_125mhz 时的命令如下:

get_clocks [list [get_clocks -of_objects [get_pins U_SOC_INST/SOC_i/xdma_0/inst/SOC_xdma_0_1_pcie2_to_pcie3_wrapper_i/pcie2_ip_i/inst/inst/gt_top_i/pipe_wrapper_i/pipe_clock_int.pipe_clock_i/mmcm_i/CLKOUT0]]]

在约束时用这么长一段来找到对应时钟太麻烦了,使用下面的命令是一样的效果

get_clocks clk_125mhz

这里的clk_125mhz是 blockdesign 内 xdma ip 核出来的设置的 AXI 时钟。

浙公网安备 33010602011771号

浙公网安备 33010602011771号