STM32 时钟系统

STM32 时钟系统

1.基础认识

为什么要有时钟?

时钟就是单片机的心脏,其每跳动一次,整个单片机的电路就会同步动作一次。时钟的速率决定了两次动作的间隔时间。速率越快,单片机在单位时间内所执行的动作将越多。

时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。

时钟系统就是CPU的脉搏,决定cpu速率。

- 类比:军队指挥员,喊一声命令,各军队动一下,指令喊的越快,军队行动越迅速。

- 所以,时钟速率越快,单片机在单位时间内执行的动作会变多,从而单片机的处理能力越强。

为什么有多个时钟源?

STM32 系统是复杂的,高精度、低精度、高速、低速等,且可以对每个时钟源进行开关操作,可以把不需要使用的关闭掉。

这可以让单片机适用更多的环境中,把选择权利交个了开发者,开发者可以从精度、功耗、资源等多方面考虑。

- 一方面,匹配不同的外设速度要求。

- 另一方面,省电,类比房间的灯光,把不需要用电的房间灯关掉,减少能耗。

STM32时钟分类

从时钟源与时钟速率的关系,时钟系统分为两个部分:时钟源与时钟速率。

从【时钟源】的角度可分为:

- 内部时钟(I)

- 外部时钟(E)

从时钟速率的角度分为:

- 低速时钟(LS)

- 高速时钟(HS)

因此组合起来,STM32时钟系统有4种时钟:

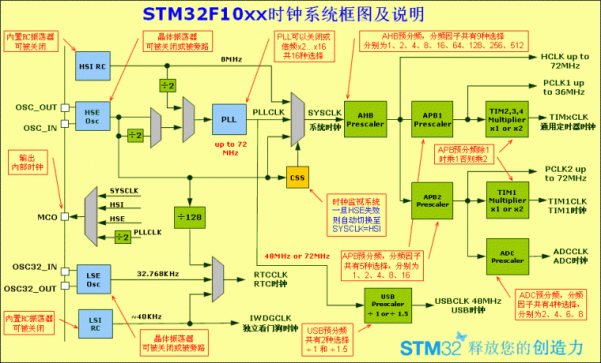

STM32有4个时钟源 LSI、LSE、HSI、HSE。

- 低速时钟(LSE和LSI)只是提供给芯片中的RTC(实时时钟)及独立看门狗使用。

- 高速时钟(HSE和HSI)提供给芯片体的主时钟。高速时钟也可以提供给RTC。

2.时钟系统结构

内部时钟是在芯片内部RC振荡器产生的,起振较快,所以时钟在芯片刚上电的时候,【默认使用内部高速时钟】。

而外部时钟信号是由外部的晶振输入的,在精度和稳定性上都有很大优势,所以上电之后我们再通过软件配置,转而采用外部时钟信号.

-

低速外部时钟(LSE):外部低速时钟,精度高,可接外部晶体/陶瓷谐振器或旁路时钟源。主要提供给【实时时钟模块】,所以一般采用 32.768KHz。

-

低速内部时钟(LSI):内部低速RC振荡器,相比于外部精度较低。也主要提供给【实时时钟模块】,通常作为【看门狗时钟源】。频率大约为 40KHz。

-

高速外部时钟(HSE):精度高,可接外部晶体/陶瓷谐振器或旁路时钟源。晶振频率可取范围为 4~16MHz,一般采用【8MHz的晶振】。通常通过PLL倍频作为系统时钟源。

-

高速内部时钟(HSI):内部高速RC振荡器,相比于外部精度较低。由内部RC振荡器产生,频率为 8MHz,但不稳定。

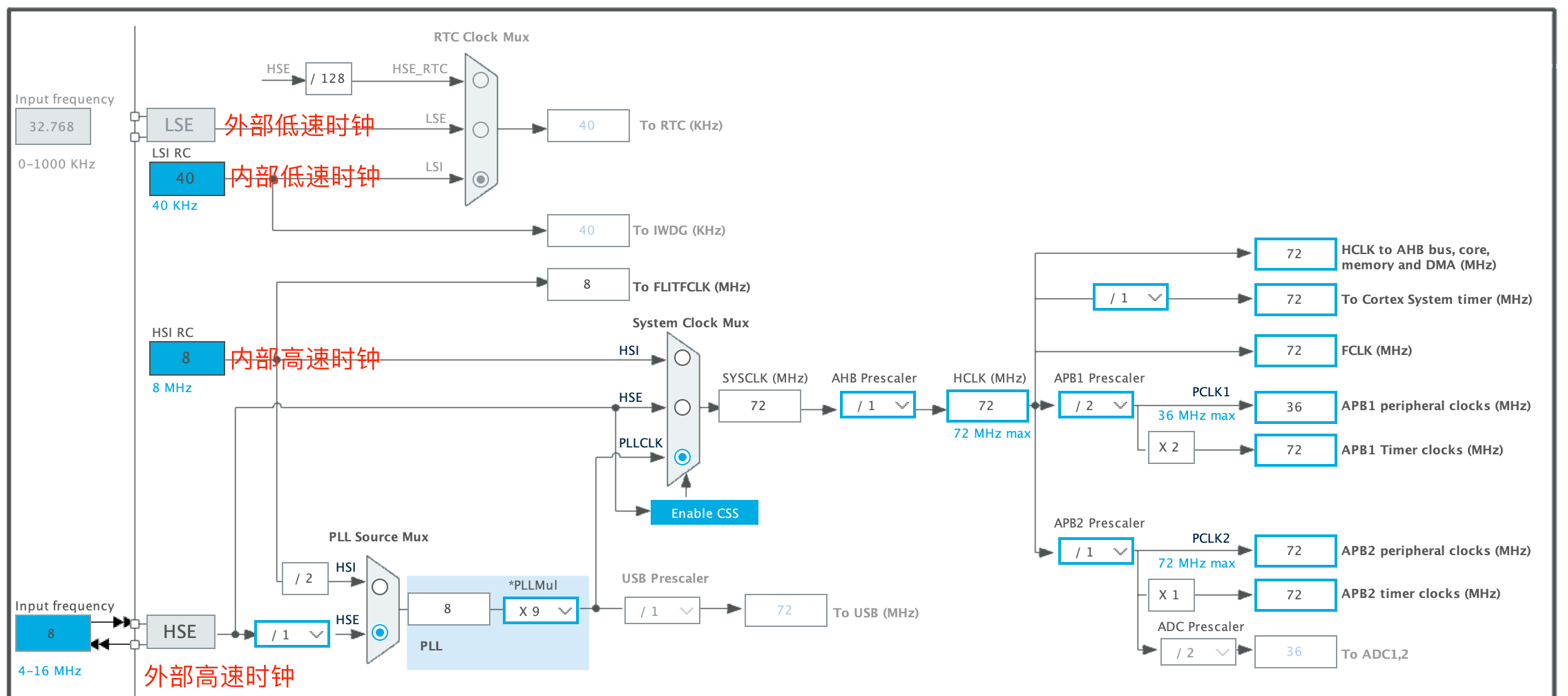

OSC_OUT 和 OSC_IN 开始,这两个引脚分别接到外部晶振8MHz,第一个分频器PLLXTPRE,遇到开关PLLSRC(PLL entry clock source),我们可以选择其输出,输出为外部高速时钟(HSE)或是内部高速时钟(HSI)。

这里选择输出为HSE,接着遇到锁相环PLL,具有倍频作用,在这里我们可以输入倍频因子PLLMUL,要是想超频,就得在这个寄存器上做手脚啦。

经过PLL的时钟称为PLLCLK。倍频因子我们设定为9倍频,也就是说,经过PLL之后,我们的时钟从原来8MHz的 HSE变为72MHz的PLLCLK。

紧接着又遇到了一个开关SW,经过这个开关之后就是STM32的系统时钟(SYSCLK)了。通过这个开关,可以切换SYSCLK的时钟源,可以选择为HSI、PLLCLK、HSE。

我们选择为PLLCLK时钟,所以SYSCLK就为72MHz了。

PLLCLK在输入到SW前,还流向了USB预分频器,这个分频器输出为USB外设的时钟(USBCLK)。

回到SYSCLK,SYSCLK经过AHB预分频器,分频后再输入到其它外设。如输出到称为HCLK、FCLK的时钟,还直接输出到SDIO外设的 SDIOCLK时钟、存储器控制器FSMC的FSMCCLK时钟,和作为APB1、APB2的预分频器的输入端。

GPIO外设是挂载在APB2总线上的, APB2的时钟是APB2预分频器的输出,而APB2预分频器的时钟来源是AHB预分频器。因此,把APB2预分频器设置为不分频,那么我们就可以得到GPIO外设的时钟也等于HCLK,为72MHz了。

- SYSCLK:系统时钟,STM32大部分器件的时钟来源。主要由AHB预分频器分配到各个部件。

- HCLK:由AHB预分频器直接输出得到,它是高速总线AHB的时钟信号,提供给存储器,DMA及cortex内核,是cortex内核运行的时钟,cpu主频就是这个信号,它的大小与STM32运算速度,数据存取速度密切相关。

- FCLK:同样由AHB预分频器输出得到,是内核的“自由运行时钟”。“自由”表现在它不来自时钟 HCLK,因此在HCLK时钟停止时 FCLK 也继续运行。它的存在,可以保证在处理器休眠时,也能够采样和到中断和跟踪休眠事件 ,它与HCLK互相同步。

APB1总线上的外设

PCLK1:外设时钟,由APB1预分频器输出得到,最大频率为36MHz,提供给挂载在APB1总线上的外设,APB1总线上的外设如下:

| 名称 | 说明 |

|---|---|

| RCC_APB1Periph_TIM2 | TIM2时钟 |

| RCC_APB1Periph_TIM3 | TIM3时钟 |

| RCC_APB1Periph_TIM4 | TIM4时钟 |

| RCC_APB1Periph_WWDG | WWDG时钟 |

| RCC_APB1Periph_SPI2 | SPI2时钟 |

| RCC_APB1Periph_USART2 | USART2时钟 |

| RCC_APB1Periph_USART3 | USART3时钟 |

| RCC_APB1Periph_I2C1 | I2C1时钟 |

| RCC_APB1Periph_I2C2 | I2C2时钟 |

| RCC_APB1Periph_USB | USB时钟 |

| RCC_APB1Periph_CAN | CAN时钟 |

| RCC_APB1Periph_BKP | BKP时钟 |

| RCC_APB1Periph_PWR | PWR时钟 |

| RCC_APB1Periph_ALL | 全部APB1外设时钟 |

APB2总线上的外设

PCLK2:外设时钟,由APB2预分频器输出得到,最大频率可为72MHz,提供给挂载在APB2总线上的外设,APB2总线上的外设如下:

| 名称 | 说明 |

|---|---|

| RCC_APB2Periph_AFIO | 功能复用IO时钟 |

| RCC_APB2Periph_GPIOA | GPIOA时钟 |

| RCC_APB2Periph_GPIOB | GPIOB时钟 |

| RCC_APB2Periph_GPIOC | GPIOC时钟 |

| RCC_APB2Periph_GPIOD | GPIOD时钟 |

| RCC_APB2Periph_GPIOE | GPIOE时钟 |

| RCC_APB2Periph_ADC1 | ADC1时钟 |

| RCC_APB2Periph_ADC2 | ADC2时钟 |

| RCC_APB2Periph_TIM1 | TIM1时钟 |

| RCC_APB2Periph_SPI1 | SPI1时钟 |

| RCC_APB2Periph_USART1 | USART1时钟 |

| RCC_APB2Periph_ALL | 全部APB2外设时钟 |

3.外部时钟模式

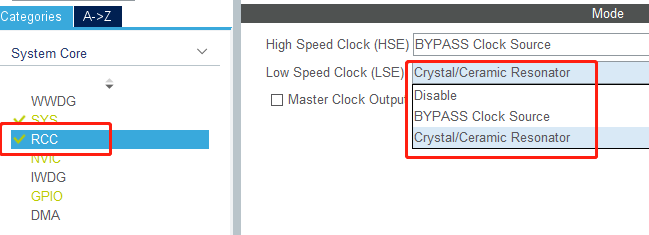

外部的高速和低速时钟均有这三个可选项目,下图是 CubeMX提供的外部时钟选择:

可选类型为:

- Disable(关闭,不使用外部时钟)

- BYPASS Clock Source(旁路时钟源)

- Crystal/Ceramic Resonator(外部晶体/陶瓷谐振器)

外部晶体/陶瓷谐振器模式

该模式较为常见,这可以为系统时钟提供较为精确的时钟源。该时钟源是由外部无源晶体与MCU内部时钟驱动电路共同配合形成,有一定的启动时间,精度较高。为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容必须尽可能地靠近振荡器引脚。负载电容值必须根据所选择的晶体来具体调整。

整体上讲,陶瓷晶体和石英晶体的主要区别就在于精度和温度稳定性上。石英晶体比陶瓷晶体精度要高,温度稳定性要好。

旁路时钟源模式

该模式下必须提供外部时钟。外部时钟信号(50%占空比的方波、正弦波或三角波)必须连到SOC_IN引脚,此时OSC_OUT引脚对外呈高阻态。

所谓旁路模式,是指无需上面提到的使用外部晶体时所需的芯片内部时钟驱动组件,直接从外界导入时钟信号。

旁路时钟源的典型应用--有源晶振

有源晶振一般是四脚封装,电源、地线、振荡输出和一个控制端【或者悬空端】。相比无源晶体,有源晶振本身就是个完整的振荡器件,只需要供给适当的电源就能输出时钟,无须额外的振荡驱动匹配电路。其时钟输出不依赖于外部器件振荡电路,相对更不容易受外部线路不稳定性的影响。自然其价格往往要高于无源晶体,不过其输出电平幅度往往不能像无源晶体那样随着应用电路的变化而变化。

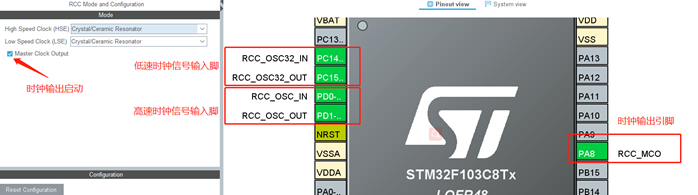

4.STM32F103C8T6芯片时钟引脚

- PC14 和 PC15 是【外部低速时钟】的输入脚

- PD0 和 PD1 是【外部高速时钟】的输入脚

- PA8 是【时钟输出引脚】输出的时钟可编程选择

通常外部高速和低速时钟输入脚在不使用的情况下也尽量不要作为普通独立IO使用

参考文档:

浙公网安备 33010602011771号

浙公网安备 33010602011771号