挑战(二):两周自己动手写CPU(第二章:可编程逻辑器件与Verilog HDL)

一、PLD(Programmable Logic Device):可编程逻辑器件(FPGA属于PLD中的一种,Field Programmable Gate Array:现场可编程门阵列)

PLD器件分类

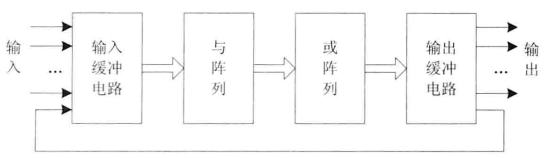

(1)基于乘积项(Product-Term)结构的PLD器件:利用与或阵列,灵活配置的互连线实现任意逻辑功能,但器件规模不大;PROM、PLA、PAL、GAL、EPLD:多采用EEPROM或Flash工艺制作,掉电后不会丢失配置数据

任何组合逻辑电路都可以化为“与或”表达式,用“与门-或门”两级电路实现,而任何时序电路又由组合电路与存储元件(触发器)构成。因此原理上来说,与或阵列加上触发器的结构即可实现任意的数字逻辑电路。

“与或阵列”:实现各种逻辑函数和逻辑功能;

输入缓冲电路:产生输入信号的原变量和反变量;

输出缓冲电路:对将要输出的信号进行处理,既能输出纯组合逻辑信号,又能输出时序逻辑信号;

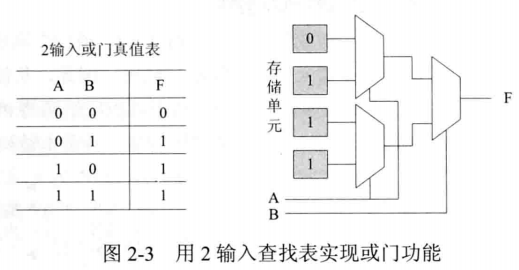

(2)基于查找表(Look-Up Table, LUT )结构的PLD器件:物理结构基于静态存储器(MStatic RAM,SRA)和数据选择器(MUX),通过查找表方式实现函数功能。函数值放在SRAM中,SRAM的地址线即输入变量,不同的输入通过MUX找到对应的函数值并输出。N个输入项的逻辑函数可以由一个2N位容量的SRAM实现。FPGA:其查找表的输入变量一般不超过5个,多余5个输入变量的逻辑函数可由多个查找表通过组合或级联实现。

PS:FPGA大多基于SRAM查找表结构实现,集成度高(可实现百万逻辑门以上设计规模)、逻辑功能强、可实现大规模数字系统设计和复杂的算法运算,但掉电后会丢失配置数据,需外挂非易失配置器以存储配置数据,才能构成可独立运行的系统。在FPGA内部一般还会集成更多的逻辑功能块,如存储器块、DSP块、硬件乘法器、数字锁相环等,用以满足数字信号处理、数字通信等应用的需要。

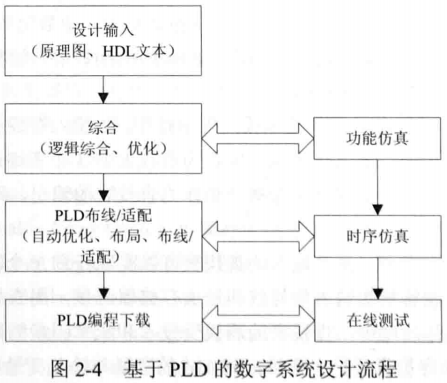

二、基于PLD的数字系统设计流程

三、Verilog HDL

1、过程语句:

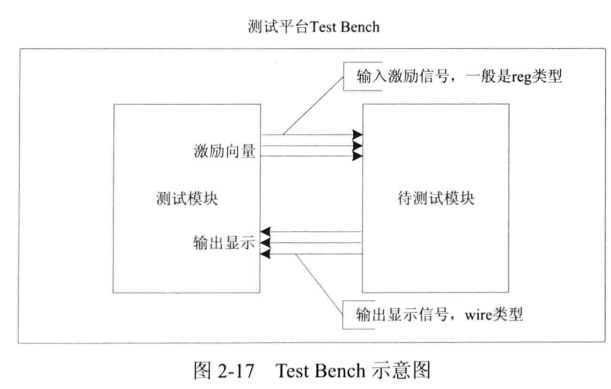

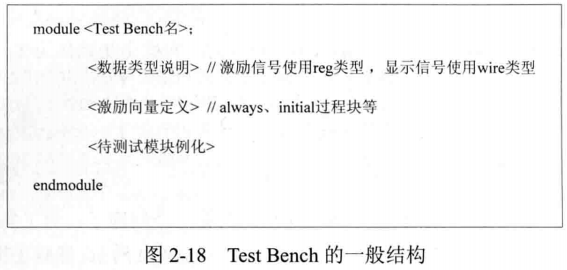

(1)initial:用于仿真模块中对激励向量的描述,或用于给寄存器赋初值,不带触发条件,其中的语句只执行一次,initial语句是面向模拟仿真的过程语句,是不可综合的;

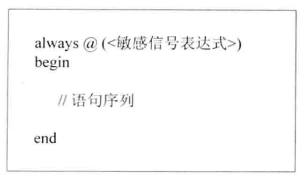

(2)always:其中的语句不断重复执行,always过程语句是可综合的;通常是带有触发条件的,触发条件写在敏感信号表达式中,当敏感信号表达式中的变量值改变时,就会引发其中语句序列的执行;当用”*“表示时,意味着在该过程语句中的所有输入信号变量;

敏感信号分为两种类型:电平敏感型(组合电路)、边沿敏感型(时序电路)

2、条件语句:

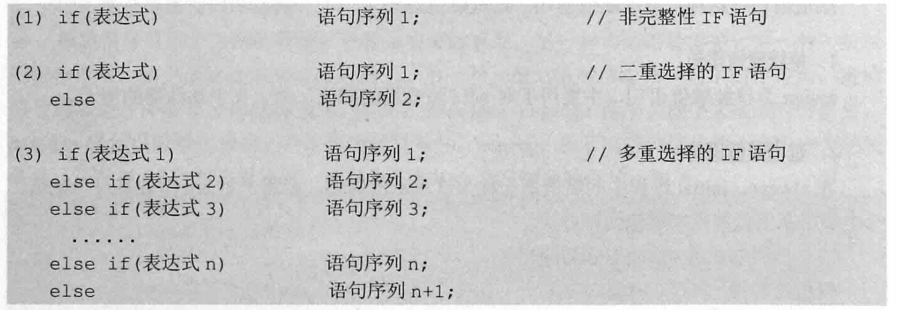

(1)if-else语句

注意:”1“为真,”0、X、Z“为假;

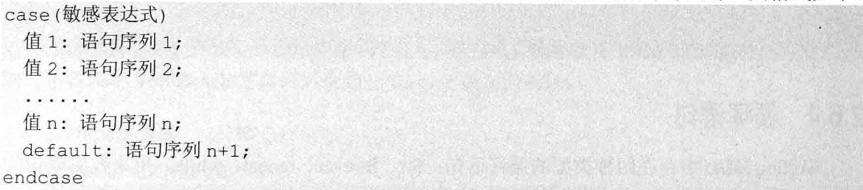

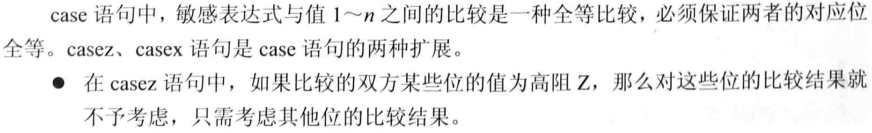

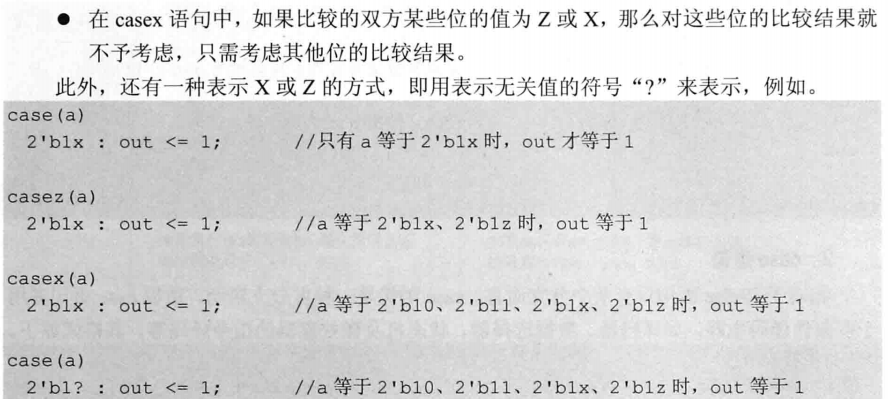

(2)case语句:

3、循环语句

(1)forever:连续不断的执行其中的语句序列,常用来产生周期性的波形;写Test Bench文件时会用到;

(2)repeat语句:

4、编译指示语句:在编译时,通常先对这些指示语句进行预处理,然后再将预处理的结果和源程序一起进行编译;

(1)宏替换'define:用一个简单的名字或有意义的标识代替一个复杂的名字或变量;

(2)文件包含语句'include:将一个文件全部包含到另一个文件中;

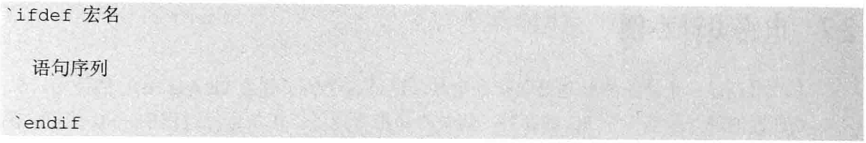

(3)条件编译语句‘ifdef、'else、’endif:可以指定仅对程序中的部分内容进行编译:

用法1:当指定的宏在程序中已定义,那么其中的语句序列参与源文件的编译,否则,其中其中的语句不参与源文件的编译;

用法2:当指定的宏在程序中已定义,那么其中的语句序列1参与源文件的编译,否则,其中其中的语句序列2参与源文件的编译;

5、行为语句的可综合性

不可综合的原因:https://blog.csdn.net/weixin_43274923/article/details/107506983

6、系统函数:

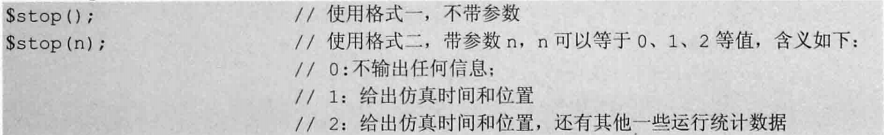

(1)$stop:当仿真程序执行到$stop时,将暂停仿真,此时设计者可以输入命令,对仿真器进行交互控制;

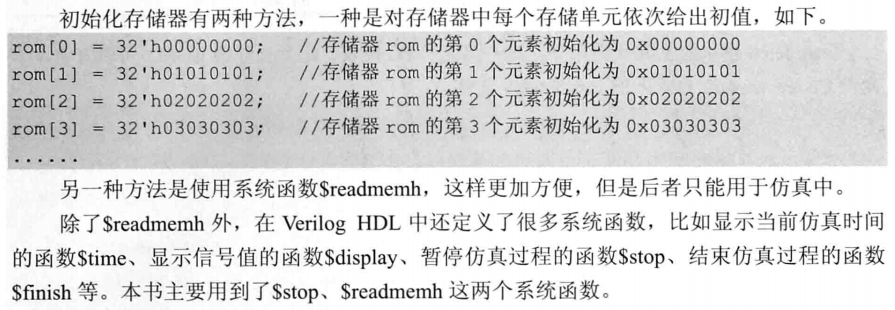

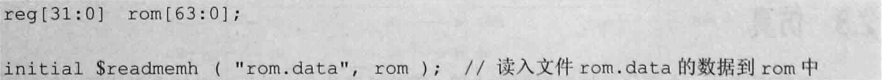

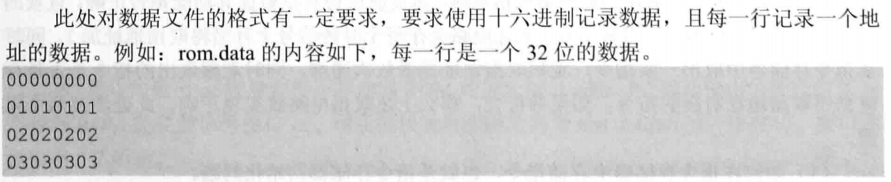

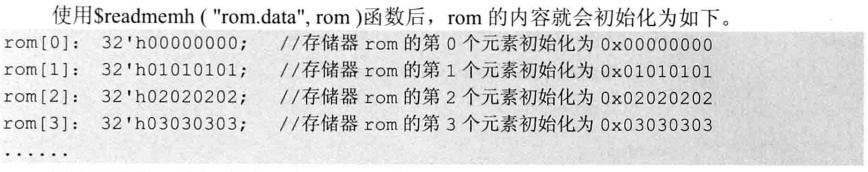

(2)$readmemh:用于从外部文件中读取数据并放入存储器中;

(PS:一个16进制数是4位,8个16进制数就是32位)

四、Test Bench

浙公网安备 33010602011771号

浙公网安备 33010602011771号