【翻译】基于Verilog设计的时序注意事项【Quartus II】【Digital Logic】

本指南讲述Altera的Quartus II软件如何处理基于Verilog硬件描述语言的设计里时序问题。讨论多种时序参数并解释如何指定时序约束。

目录

1 电路范例

2 时序分析报告

3 指定时序约束

4 时序仿真

Quartus II软件包含一个时序分析模块用来执行对在FPGA芯片里编译实现的电路的所有时序延迟的详细分析。本指南讨论执行的分析的种类和演示如何指定特殊的计时要求。讨论的前提是假设读者已经熟悉Quartus II的基本操作。

完成本指南,读者将学到:

- 定时分析器估计的参数

- 指定时序参数的期望值

- 使用时序仿真

本指南范例的时序结果有Quartus II 9.1版产生,其他版本同样可以使用。

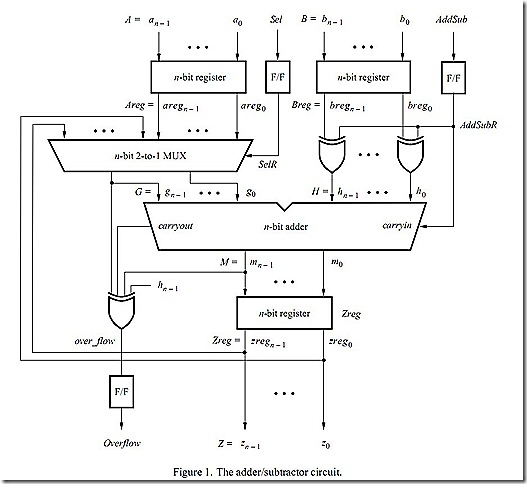

1 电路范例

在通过输入和输出寄存器穿过组合逻辑元件的长路径的电路里,时序问题很重要。我们将用图1所示的加/减电路作为范例。它可以加、减,并用2的补码表示计算n位的数。2个主要的输入是数A=a_n-1a_n-2...a_0和数B=b_n-1b_n-2...b_0,主要的输出是Z=z_n-1z_n-2...z_0.另一个输入是AddSub控制信号,当AddSub=0时Z=A+B,当AddSub=1时Z=A-B.第2个控制输入是Sel,用来选择计算器的操作模式。如果Sel=0,执行Z=A+-B,如果Sel=1,当前的Z的值将加上B或者减去B。如果加或减操作产生算术溢出,一个输出信号,Overflow将有效。

为使处理异步输入信号较容易,在时钟的上升沿它们将加载到触发器。因此,输入A和B将被加载到寄存器Areg和Breg,而Sel和AddSub将被加载到触发器SelR和AddSubR。加减电路将结果放到寄存器Zreg。

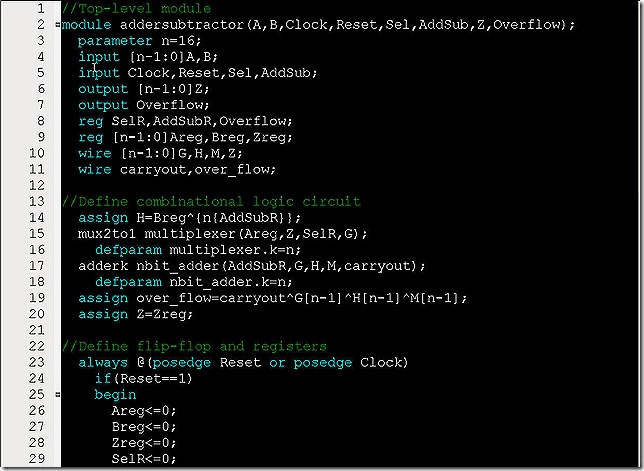

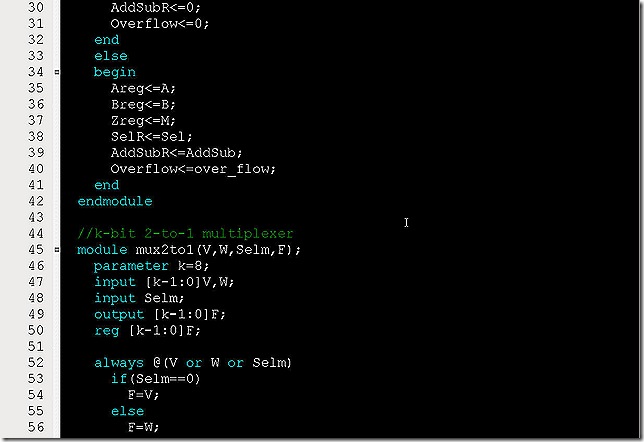

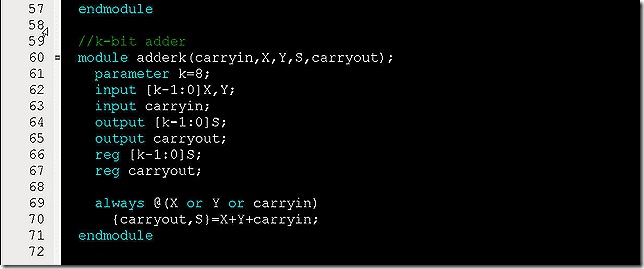

图2用Verilog代码描述了电路。在我们的例子里,指定n=16.按以下实现:

- 创建一个工程addersubtractor。

- 工程里包含图2所示代码的文件addersubtractor.v。为了方便,这个文件已经包含在DE2附带光盘的DE2_tutorial\design_files里,在Altera的DE2主页也可以找到。

- 选择DE2上的FPGA芯片,Cyclone II EP2c35F672C6。

- 编译这个设计。

2 时序分析报告

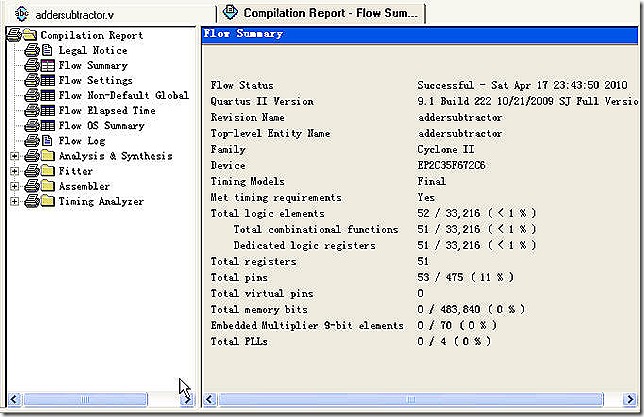

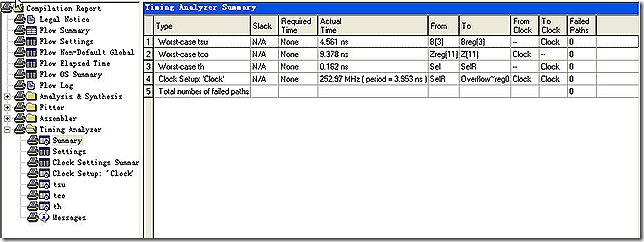

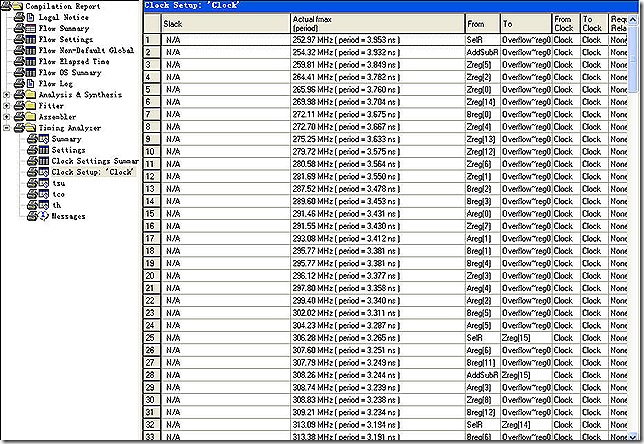

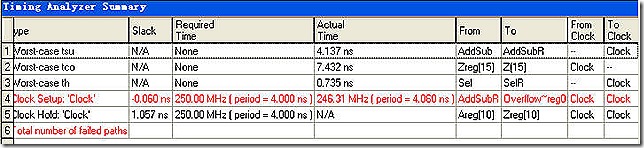

电路成功编译后生成的编译报告如图3所示。这个报告提供许多有用的信息。它显示了实现电路所需要的逻辑单元,触发器(寄存器)和引脚的数量。它给出了综合和适配模块产生的详细信息。也给出了实现的电路的速度。一个好的表示速度的方式是电路时钟的最大频率,记做fmax。这种测量依赖于同一时钟控制的两个寄存器之间的任意路径(关键路径)的最长延迟。Quartus II执行时序分析来测定电路预期的性能.在报告的时序分析区域,列出了几个估价的参数.单击时序分析器左边的+号展开这部分,然后点击Summary,如图4所示.表格的最后一行输入显示了我们完成的电路的最高频率是252.97MHz.依据你使用的Quartus II的版本,你可能得到不同的频率最大值.要查看电路里限制频率的路径,单击时序分析器的Clock Setup:'Clock'选项,如图5所示。这个表格显示了从触发器AddSubR到Overflow的实际路径。

图 3

图 4

图 5

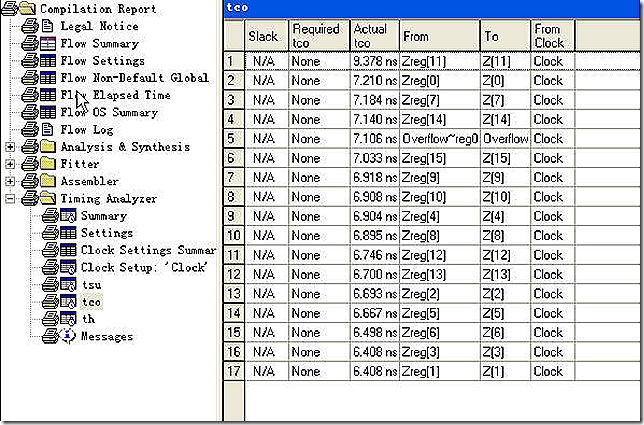

图4的表格也显示了其他时序结果。fmax作为电路里2个寄存器之间的最长时延,并没有在芯片的引脚的输出信号标出。从时钟源的时钟信号的有效沿到相应的输出引脚的输出信号的产生所消耗的时间叫做这个引脚的tco延迟。我们的电路里最坏的情况下,tco是9.378ns。单击时序分析器区域的tco,如图6所示,第一行显示从有效时钟沿到信号的传输从寄存器Zreg的位11到输出引脚z11花了9.378ns。图4中的其他两个参数是设置时间tsu和保持时间th。

图 6

3 指定时序约束

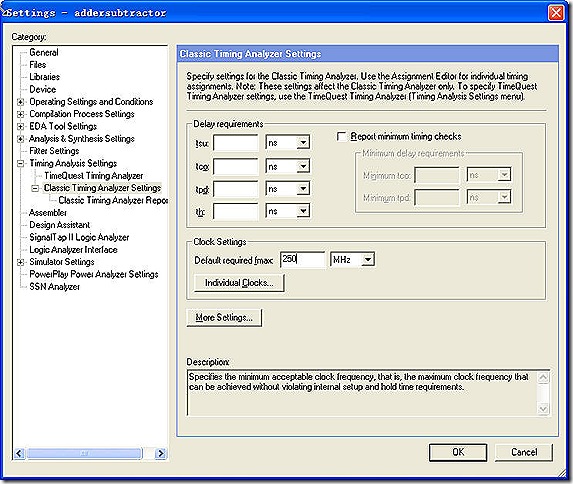

到这一步,我们已经在没有指示Quartus II要求的电路速度性能前提下编译了代码。在缺乏时序约束条件下Quartus ii为了保证快速编译可以很好的但不是最优实现电路。如果结果不符用户的期望,可以指点时序约束。例如,我们范例里的电路要在250MHz时钟下工作,而不是图4所示的fmax。可以按照以下实现设置fmax约束:

- 选择Assignments > Timing Settings 打开图7所示的Timing Requirements & Options窗口。在这个窗口可以指定不同的参数值。

- 在Clock栏指定fmax为250MHz,单击OK。

- 重新编译电路。

- 打开时序分析器的总结可以看到新的fmax,如图8所示。

图 7

图 8

如果指定的参数值太高,Quartus II会提示。

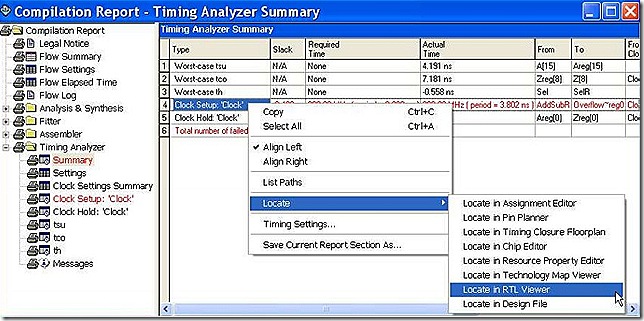

指定300MHz不能达到,因为电路的一条或多条长延迟。通过单击时钟设置输入高亮显示来查找最关键的路径。然后,右击,选择Locate > Locacet in RTL Viewer。注意从触发器AddSubR到Overflow的路径。

图 10

4 时序仿真

时序仿真形象的显示了延迟。

浙公网安备 33010602011771号

浙公网安备 33010602011771号