RAM/ROM IP一次性总结

1, 若需要修改memory mode, 需重新编译; 若不需要修改memory mode, 直接修改宏参数即可;

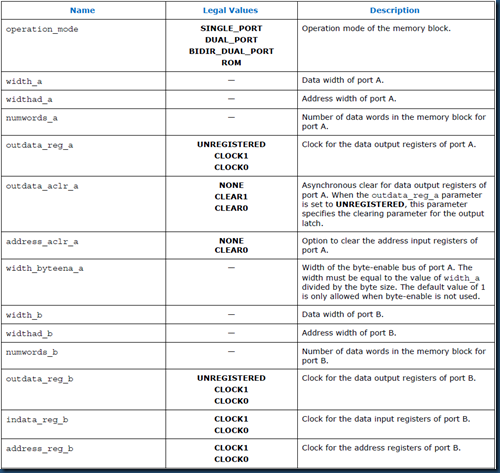

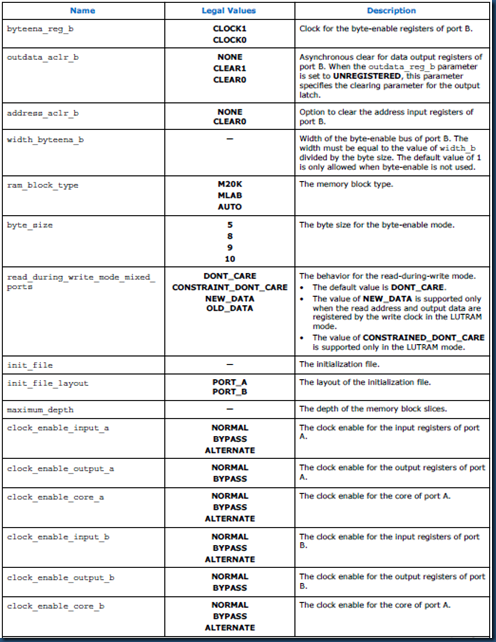

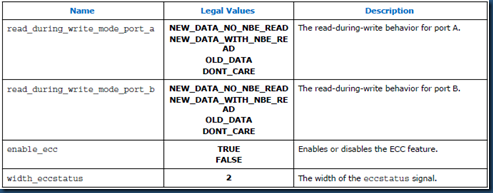

2, 宏参数列表:

3, 注意用LE搭memory的情况;

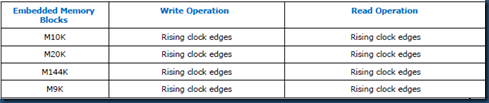

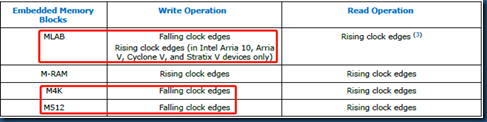

4, memory type与读写触发边沿(triggering)

注意,read/write triggering与地址/数据锁存是有区别的。

把triggering point理解为实际读/写发生的时间点,可以是上升沿或者下降沿;但地址/数据的锁存永远是在上升沿发生的。

5, 名词解释 -- continuous read

… when you write a data at the write clock rising edge and after the write operation is complete, you see the writtern data at the ourput port without the need for a read clock rsing edge.

MLAB ram supports continuous read.

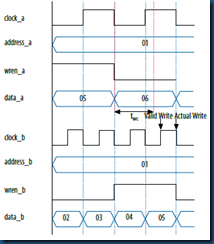

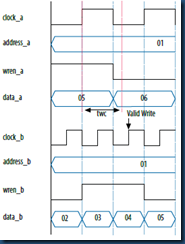

6, 名词解释 – write cycle time interval

tWC, write cycle time internal, 指对同一地址的两次成功写操作之间的最小时间间隔。假如在tWC之内对同一地址有多于一次写操作,那么写内容可能是未知的。

7, memory ram存储深度与功耗

(1) 首先要说明,RAM的存储深度一定需要是2的n次幂。会有些文档描述,指M9K最大的memory depth是8K;为什么9K的空间只有8K的深度呢?就是因为存储深度一定需要是2的n次幂。

(2) 依据memory type不同,相应的最大存储深度不一样

The maximum block depth setting 64 for MLAB is not available for Arria V and Cyclone V devices.

(3) 如(1)所述,M9K最密可以分割成8Kx1的存储格式。事实上,最小存储单位(多少bit)稍微大一点,整个Ram块的功耗会相对下降。但该规律不是一直线性的,边界在存储深度为256时。

When the RAM is sliced shallower, the dynamic power usage decreases. However, for a RAM block with a depth of 256, the power used by the extra LEs starts to outweigh the power gain achieved by shallower slices.

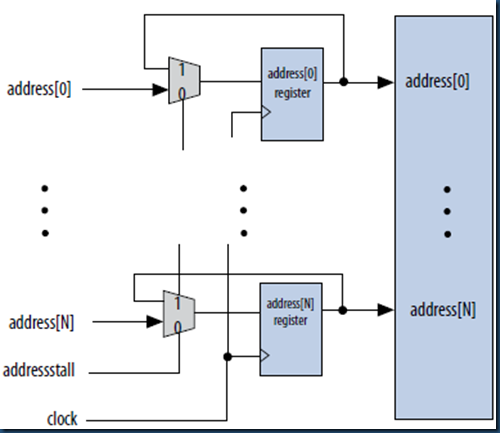

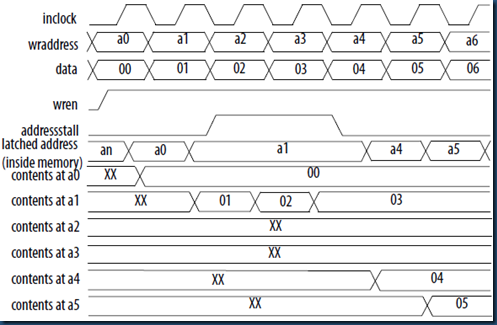

8, address enable以及读写时序

… address enable (…) holds the previous address value for as long as the signal is enabled (addressstall = 1), 即保持住地址值。

address enable的实现电路如下:

重点是下图描述外部信号到内部存储cell的数据流向。看完此图后理解RAM读写时序应该不会有任何困难。

9, byte enable

byte enable mask的是写操作。先确认1-bit的byte enable控制多少比特实际数据(size)、确保写入数据宽度与size是整数倍关系即可。

可选的size值有:5, 8, 9, 10。不同的RAM类型可用的值不同

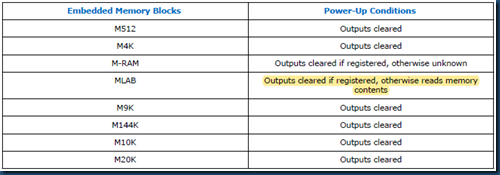

10, memory block上电时的初始值

只有MLAB可以灵活控制上电时的输出初值

11, freeze logic

用于重配置

posted on 2019-12-24 17:34 freshair_cn 阅读(1033) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号