IIC总线特性

定义

- Inter-Integerated circuit,飞利浦公司于1980年推出的串行通讯总线,使用多主从架构模型,同步半双工模式,一根时钟线,一根数据线进行通讯

主要特性

- 时钟线SCL、数据SDA,只是用两根线进行信息通讯

- 使用开漏结构进行引脚设计,可实现线与的特性

- 地址支持 7 bit和10 bit

- 支持多主机机制,通过冲突检测和仲裁机制实现

工作时序

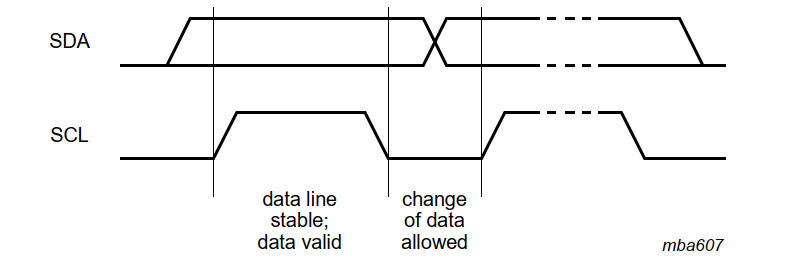

- data_valid:在SCL处于高位时进行SDA数据的截取(不同的厂家可能在同一时间段进行多次的截取,确认数据的准确性避免误码,以及判断是否存在主机竞争关系)。在SCL处于低位时,SDA数据进行切换

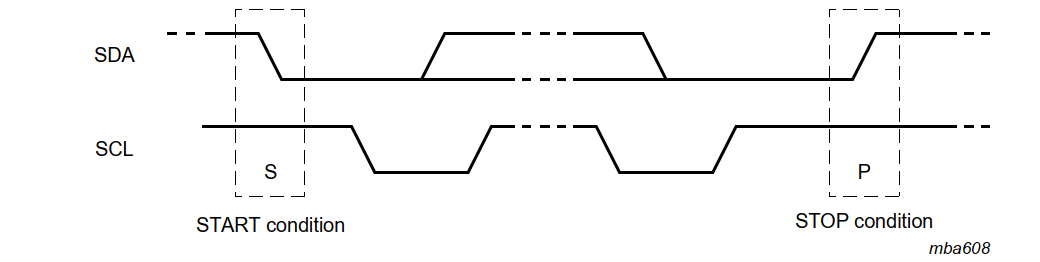

- start:由于开漏的特性,在设备不进行总线控制时,SDA和SCL均处于高电平。主机此时需要占据从总线进行传输,则拉低SDA电平,即在SCL处于高电平时进行SDA电平的转换,SDA由高电平到低电平的转换表示开始。repeat start则是指在不释放总线的情况重新发起,一般用于切换读写命令或者切换到其他从设备

- stop:当主机发送结束以后,若不会继续进行传输,则需要在SCL处于高电平时进行SDA由低电平到高电平的切换

此时细节的同学可以发现:整体数据SDA的电平主要发生在两块,前者是进行数据传输【scl低位->切换sda】,后者是进行传输启动或结束【scl高位->切换sda】

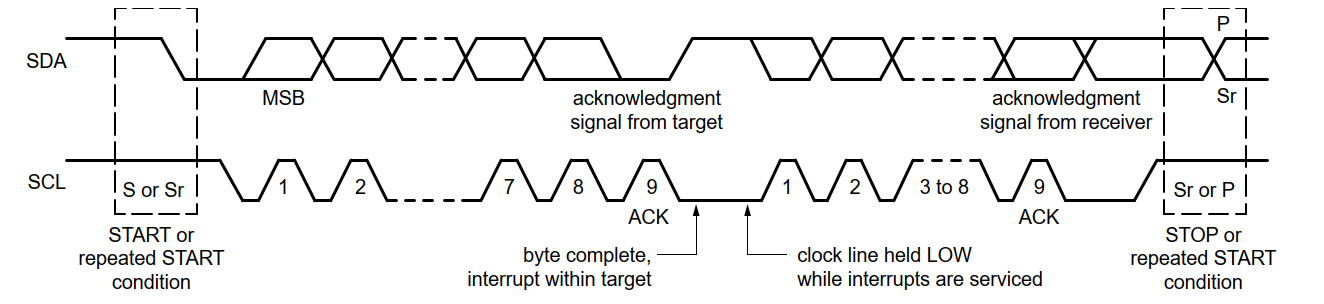

- format:发送以字节为单位,8bit,高位在前发送,完成后需要接受方在bit9 发送ack信号【低电平为ack,高电平为nack】

中断

- 中断的机制并不是iic总线的机制,而是由iic控制器向cpu发起的中断信号: 收发数据、总线状态切换、错误事件等

- 软件处理逻辑:iic控制器以及cpu配置中断使能,在触发中断后,iic控制器发送irq信号值中断控制器,中断控制器解析irq并发送中断信息至cpu,cpu获取信息后陷入中断,完成中断例程处理

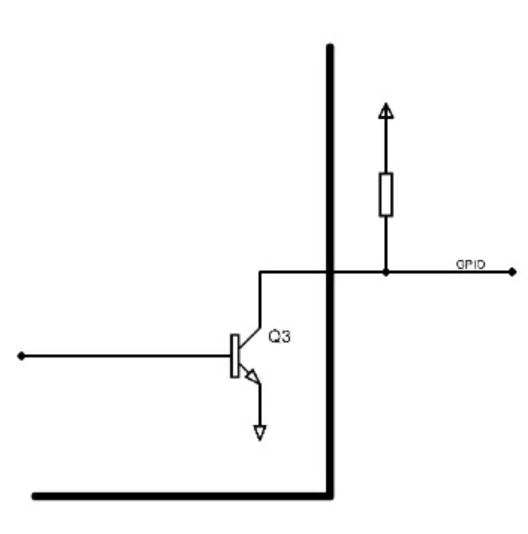

仲裁

- 电气特性:iic总线通过开漏结构并使用上拉电阻实现线与的特性【当多条信号线(如 SDA 或 SCL)通过上拉电阻连接到电源时,只要有任意一个设备将该信号线拉低,整条线就会保持低电平;只有当所有设备都释放该信号线(即输出高阻态)时,线才会在上拉电阻的作用下恢复高电平】

- 仲裁逻辑:通过iic设备对sda线进行高低电平的监控来实现,当多个主机发起数据传输时,该主机实时监控sda数据线的变化,若出现发送电平为高但是sda线上电平为低时,判定仲裁失败,释放总线

TIPS:当前本人从事IIC外设IP的验证工作,基于IIC进行部分功能验证,以及后续产品开发

验证记录

- 单主机通讯验证

- 主机收发数据与从机 - start,地址帧,数据帧,ack,nack,stop

- 从机通讯验证

- 地址识别功能,ack响应, 从机的时钟拉伸功能(保证处理完成从而拉低scl,延迟传输;主机端检测到scl被拉低后暂定通讯等候恢复)

使用记录

- 后续由于扩展iic设备的选路,使用了PCA9548和PCA9641,进行iic多路扩展

- 出现一次,从设备无法拉低进行ack的响应,后续硬件通过增加一颗电容解决

开漏结构

- 定义:输出级仅保留漏极(Drain)悬空的 MOS 管(通常为 N 沟道 MOSFET),无内部上拉电阻,源极(Source)接地,栅极(Gate)由内部逻辑控制,通常接一个上拉电阻表示1

- 可以实现线与的特性,即栅极控制高电平导通mos管,栅极接地,则整条线表现为0;若存在多组iic设备,整体电流路径也是由vcc-电阻-接地,没有风险

浙公网安备 33010602011771号

浙公网安备 33010602011771号