STM32F4 存储器和总线架构

总线矩阵

上图为stm32f4的总线矩阵,其中主控总线有8条,被控总线有7条,主设备和从设备通过各自的总线两两相交连接,图中两条总线相交且为圆圈的地方,表示这两条总线对应的主设备可以访问从设备,如I总线(指令总线),只有跟 M0、M2和M6这三根被控总线交叉的时候才有圆圈,就表示I总线只能跟这三根被控总线通信,这样就可以知道stm32f4的启动有三种分别是FLASH、内部SRAM、外部存储FSMC。

总线矩阵用于主控总线之间的访问仲裁管理,仲裁采用循环调度算法。有了总线矩阵,就可以让主设备和从设备进行并行访问,提升了访问效率,同时也降低了功耗。需要注意的是,虽然总线矩阵使得多个主设备可以并行访问不同的从设备,但在一个定义的时间段内,只有一个主设备拥有总线矩阵的控制权,如果有多个主设备同时出现总线请求时就得进行仲裁。所以有了总线仲裁器,就能保证每个时刻只有一个主设备通过总线矩阵对从设备进行访问。

注意并非所有主设备访问从设备都得经过总线矩阵,如上图中,有些主设备和从设备间有直通通道。

存储器映射

存储器本身不具有地址信息,给存储器分配地址的过程就称为存储器映射,尽管预定义的存储器映射的地址是固定的,但也具有很高的灵活性,允许芯片设计人员使用不同的内存和外设来设计他们的产品,以实现更好的产品差异化。给某个地址再分配一个地址的过程叫存储器重映射,但是Cortex M4芯片没有MMU所以并不支持。如上所示,就是stm32f4xx的部分通过存储器映射的寄存器地址,详见《STM32F4xx中文参考手册》的P52~P54页。

上图为预定义的存储器映射图,来自 Cortex M3与M4权威指南中的第六章第三节。在4GB的可寻址内存空间中,一些部分被分配给内部外设,如NVIC和调试组件。这些内部外设的地址是固定的。此外,内存空间在结构上被划分为若干内存区域,对应上图:

Code:只读段,用于保存默认的向量表;

SRAM:连接SRAM,主要是片内SRAM,但没有确切的内存类型限制。SRAM区域的前1MB是位可寻址的,如果可选位带特性包括在内。还可以从该区域执行程序代码;

Peripherals:主要用于片内外设。由芯片公司进行定义的一些寄存器地址,如GPIO寄存器地址、USART和I2C的寄存器地址等等;

RAM:变量存储区,如果开发板从片内的Flash启动,就需要指定RAM,不过一般只要选好了器件型号,keil5就自动选好了;

Devices:主要是用于给片外的设备分配地址;

System:内核定义的一些寄存器,包含了:NVIC,MPU, SysTick,SCB,FPU,FPB,DWT等。

GPIO的位带操作

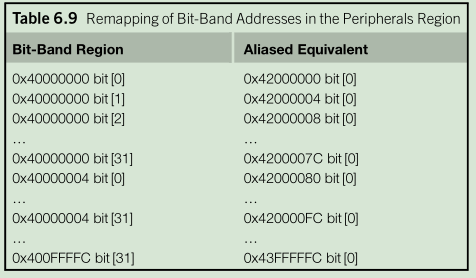

在预定义的存储器映射图有两个位带区,分别对应了两个位带别名,其实也就是将位带区每个的比特位一个一个按顺序取出来,将其映射成32位4字节的寄存器,这样位带别名的大小应该是位带区的32倍,事实也是这样。

查看stm32f4xx的芯片手册可以发现GPIO的寄存器地址属于Peripherals的位带区,所以可以进行位带操作,使用位带操作可以大大提高程序的运行速率和提升安全性,操作IO口的性能将达到极致,而不必要去调用GPIO_SetBits、GPIO_ResetBits、GPIO_WriteBit等GPIO操作的库函数,调用函数要进行入栈出栈等操作,会占用时间。

上图为位带区转换为位带别名区的宏定义代码,以GPIOE端口的第n根引脚为例,进行了输出高低电平的操作,只要预先初始化好了GPIOE端口第n根引脚,就可以使用这个宏定义,让第n根引脚输出高低电平,如:

PEout(13) = 0;//让GPIOE的第13根引脚输出低电平

PEout(13) = 1;//让GPIOE的第13根引脚输出高电平

总结

1.总线矩阵很重要,不可忽略;

2.了解了存储器映射便能大概知道内核的结构;

3.位带操作可以提高速率和提升安全性,能使用就尽量使用,I/O初始化就不必要,因为这样的话代码会很多,直接使用库函数初始化就可以。

相关下载

链接:https://pan.baidu.com/s/10gTR5-5cFMnb9XZZmtxjsQ

提取码:nfsj

复制这段内容后打开百度网盘手机App,操作更方便哦

浙公网安备 33010602011771号

浙公网安备 33010602011771号