摘要:

-

没有声明类型的变量,默认是wire类型,即线型。

-

使用assign连续赋值,或者使用实例元件,进行硬件描述。

-

Vector part select

-

Vectorgates

-

Gates4

------------------------------------------------------------------------------------------------

- Vector part select

module top_module( input [31:0] in, output [31:0] out );// assign {out[7:0],out[15:8],out[23:16],out[31:24]}=in; endmodule

-

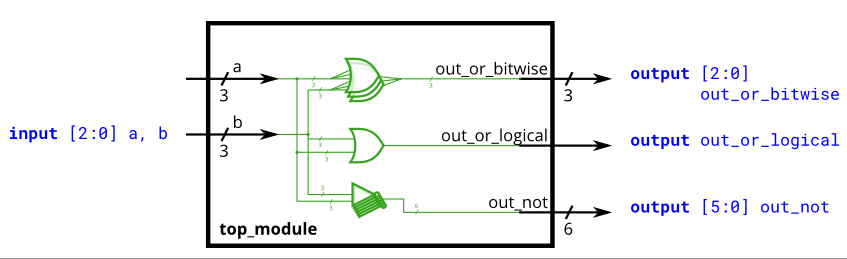

Vectorgates

module top_module( input [2:0] a, input [2:0] b, output [2:0] out_or_bitwise, output out_or_logical, output [5:0] out_not ); assign out_or_bitwise[2:0]= {a[2]|b[2],a[1]|b[1],a[0]|b[0]}; assign out_or_logical=a[2:0]||b[2:0]; assign out_not[5:0]={!b[2],!b[1],!b[0],!a[2],!a[1],!a[0]};

//等号右边,各个位进行按位操作,然后用利用{}拼接成vector

//左边这些变量旁边的[],也可以省去不写,效果是一样的

endmodule

这么写更简洁一点:

assign out_or_bitwise= a|b;

assign out_or_logical=a||b;

assign out_not={~b,~a};

-

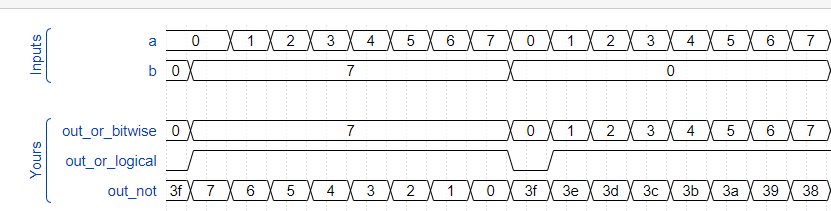

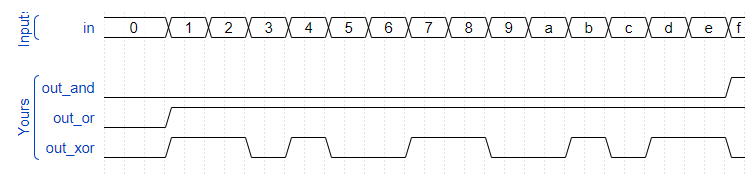

Gates4

module top_module( input [3:0] in, output out_and, output out_or, output out_xor ); assign out_and=in[3]&in[2]&in[1]&in[0]; //检查4位输入是否同时置1 assign out_or=in[3]|in[2]|in[1]|in[0]; //检查4位输入是否有一个1,即是否有任何信号 assign out_xor=in[3]^in[2]^in[1]^in[0]; //这个的实际含义不太清楚 endmodule

-----进度有点慢,明天多弄点------20210728--------

![]()

module top_module ( input [4:0] a, b, c, d, e, f, output [7:0] w, x, y, z );//\ assign w = {a,b[4:2]}; assign x = {b[1:0],c,d[4]}; assign y = {d[3:0],e[4:1]}; assign z = {e[0],f,2'b11}; //注意,这里常量是上逗号',而不是键盘左上角的这个` // assign { ... } = { ... }; endmodule

module top_module (

input [7:0] in,

output [31:0] out );//

// assign out = { replicate-sign-bit , the-input };

assign out={{24{in[7]}},in}; //注意里面24个复制之后,要再用{}把这24个拼接起来。

endmodule

![]()

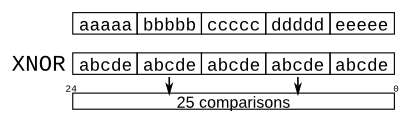

module top_module ( input a, b, c, d, e, output [24:0] out );// assign out = ~{{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}} ^ {{5{a,b,c,d,e}}}; // The output is XNOR of two vectors created by // concatenating and replicating the five inputs. // assign out = ~{ ... } ^ { ... }; endmodule

《

https://hdlbits.01xz.net/wiki/Vector2

》

浙公网安备 33010602011771号

浙公网安备 33010602011771号