UFS笔记

转载自:https://zhuanlan.zhihu.com/p/514645324?utm_id=0

eMMC

eMMC(embeddedMultiMediaCard)是由MMC协会针对手机平板制定的闪存标准,起源时间较UFS与NVMe还要更早。 eMMC基础上由MMC储存卡发展而来,采用并行传输技术制成,读写必须分开执行,虽然仅提供单路读写功能,但仍具备体积小、高度集成与低复杂度的优势。

目前最新的eMMC5.1标准,连续读取速度约为250MB/s

UFS

第一代UFS由于与当时eMMC标准速度差异不大,且成本较为高昂,因此并未成功普及,直至2014年UFS2.0标准问世后,连续读取速度约达800MB/s,UFS至此逐渐成为Android旗舰都会采用的标准配置。

到了2018年UFS3.0问世,连续读取速度约为1700MB/s,逐渐赶超苹果NVMe。目前2022年UFS4.0发布,连续读写速度已经可以做到3400MB/s。

2023年发布的Android旗舰基本上都采用了UFS4.0这一规格的闪存,Android手机上eMMC、UFS的区别,基本上可以理解成PC上的HDD机械硬盘和SSD固态硬盘的区别。

NVMe

NVMe(NVMExpress)原先是用在MacBook上的SSD固态硬盘的闪存标准,具备高效率、低负载、低延时的特性。 2015年,苹果首次在iPhone6S上使用NVMe闪存,当时的连续读取速度约为500MB/s。

由于早期Android手机大多使用的是eMMC5.1标准,因此在连续读取速度方面,iPhone一骑绝尘,这也是「iPhone用着不卡,一部手机可以用3-5年的最大原因。

另外能使用NVMe闪存,跟苹果A9芯片开始用PCIE接口有关,后续苹果家的WiFi、基带都使用PCIE接口,自己家的芯片接口自己定义,其他厂商真的学不来。

直至UFS3.0问世后两者差距才逐渐缩小,这几年的苹果的NVMe也在升级,,从iPhone6S以来将近翻了4倍。目前最新的iPhone14ProMax连续读写性能在1,500MB/s左右。 所以在连续读写性能这块:UFS4.0>NVMe=UFS3.1>UFS2.1>eMMC5.1

/********************************************************** NAND Flash *****************************************************************/

一、NAND Flash

NAND Flash全名为Flash Memory,属于非易失性存储设备(Non-volatile Memory Device),基于浮栅(Floating Gate)晶体管设计,通过浮栅来锁存电荷,由于浮栅是电隔离的,所以即使在去除电压之后,到达栅极的电子也会被捕获。这就是闪存非易失性的原理所在。数据存储在这类设备中,即使断电也不会丢失。

根据不同的纳米技术,NAND Flash已经历了从SLC向MLC,再向TLC的过渡,正在向QLC迈进。NAND Flash凭借容量大、写入速度快等特点,广泛应用于eMMC/eMCP,U盘,SSD、汽车、物联网等领域。

SLC(英文全称(Single-Level Cell——SLC)即单层式储存

SLC技术特点是在浮置闸极与源极之中的氧化薄膜更薄,在写入数据时通过对浮置闸极的电荷加电压,然后透过源极,即可将所储存的电荷消除,通过这样的方式,便可储存1个信息单元,即1bit/cell,速度快寿命最长,价格贵(约MLC 3倍以上的价格),约10万次擦写寿命。

MLC(英文全称Multi-Level Cell——MLC)即多层式储存

英特尔(Intel)在1997年9月最先开发成功MLC,其作用是将两个单位的信息存入一个Floating Gate(闪存存储单元中存放电荷的部分),然后利用不同电位(Level)的电荷,通过内存储存的电压控制精准读写。

即2bit/cell,速度一般寿命一般,价格一般,约3000---1万次擦写寿命。MLC通过使用大量的电压等级,每个单元储存两位数据,数据密度比较大,可以一次储存4个以上的值,因此,MLC架构可以有比较好的储存密度。

TLC(英文全称Trinary-Level Cell)即三层式储存

TLC即3bit per cell,每个单元可以存放比MLC多1/2的数据,共八个充电值,即3bit/cell,也有Flash厂家叫8LC,所需访问时间更长,因此传输速度更慢。

TLC优势价格便宜,每百万字节生产成本是最低的,价格便宜,但是寿命短,只有约1000次擦写寿命。

QLC(英文全称Quadruple-Level Cell)四层存储单元

全称是Quad-Level Cell,四层式存储单元,即4bits/cell。QLC闪存颗粒拥有比TLC更高的存储密度,同时成本上相比TLC更低,优势就是可以将容量做的更大,成本压缩得更低,劣势就是寿命更短,理论擦写次数仅150次。

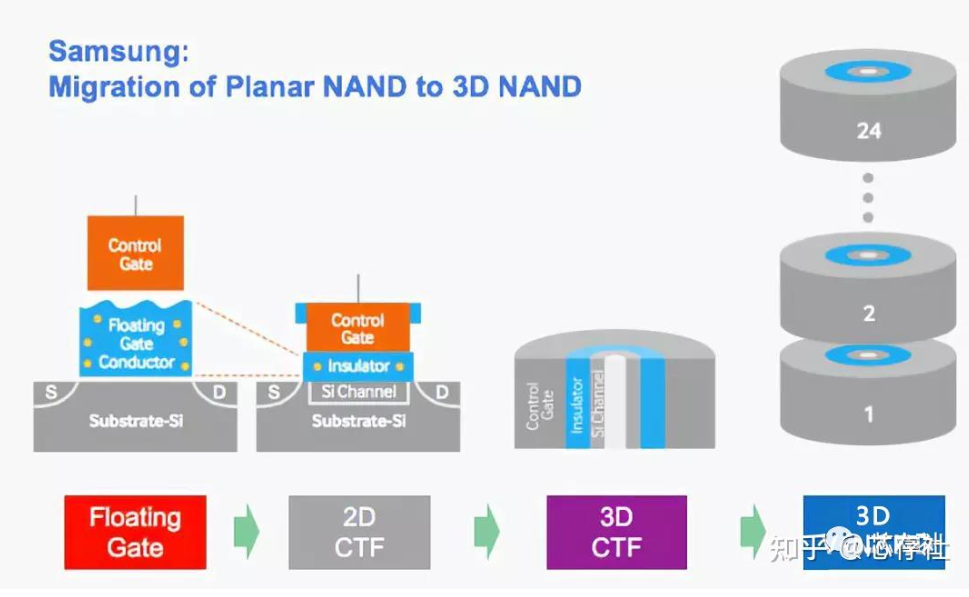

而NAND闪存根据对应不同的空间结构来看,这四类技术可又分为2D结构和3D结构两大类,浮栅晶体管是主要用于2D FLASH,3D flash主要采用的是CT晶体管,浮栅是半导体,CT是绝缘体,二者在本质和原理上就有区别。其区别在于:

2D结构NAND Flash

2D结构的存储单元仅布置在芯片的XY平面中,因而使用2D闪存技术在同一晶圆中实现更高密度的唯一方法就是缩小制程工艺节点。

其缺点是,对于较小的节点,NAND闪存中的错误更为频繁;另外,可以使用的最小制程工艺节点存在限制,存储密度不高。

3D结构NAND Flash

为了提高存储密度,制造商开发了3D NAND或V-NAND(垂直NAND)技术,该技术将Z平面中的存储单元堆叠在同一晶圆上。

在3D NAND闪存中,存储器单元作为垂直串连接而不是2D NAND中的水平串,以这种方式构建有助于为相同的芯片区域实现高位密度。第一批3D Flash产品有24层。

Nand Flash的加工过程

硅材料 -> 晶圆(Wafer) -> NAND FLSH 芯片(晶片)

NAND Flash是从原始的硅材料加工出来的,硅材料被加工成晶圆(Wafer),一般分为6英寸、8英寸、12英寸规格不等,晶片就是基于这个wafer上生产出来的,一片晶圆可以切割出多少晶片是根据die的大小和wafer的大小以及良率来决定的,通常情况下,一片晶圆上可以做出几百颗NAND FLASH芯片。

芯片未封装前的晶粒成为Die,它是从Wafer上用激光切割而成的小片,每个Die就是一个独立的功能芯片,它由无数个晶体管电路组成,但最终可被作为一个单位封装起来成为闪存颗粒芯片。

晶片在光刻了电路后,称之为wafer

一片载有NAND Flash晶圆的wafer,wafer首先经过切割,然后测试,测试通过后,再进行切割、封装,封装完成后会再次进行一道检测。将完好的、稳定的、足容量的die取下,封装形成日常所见的Nand 。

合格的Flash Die原厂封装工厂会根据需要封装成eMMC、TSOP、BGA、LGA等产品

/********************************************* eMMC UFS ***************************************************************/

二、eMMC、UFS

eMMC ( Embedded Multi Media Card) 采用统一的MMC标准接口, 把高密度NAND Flash以及MMC Controller封装在一颗BGA芯片中。针对Flash的特性,产品内部已经包含了Flash管理技术,包括错误探测和纠正,flash平均擦写,坏块管理,掉电保护等技术。用户无需担心产品内部flash晶圆制程和工艺的变化。同时eMMC单颗芯片为主板内部节省更多的空间。

简单地说,eMMC=Nand Flash+控制器+标准封装

新一代UFS

UFS:Univeral Flash Storage,我们可以将它视为eMMC的进阶版,是由多个闪存芯片、主控、缓存组成的阵列式存储模块。UFS弥补了eMMC仅支持半双工运行(读写必须分开执行)的缺陷,可以实现全双工运行,所以性能得以翻番。

/*************************************************************************************************************************/

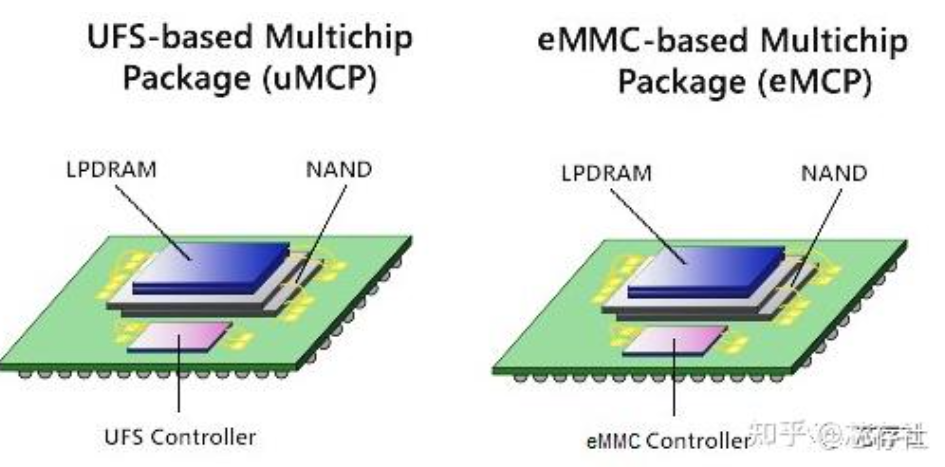

三、eMCP 与uMCP

eMCP是结合eMMC和LPDDR封装而成的智慧型手机记忆体标准,与传统的MCP相较之下,eMCP因为有内建的NAND Flash控制晶片,可以减少主晶片运算的负担,并且管理更大容量的快闪记忆体。以外型设计来看,不论是eMCP或是eMMC内嵌式记忆体设计概念,都是为了让智慧型手机的外型厚度更薄,更省空间。uMCP是结合了UFS和LPDDR封装而成的智慧型手机记忆体标准,与eMCP相比,国产的uMCP在性能上更为突出,提供了更高的性能和功率节省。

uMCP是顺应UFS发展的趋势,满足5G手机需求

eMCP=eMMC+LPDDR+标准封装

uMCP=UFS+LPDDR

/*************************************************************************************************************************/

四、DDR、LPDDR

DDR全称Double Data Rate双倍速率同步动态随机存储器,严格的来讲,DDR应该叫DDR SDRAM。虽然美国固态技术协会2018年宣布正式发布DDR5标准,但实际上最终的规范要到2020年才能完成,其目标是将内存带宽在DDR4基础上翻倍,速率3200MT/s起,最高可达6400MT/s,电压则从1.2V降至1.1V,功耗减少30%。

LPDDR是在DDR的基础上多了LP(Low Power)前缀,全称是Low Power Double Data Rate SDRAM,简称“低功耗内存”是DDR的一种,以低功耗和小体积著称。目前最新的标准LPDDR5被称为5G时代的标配,但目前市场上的主流依然是LPDDR3/4X。

电子产品的进步总结下来一定是体积更小,性能更强,功耗更低。当然内存也不例外,无论是LPDDR内存还是DDR内存,或许有一天能通过极低的功耗,实现更高的性能。

浙公网安备 33010602011771号

浙公网安备 33010602011771号