从电路的角度看功耗

本文将从分两部分进行讲解,第一部分为CMOS晶体管的基础知识,第二部分详细阐述了电路中功耗组成。

CMOS Transistors

最早期的电子计算机使用继电器或电子管实现二值系统,而现代计算机中则采用晶体管来实现二值系统。晶体管可以根据控制端电压或者电流的变化来实现“开启”或者“关闭”的功能,从而表达二进制。晶体管主要分为双极性晶体管(Bipolar Junction Transistor)和金属-氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor, MOSFET or MOS),当前绝大多数CPU都采用MOS晶体管实现,其中又以CMOS(Complementary Metal Oxide Semiconductor)晶体管电路设计最为常见。

Semiconductor

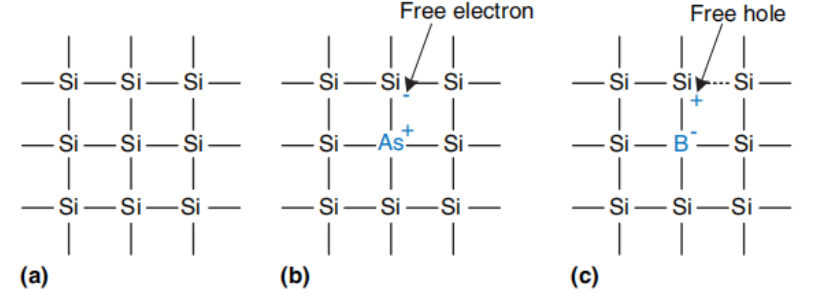

MOS晶体管使用硅作为基本材料,在元素周期表中,硅是IV族元素,他的原子最外层有4个电子,可以与相邻的4个硅原子的最外层电子配对成为共价键,通过与相邻原子形成的共价键,纯净硅中所有原子的最外层都具有8个电子,达到相对稳定,所以纯净硅的导电性很弱。

但是如果在纯净硅中掺杂少量的5价原子(如磷As),这些原子将挤占原有硅原子的位置,由于这些原子的最外层有5个电子,除了与原有的硅原子形成共价键用掉四个电子外,还多余一个处于游离状态的电子。在电场的作用下,处于游离状态的电子会逆着电场的方向流动,形成负电流,这类材料被称为n-type材料。

同样如果在纯净的硅中掺杂少量的3价原子(如硼B),这些原子挤占原有硅原子的位置后,其最外层还缺少一个电子和相邻的硅原子形成共价键,形成空穴(hole),在电场的作用下,周围的电子就会跑来填补这个空穴,从而留下一个新的空穴,相当于空穴也在顺着电场的方向流动,形成正电流,这类材料被称为P-type材料。

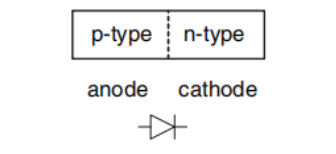

Diodes

p-type类型的硅和n-type类型的硅连接起来形成二极管(Diodes),p-type区域称为阳极,n-type区域称为阴极,当阳极电压大于阴极电压,电流从阳极流向阴极,反之阳极电压小于阴极电压,电流无法通过。

nMOS and pMOS Transistors

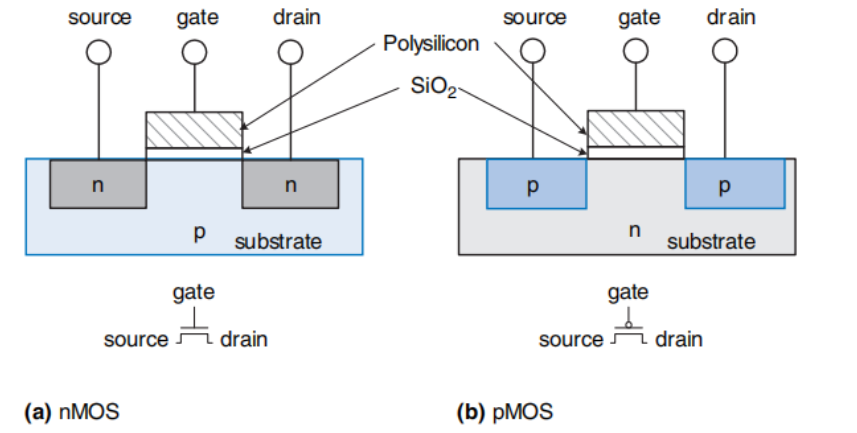

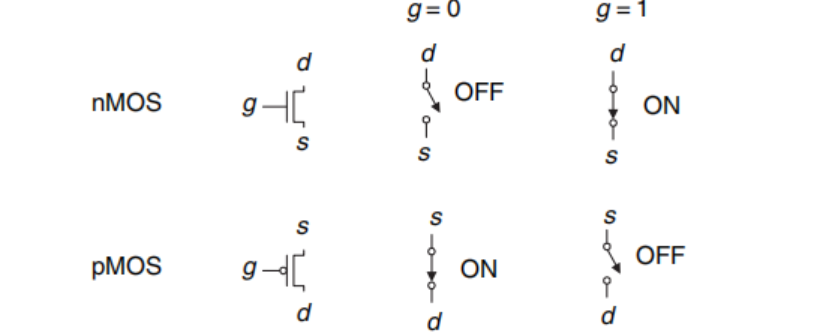

MOS晶体管是由多层摞放在一起的导电和绝缘材料构建起来的,每个晶体管的底部叫做衬底,是低浓度掺杂的半导体硅。晶体管上部接出来3个信号端口,分别称为源极(Source)、漏极(Drain)和栅极(Gate)。栅极和漏极叫做有源区,该区域采用与衬底相反极性的高浓度掺杂。衬底是低浓度P型掺杂,有源区是高浓度N型掺杂的MOS晶体管叫做nMOS晶体管;衬底是低浓度N型掺杂,有源区是高浓度P型掺杂的MOS晶体管叫做pMOS晶体管。

无论是nMOS管还是pMOS管,其栅极和衬底之间都存在一层绝缘体,叫做栅氧层,其成分通常是二氧化硅(silicon dioxide,SiO2)。最早期的MOS晶体管栅极由金属制成,这也是metal-oxide-semiconductor名字的由来,现在大多数的栅极采用掺杂后的多晶硅(Polysilicon)制成。掺杂后的多晶硅尽管其电阻比金属大,但却比半导体硅的电阻小很多,可以用作电极。并且同普通金属相比,多晶硅更耐受高温,不至于在MOS晶体管生产过程中融化。

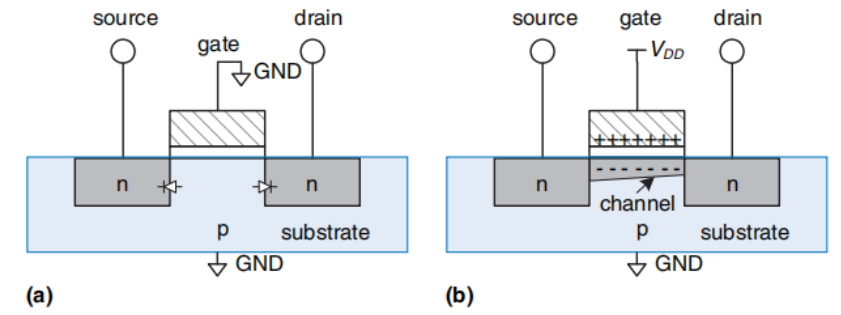

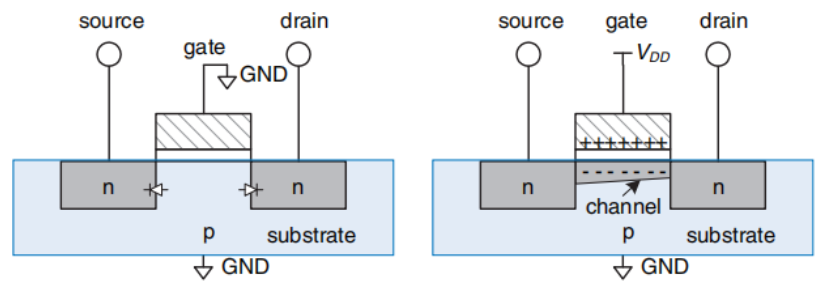

我们以nMOS晶体管为例,介绍晶体管如何工作

通常nMOS晶体管的衬底接地,如果单纯在源极、漏极之间加上电压,两极之间是不会有电流流过的,因为源极和漏极之间相当于有一对正反相对的PN结,如果在栅极上加上电压,因为栅氧层是绝缘的,就会在P衬底里形成一个电场。栅极上的正电压会把P衬底里面的电子吸引到栅氧层的地步,形成一个很薄的沟道电子层,相当于在源极和漏极之间架起了一座导电的桥梁,此时再在源极漏极之间加上电压,那么两极之间的电流就能流过来了。

pMOS正好相反,其衬底连接正电压,当栅极不加电时,晶体管导通,栅极加电时,晶体管断开。

随着工艺的发展,MOS晶体管中的栅氧层的厚度越来越薄,使得开启所需要的门电压不断降低,从早期工艺的5V,降低到后来的2.5V、1.8V,现在都是1V左右或者更低。

不幸的是,MOS晶体管不是理想的开关,nMOS晶体管适合传输0而不适合传输1,pMOS晶体管适合传输1而不适合传输0。因此需要同时使用两种类型的晶体管,令他们传输自己的擅长的,这种处理过程称为Complementary MOS or CMOS。

Common CMOS Gate

下面举两个简单的例子来说明如何用cMOS晶体管来构造电路中的基本单元—门。

-

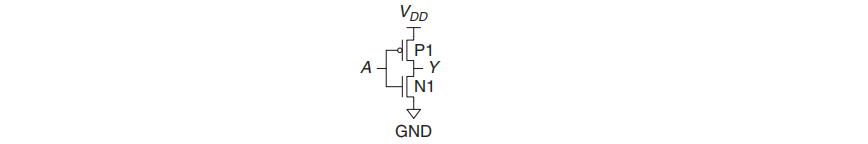

CMOS NOT Gate

当A为1,上面的pMOS晶体管断开,下面的nMOS晶体管导通,Y = 0

当A为0,上面的pMOS晶体管导通,下面的pMOS晶体管断开,Y = 1

-

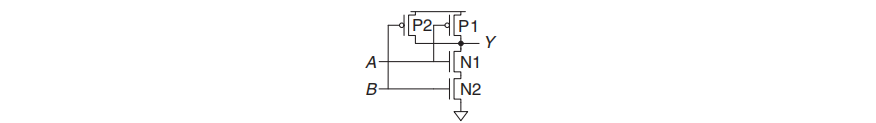

CMOS NAND Gate

通过并联的pMOS晶体管和串联的nMOS晶体管形成与非门,需要注意的是,当输入即扇入系数过多时,串联的nMOS会导致过大的延迟,因此通常扇入系数最多为4或5。

Power and Energy Consumption

功耗通常分为两部分:

$$

P = P_{static} + P_{dynamic}

$$

-

Dynamic Power

电信号在0和1之间变换时电容的充放电。

$$

P_{dynamic} = α * C_L * V^2_{DD} * f + I_{sc} * V_{DD}

$$

$C_L$为电路中的电容大小,$f$为时钟频率,$α$为晶体管翻转的概率,$I_{SC}$ 为短路电流,$V_{DD}$ 为供电电压(Supply voltage)。短路电流发生的原因为电信号在0和1之间变化时,NMOS和PMOS晶体管同时导通,此时从$V_{DD}$到$GND$之间出现短路,通常短路电流功耗占功耗的一小部分,我们不做考虑。 -

Static Power

电信号不发生变化时的功耗(电流泄露)

$$

P_{static} = V_{DD} * I_{D}

$$

$I_{D}$被称为泄露电流(从$V_{DD}$到GND)

Static Power

重新回顾一下晶体管导通时的情况,当Gate端电压达到一定值时,substrate上形成一个channel,此时电子可以流通,此时晶体管处于导通状态。我们将source和drain导通所需要的电压,我们记为$V_{TH}$,Gate端电压记为$V_{GS}$。

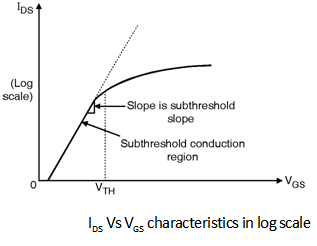

当$V_{GS} < V_{TH}$时,理想状态下,source端和drain端无电流流动,但实际上,两端之间仍存在电流流通,我们称该电流为subthreshold current,记为$I_{D}$,泄露电流随着gate端电压增长指数级增长。

$$

I_{\text{D}}\approx I_{\text{D0}}e^{\frac {V_{\text{GS}}-V_{\text{TH}}}{nV_{\text{T}}}}

$$

$I_{D0}$为当$V_{GS} = V_{TH}$时的电流,$V_{T} = kT/q$为热电压(thermal voltage),我们需要关心的是泄露电流随着门限电压的降低指数级增长,因此门限电压不能无限制的降低,这也限制了供电电压的降低。

上图刻画了$I_{D}$和$V_{GS}$的关系(两边同时取log),通常一个好的电路,其Slope越大越好。

补充一个概念:thermal runaway,由于泄露电流会导致温度提升,造成热电压的升高,此时泄露电流继续增大,形成恶性循环,这种循环成为thermal runaway。因此经常说温度是集成电路的第一杀手[^3]。

Dynamic Power

不考虑短路功耗,则动态功耗由下式表示:

$$

P_{dynamic} = α * C_L * V^2_{DD} * f

$$

动态功耗通常在功耗中占比很高,是我们研究的重中之重。我们先来简要说一下频率和供电电压的关系,这对我们后续理解大有帮助。

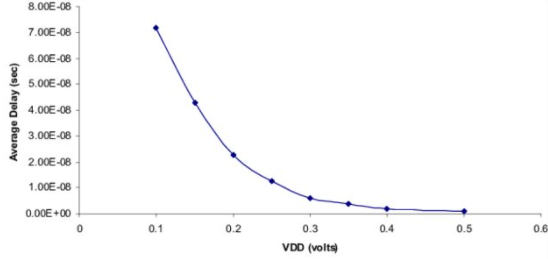

频率$f$可以视为电路中关键路径延迟的倒数,即$f = 1 / Delay $

而延迟通常由路径中电容的充放电决定,延迟和供电电压关系可以由下式给出[^5]

$$

Delay = C_L * V_{DD} / I = (C_L * V_{DD}) / (uC_{ox}(W / L)(V_{DD} - V_{TH})^2)

$$

可以看出延迟和供电电压成反比

最终,我们将式子简化为

$$

f \propto (V_{DD} - V_{TH})^2 / V_{DD}

$$

因此频率可以看作电压的线性函数,最大频率随着供电电压的增加线性增加,所以动态功耗近似正比于供电电压的三次方($P_{dynamic} \propto V^3$),因此在动态功耗为主的CPU中,通过动态降低电压实现功耗降低带来了很大的受益,但需要注意的是,降低$V_{DD}$也通常也意味着$f$的降低,会造成任务执行时间的增加,因此需要在performance和energy之间做出权衡,通常对于已知deadline time的任务,通过降低供电电压且保证任务在期限前完成可以造成功耗大幅度下降。

Reference

[1] 《Digital Design and Computer Architecture》

[2] 《Embedded Computing for High Performance》

[3] 《计算机体系结构基础(第二版)》 胡伟武著

[4] T. D. Burd and R. W. Brodersen, "Energy efficient CMOS microprocessor design," Proceedings of the Twenty-Eighth Annual Hawaii International Conference on System Sciences, 1995, pp. 288-297 vol.1, doi: 10.1109/HICSS.1995.375385.

[5] A. P. Chandrakasan, S. Sheng and R. W. Brodersen, "Low-power CMOS digital design," in IEEE Journal of Solid-State Circuits, vol. 27, no. 4, pp. 473-484, April 1992, doi: 10.1109/4.126534.

[6] T. Mudge, "Power: a first-class architectural design constraint," in Computer, vol. 34, no. 4, pp. 52-58, April 2001, doi: 10.1109/2.917539.

浙公网安备 33010602011771号

浙公网安备 33010602011771号