会员

周边

新闻

博问

闪存

众包

赞助商

Chat2DB

所有博客

当前博客

我的博客

我的园子

账号设置

会员中心

简洁模式

...

退出登录

注册

登录

神的随波逐流的中子

博客园

首页

新随笔

联系

订阅

管理

上一页

1

2

3

4

5

6

7

下一页

2021年2月18日

FPGA——OV5640摄像头初始化实现及仿真

摘要: 一、设计思路 1、步骤 摄像头有一个上电复位信号(低有效) 摄像头在系统复位之后,摄像头上电复位信号要保持稳定的低电平至少1ms 1ms之后之后,拉高上电复位信号 拉高上电复位信号后20ms之后,摄像头才能进入工作模式 进入工作模式之后,通过SCCB将初始化的参数写入摄像头寄存器内 摄像头初始化完成

阅读全文

posted @ 2021-02-18 15:47 AdriftCore芯研社

阅读(2323)

评论(0)

推荐(0)

2021年2月17日

FPGA——从IIC到SCCB状态机实现

摘要: 一、SCCB协议注意事项 1、读时序 2阶段写紧跟着一个2阶段读,意思是读时序有一个完整的2阶段写以及一个完整的2阶段读 所以,读时序是有两个完整阶段的,2阶段写有起始位停止位,2阶段读也有起始位和停止位 2、IIC协议与SCCB协议 IIC协议与SCCB协议的写时序是完全相同的,而读时序通过以上的

阅读全文

posted @ 2021-02-17 19:29 AdriftCore芯研社

阅读(421)

评论(0)

推荐(0)

2021年2月15日

vivado警告记录——[Timing 38-316]

摘要: 警告记录:[Timing 38-316] Clock period '20.000' specified during out-of-context synthesis of instance 'dds_module/dds_rom' at clock pin 'clka' is different

阅读全文

posted @ 2021-02-15 21:45 AdriftCore芯研社

阅读(4489)

评论(0)

推荐(0)

2021年2月12日

FPGA时序约束学习笔记——IO约束

摘要: 一、参考模型 图源来自《【抢先版】小梅哥FPGA时序约束从遥望到领悟》 二、参数分析 T(0)->(3) = Tclk1 T(3)->(4) = Tco T(4)->(5) + T(5)->(6) = Tdata T(4)->(5) = Tdata(Init) T(5)->(6) = Tdata(P

阅读全文

posted @ 2021-02-12 16:08 AdriftCore芯研社

阅读(934)

评论(0)

推荐(0)

2021年2月11日

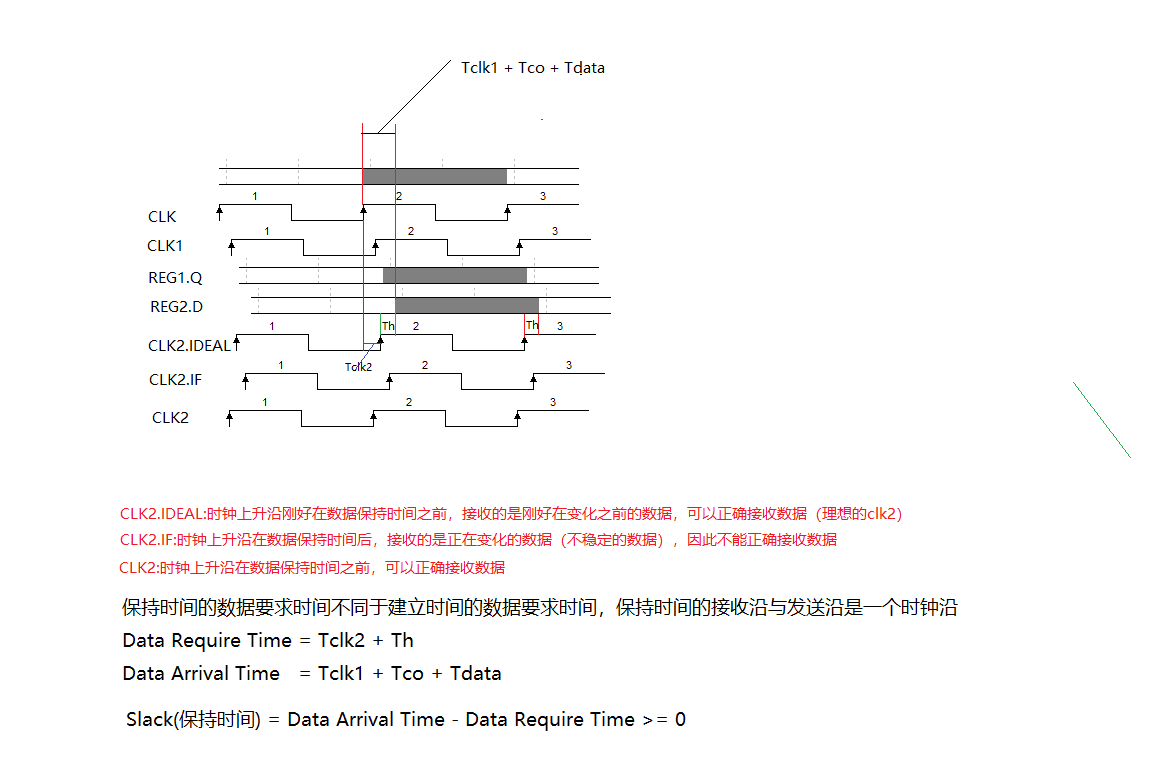

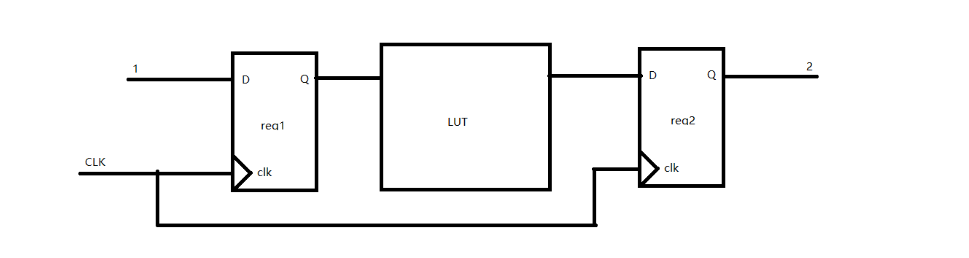

FPGA时序约束学习笔记——时序分析模型(保持时间)

摘要:

阅读全文

posted @ 2021-02-11 21:33 AdriftCore芯研社

阅读(136)

评论(0)

推荐(1)

2021年2月9日

FPGA时序约束学习笔记——TimeQuest

摘要: 一、基本操作 STEP1:quaturs ——> tool ——> TimeQuest Timing Analyzer STEP2:Create Timing NetList(创建时序网表) STEP3:读取SDC文件(设计约束文件) STEP4:查看报告/创建时钟约束 (1)查看报告 report

阅读全文

posted @ 2021-02-09 00:09 AdriftCore芯研社

阅读(859)

评论(0)

推荐(1)

2021年2月6日

FPGA——SPI从机通信实现与仿真

摘要: 一、设计思路 发送数据计数器 接收数据计数器 从机的时钟SCK是由主机支持的,所以不是一个时钟域,接收时钟SCK需要防止亚稳态接两级触发器 因为边沿检测接两级触发器延后一拍,所以接收的数据要再接一级触发器,与接收数据的边沿对齐 二、参数化设计 从机代码参数说明 DATA_W:为接收、发送数据的个数

阅读全文

posted @ 2021-02-06 19:40 AdriftCore芯研社

阅读(4905)

评论(2)

推荐(3)

2021年2月5日

FPGA——IIC状态机实现及仿真

摘要: 一、设计思路 二、IIC代码 module iic_module( rst_n , clk , waddr_num , //选择两字节地址或单字节地址 device_addr , word_addr , wr , wr_data , wr_data_vld , rd , rd_data , rd_d

阅读全文

posted @ 2021-02-05 17:29 AdriftCore芯研社

阅读(2543)

评论(3)

推荐(1)

2021年2月1日

FPGA——串口传图到RAM并TFT显示

摘要: 一、设计思路 RAM读问题 RAM为了使得性能更好加了输出寄存器,时钟上升沿读到地址后的三个时钟周期才会输出该地址的数据,这就会让读端的首地址读多次造成结果上的不准确 解决方法有两种:一、让DATA_VLD提前几拍,经过验证该方法会造成计数器与数据不匹配,由此带来的一系列问题不是很好解决。二、让TF

阅读全文

posted @ 2021-02-01 21:46 AdriftCore芯研社

阅读(585)

评论(0)

推荐(0)

FPGA——TFT显示屏驱动

摘要: 一、TFT时序 视频电子标准协会(Video Electronics Standards Association)显示器时序标准(Monitor Timing Standard) https://vesa.org/vesa-standards/ 二、设计思路 800 * 480 60Hz的意义 该显

阅读全文

posted @ 2021-02-01 20:43 AdriftCore芯研社

阅读(2014)

评论(0)

推荐(1)

上一页

1

2

3

4

5

6

7

下一页

公告