打工人日报#20251002 - 教程

打工人日报#20251002

假期进行中

知识点

用按键来控制 LED 灯闪烁

功能:

LED默认常亮

按下按键对应的LED熄灭

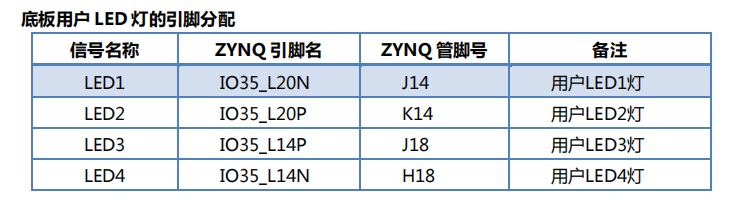

当连接用户 LED 灯的 IO 电压为高时,用户 LED 灯熄灭,当连接 IO 电压为低时,用户 LED 会被点亮。

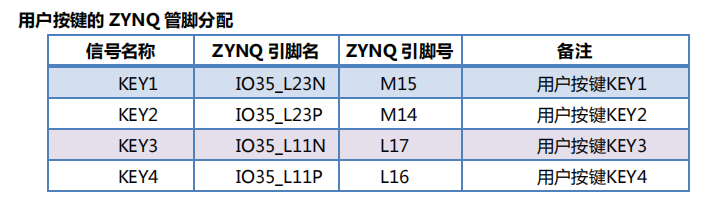

4 个用户 KEY 均连接到 PL 端 BANK35的 IO 上。按键按下,信号为低

由于前面的练习,已经熟悉vivado操作方法了,这里省略,仅展示关键步骤

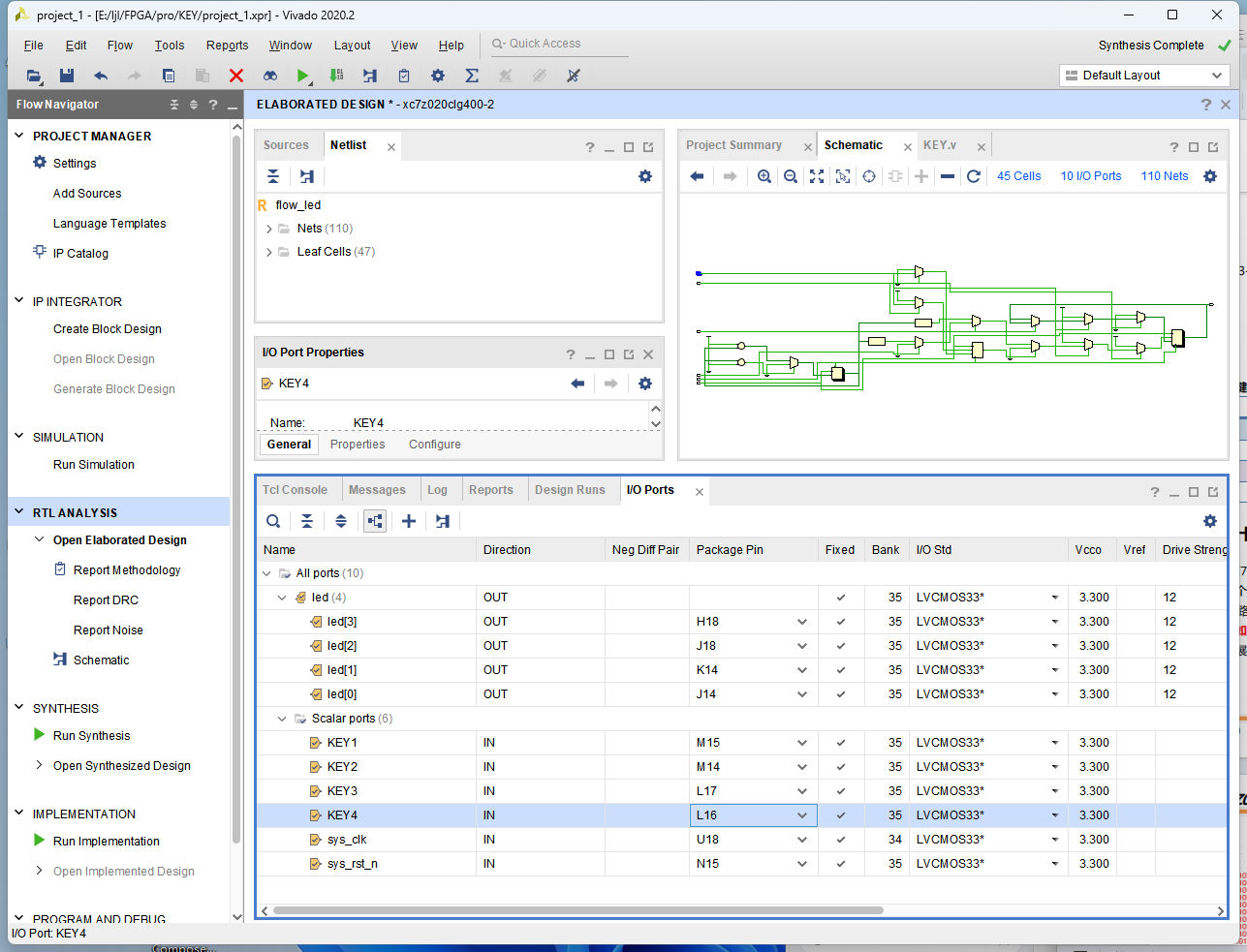

管脚约束

KEY.v

module flow_led (

input sys_clk,

input sys_rst_n,

input KEY1,

input KEY2,

input KEY3,

input KEY4,

output reg [3:0] led

);

reg [24:0] cnt;

// LED控制部分

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

led <= 4'b1111;

end else if (!KEY4) begin

led <= 4'b1000;

end else if (!KEY3) begin

led <= 4'b0100;

end else if (!KEY2) begin

led <= 4'b0010;

end else if (!KEY1) begin

led <= 4'b0001;

end

end

endmodule- module flow_led 定义了一个名为 flow_led 的模块。

- 该模块有六个输入端口:

- sys_clk:通常代表系统时钟信号,用于驱动模块内的时序逻辑。虽然在当前代码的逻辑实现中,时钟信号并没有被有效利用来实现随时间变化的动态功能,但它可能是为后续扩展功能预留的。

- sys_rst_n:低电平有效的复位信号。当该信号为低电平时,会触发模块内的复位逻辑。

- KEY1、KEY2、KEY3、KEY4:这四个输入端口大概率是用于连接外部按键的信号。根据代码逻辑,低电平表示按键按下。

- 一个输出端口 led:这是一个 4 位的寄存器类型输出,用于控制 LED 的状态。

- reg [24:0] cnt;:声明了一个 25 位的寄存器 cnt。然而,在当前代码中,这个寄存器没有被使用到,可能是为未来添加基于计数的功能预留的,比如实现跑马灯的速度控制等。

- always @(posedge sys_clk or negedge sys_rst_n):这个 always 块对 sys_clk 的上升沿和 sys_rst_n 的下降沿敏感。

- if (!sys_rst_n) begin led <= 4’b1111; end:当复位信号 sys_rst_n 为低电平时,将 led 赋值为 4’b1111,即所有 LED 点亮,这是模块的初始状态。

- else if (!KEY4) begin led <= 4’b1000;:如果 KEY4 信号为低电平(按键 4 按下),将 led 赋值为 4’b1000,此时只有最高位 LED 熄灭。

- else if (!KEY3) begin led <= 4’b0100;:如果 KEY3 信号为低电平(按键 3 按下),将 led 赋值为 4’b0100,此时只有次高位 LED 熄灭。

- else if (!KEY2) begin led <= 4’b0010;:如果 KEY2 信号为低电平(按键 2 按下),将 led 赋值为 4’b0010,此时只有次低位 LED 熄灭。

- else if (!KEY1) begin led <= 4’b0001;:如果 KEY1 信号为低电平(按键 1 按下),将 led 赋值为 4’b0001,此时只有最低位 LED 熄灭。

KEY.xdc

这个是可以自动保存的,这里做对比参考

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property PACKAGE_PIN H18 [get_ports {led[3]}]

set_property PACKAGE_PIN J18 [get_ports {led[2]}]

set_property PACKAGE_PIN K14 [get_ports {led[1]}]

set_property PACKAGE_PIN J14 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports KEY1]

set_property IOSTANDARD LVCMOS33 [get_ports KEY2]

set_property IOSTANDARD LVCMOS33 [get_ports KEY3]

set_property IOSTANDARD LVCMOS33 [get_ports KEY4]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property PACKAGE_PIN N15 [get_ports sys_rst_n]

set_property PACKAGE_PIN M15 [get_ports KEY1]

set_property PACKAGE_PIN M14 [get_ports KEY2]

set_property PACKAGE_PIN L17 [get_ports KEY3]

set_property PACKAGE_PIN L16 [get_ports KEY4]

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]流程总结

创建工程

添加XX.v

Open Elaborated Design

添加管脚约束

Run Synthesis

添加时序约束

Run implementation

Generate Bitstream

上板验证

阅读

《杀死一只知更鸟》

第七章 结束

浙公网安备 33010602011771号

浙公网安备 33010602011771号