systemverilog数据类型

1,logic类型:

verilog中最常使用的数据类型是变量(reg)和线网(wire),在编码或测试的时候经常需要区分两种数据类型的不同使用方法。在SV中定义logic可以取代这两种数据类型。

logic不仅能够作为变量,而且可以被连续赋值,门单元和模块所驱动。但是logic不能够被多个结构体驱动。下面这段代码展示了logic的使用方法。

module logic_test(input logic rst_h

);

parameter CYCLE = 20;

logic q,q_1,d,clk,rst_1;

initial

begin

clk = 0;

forever #(CYCLE/2) clk = ~clk; // 过程赋值

end

assign rst_1 = ~ rst_h; //连续赋值

not n1(q_1,q); //q_1被门驱动

my_dff d1(q,d,clk,rst_1); //q被模块驱动

endmodule

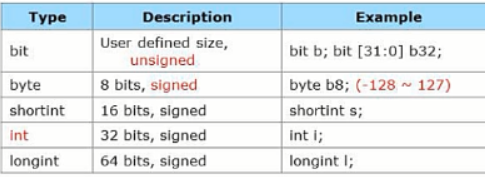

2,双状态数据类型。

相比于verilog中的4状态数据类型(1,0,x,z),SV引入双状态数据类型有利于提高仿真器的性能并减少内存的使用量。下面逐例解释。

bit b; // 双状态 单bit

bit [31:0] b32; // 双状态,32bit,无符号

int unsigned ui; // 双状态,32bit,无符号

int i; // 双状态,32bit,有符号

byte b8; // 双状态,8bit ,有符号

shortint s; // 双状态,16bit,有符号

longint l; // 双状态,64bit,有符号

integer i4; // 四状态,32bit,有符号

time t; // 四状态,64bit,无符号

real r; // 双状态,双精度浮点数。

浙公网安备 33010602011771号

浙公网安备 33010602011771号