日常记录(89)VCS使用

仿真事件队列

VCS首先读取RTL代码,设置仿真时间t=0,然后开始仿真。

active region:执行原语、$dislpay,连续赋值assign,阻塞赋值=,非阻塞赋值的RHS(右手语句righthand statement)

inactive region: #0的时间相关赋值

nonblocking assign region:非阻塞赋值的赋值部分

monitor region:$monitor函数的执行

feature region

代码

module taa ();

int a;

initial begin

a = 1;

#10;

a = 1;

#0 a = 2;

$display("%0t,display value a is %0d",$time, a);

#10;

a = 3;

a <= 4;

$display("%0t,display value a is %0d",$time, a);

#10

$finish;

end

initial begin

$monitor("%0t, monitor value a is %0d",$time, a);

end

endmodule

输出

monitor明显得到的值是非阻塞之后的,display得到的是立即的输出值

0, monitor value a is 1

10,display value a is 2

10, monitor value a is 2

20,display value a is 3

20, monitor value a is 4

$finish called from file "taa.sv", line 14.

增量编译

-Mupdate

使得编译过程中值编译改变的文件

有以下效果:

Both modules done.

However, due to incremental compilation, only 2 modules need to be compiled.

工艺库

SMIC 中芯国际

-v 库文件名

-y 库查找路径

+libext+库后缀名

示例(vcs lab1):

add8加法器引用了add4的加法器,而add4.v本身在../../lib/目录。

vcs addertb.v add8.v -y ../../lib/ +libext+.v -R

+incdir+文件查找路径

-f 文件列表

-o 输出可执行文件名

+define+宏=值

定义Makefile:

vcs -sverilog -R +define+MACRO=1234 taa.sv -o target

定义taa.sv

module taa ();

initial begin

$display("MACRO is %d", `MACRO);

end

endmodule

输出:

MACRO is 1234

DesignWare

https://www.synopsys.com/zh-cn/designware-ip.html

DesignWare为synopsys自己开发的一些软IP,其中包括加法器,乘法器,比较器,FIFO等IP,根据约束,DC会直接调用相应适合的IP核。

仿真性能取决因素

- RTL程序本身

- 工具优化

- debug开关的控制

- 需要重新编译的必要性

VCS debug考虑的因素

- 仿真速度

- 信号可视化

- 信号可追踪

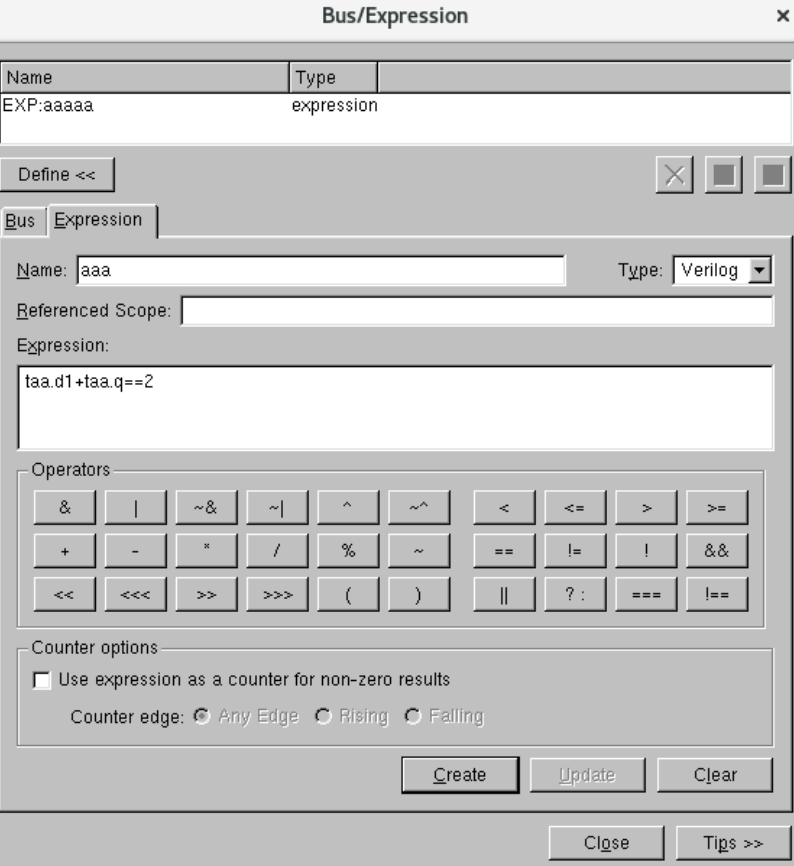

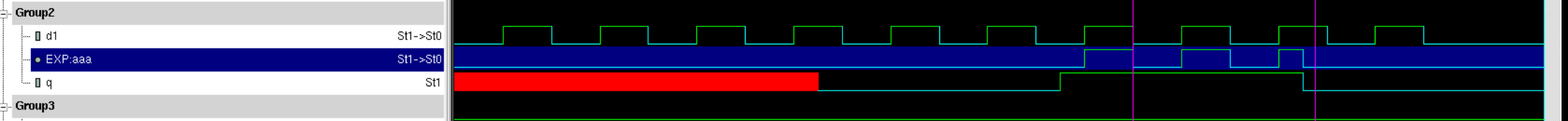

DVE创建bus

全称:Discovery Visual Environment

创建bus,设置相加

输出:

vcdpluson的使用

- 只保存一个信号

$vcdpluson(taa.clk);

- 其它参数:

(level_number,module_instance,net_or_reg)

(层级,0为所有层,模块实例,寄存器) - 更改波形名

-vpdfile+filename - 关闭仿真

$vcdplusoff

- dve对应打开vpd文件

verdi对应为sdb文件

覆盖率

-cm line+cond+fsm+branch+tgl

不合规的代码

出现竞争的代码不合规,

- 以下代码前面读不和规,后面写不和规

module tbb ();

reg a;

initial begin

a = 0; #10 a = 1;

end

initial begin

#10 if (a) begin

$display("May not print");

end

end

initial #20 a=0;

initial #20 a=1;

endmodule

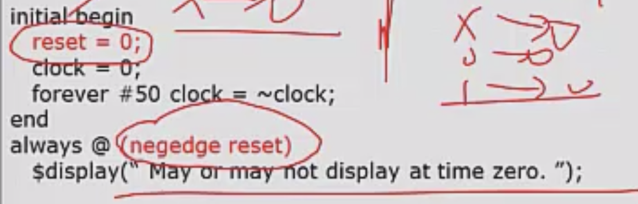

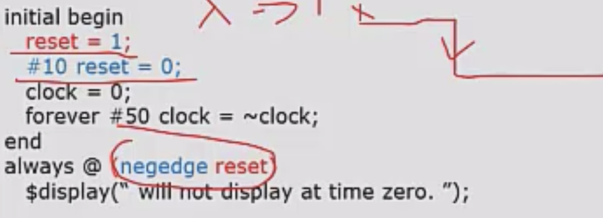

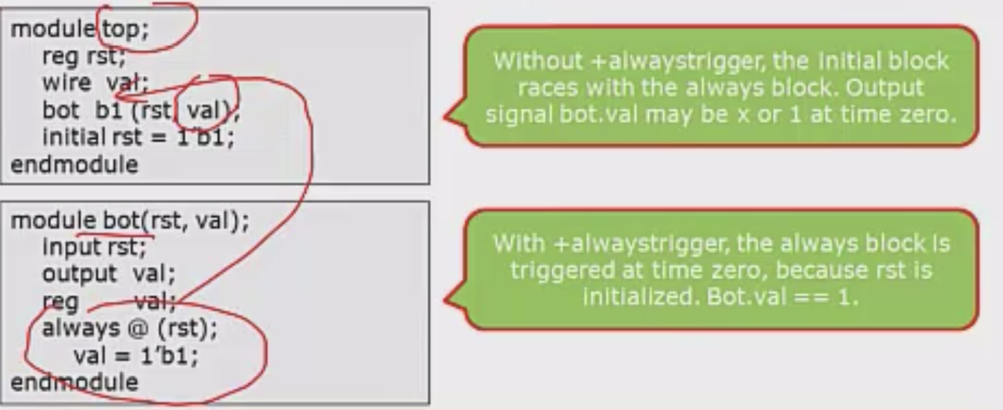

- 0时刻的问题,从x信号到0会不会触发always语句

修改后:

vcs5.2之后,默认了+alwaystrigger,使得x到1认为是跳变

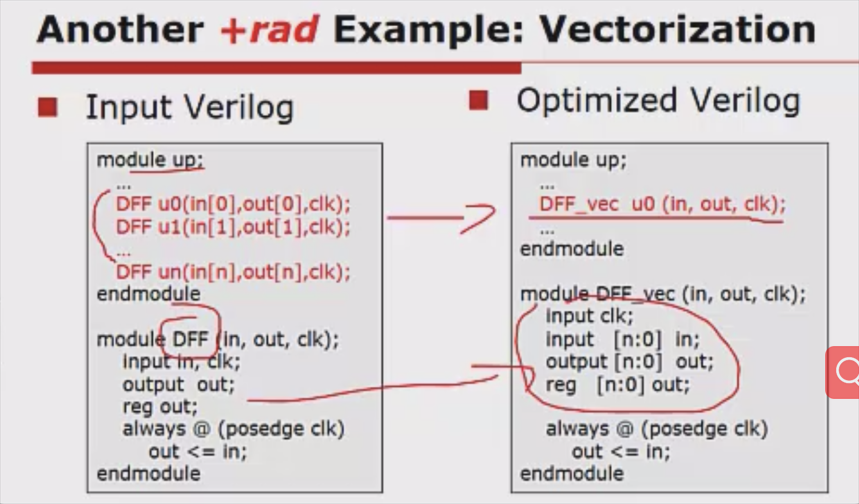

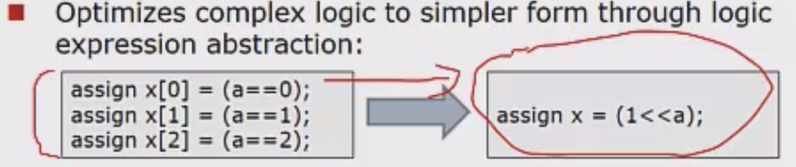

rad优化

- 在提高了RTL代码的基础上

- 使用+rad参数提升RTL的代码质量

radiant technology

在compile阶段对Verilog code进行优化,以提高仿真性能。

优化示例:

- 优化可能改变了设计的hierarchy

- 当编译的sdf文件被使用,rad模式disabled

simprofile测算

测算耗时,定位仿真耗时瓶颈,用于优化

排除部分覆盖率收集

- 使用注释

仍综合

- // VCS coverage on

- // VCS coverage off

- 使用注释

不收集且部综合

- // synopsys translate_on

- // synopsys translate_off

覆盖率收集选项

- 设定包含或者排除的模块

-cm_hier <module_>(未生效) - 设定报告名

-cm_name <name_>(未生效)

覆盖率贡献程度

-grade (未示例)

静态冒险检测race

对always语句(非posedge和negedge)和assign构成的潜在环检测。

检测内容有限

Makefile

tcc:

vcs -R tcc.sv

tcc1:

vcs -R tcc.sv +race=all

tcc.sv

module tcc ();

reg A, B, D;

wire C;

always @( A or C ) begin

D = C;

B = A;

end

assign C = B;

endmodule

输出race.out.static

Race-[CLF] Combinational loop found

"tcc.sv", 4: The trigger 'C' of the always block can cause the following

sequence of event(s) which can again trigger the always block.

"tcc.sv", 6: B = A;

which triggers 'B'.

"tcc.sv", 9: assign C = B;

which triggers 'C'.

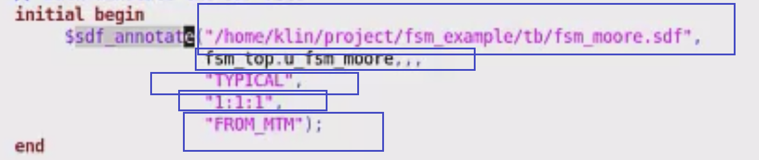

sdf反标rtl

使用$sdf_annotate函数

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号