日常记录(84)校验位、正则等

UART串口校验方式(无校验、奇偶校验、固定校验)

概念

https://www.codenong.com/cs106550351/

- 奇校验(ODD):添加校验位,使得每个字节传送整个过程中bit为1的个数是奇数个。

- 偶校验(EVEN):添加校验位,使得每个字节传送整个过程中bit为1的个数是偶数个。

- 无校验(NONE): 没有校验位。

- 固定校验位(Stick):校验位为LCR的bit4内容取反。(设置为奇校验取1,偶校验取0)

校验计算

偶校验,先取parity_bit = 0,然后按位异或叠加,获得偶校验。

这里校验输出为1.

// even parity

module taa ();

logic [7:0] data = 8'bxx001110;

logic parity_bit = 0;

initial begin

for (int i = 0; i < 6; i++) begin

parity_bit ^= data[i];

end

$display("parity bit is %0b", parity_bit);

parity_bit = ^data[5:0];

$display("parity bit is %0b", parity_bit);

end

endmodule

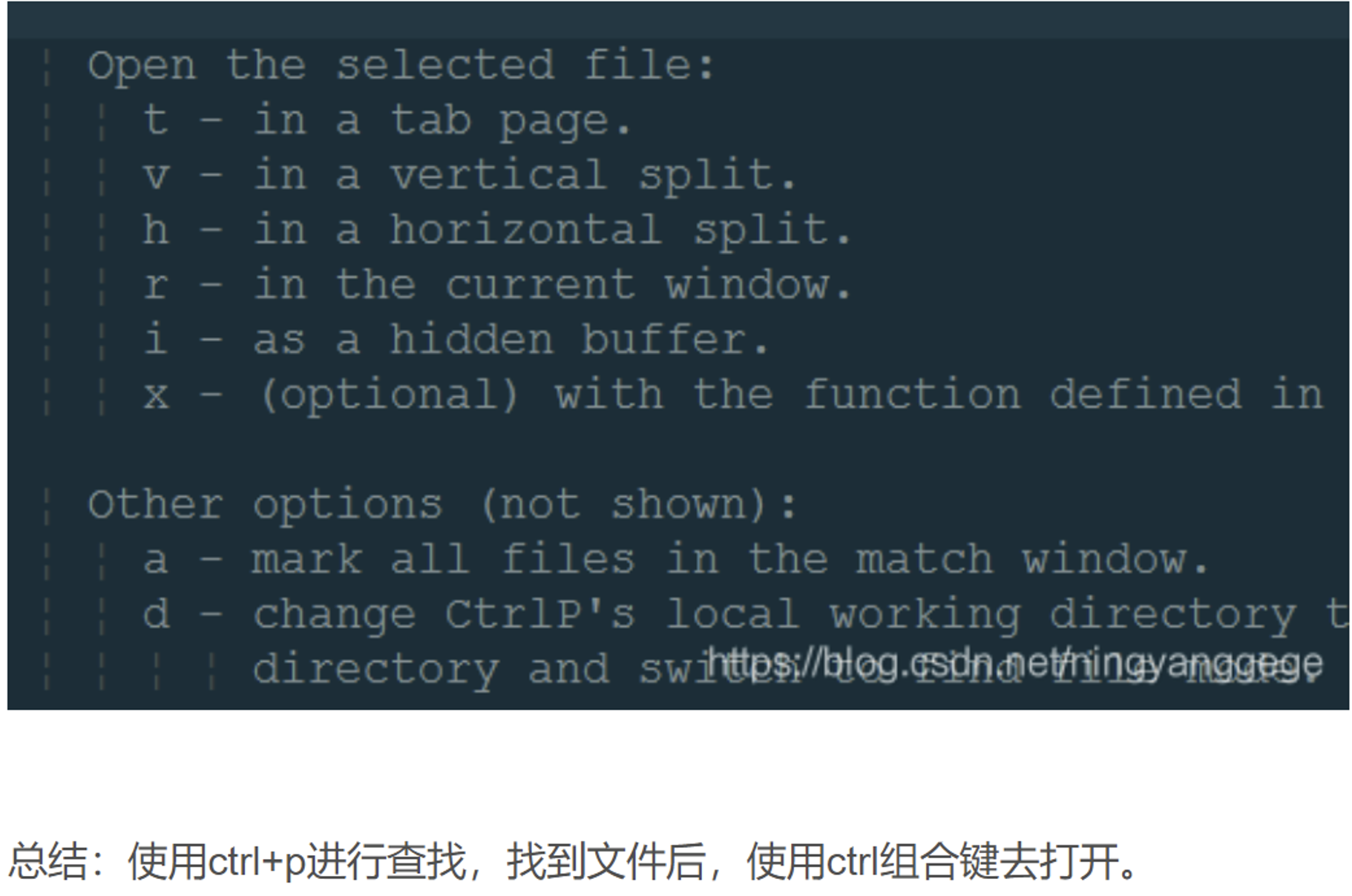

Ctrlp插件打开文件的形式,快捷键

- t 新标签

- v 垂直

- h 水平

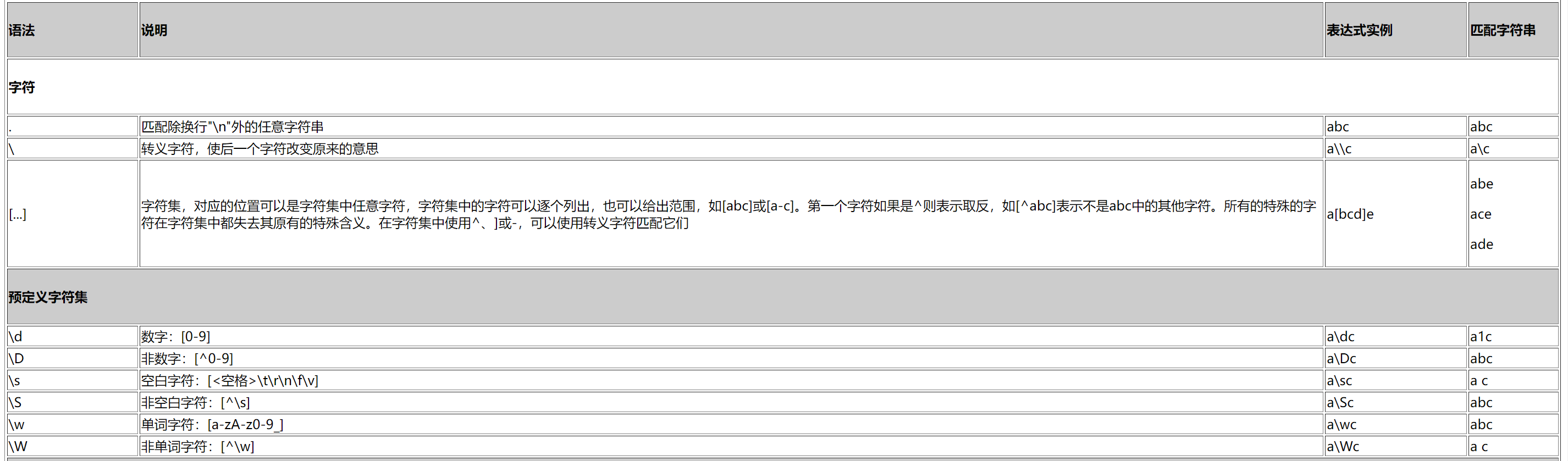

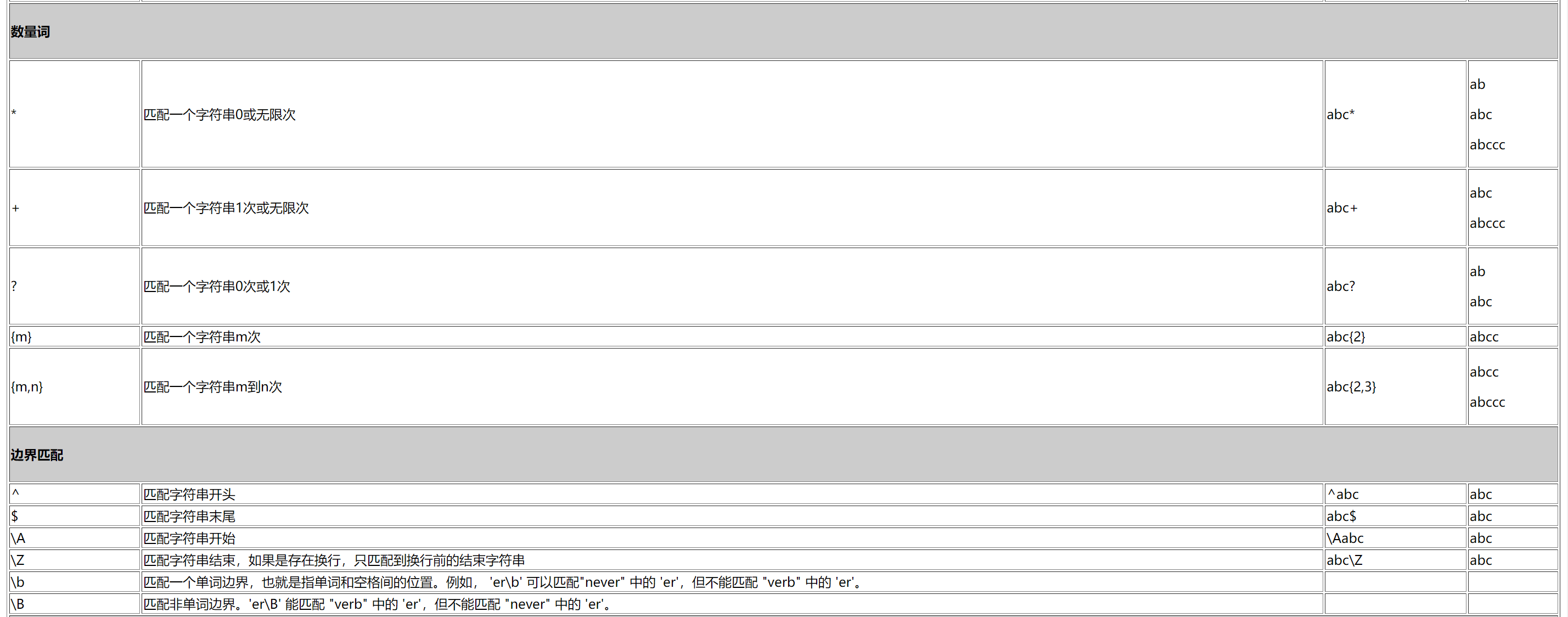

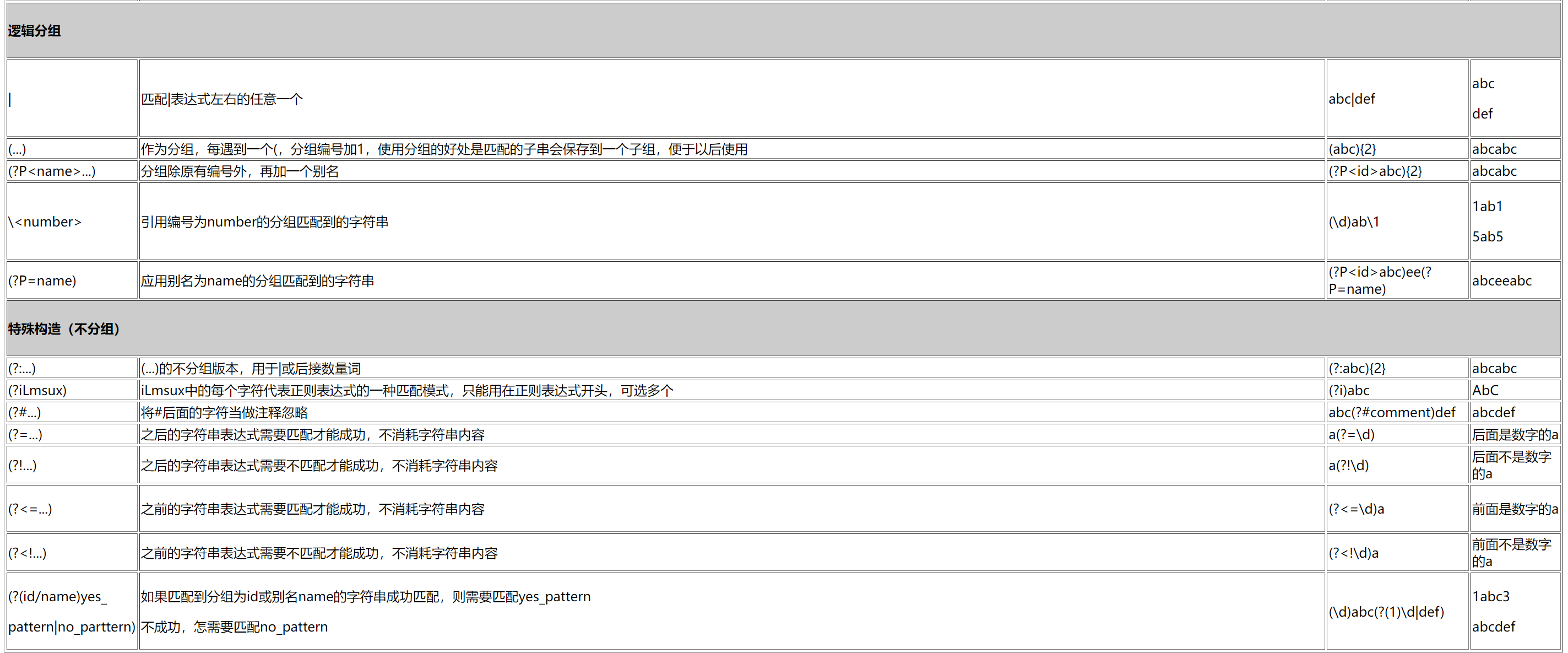

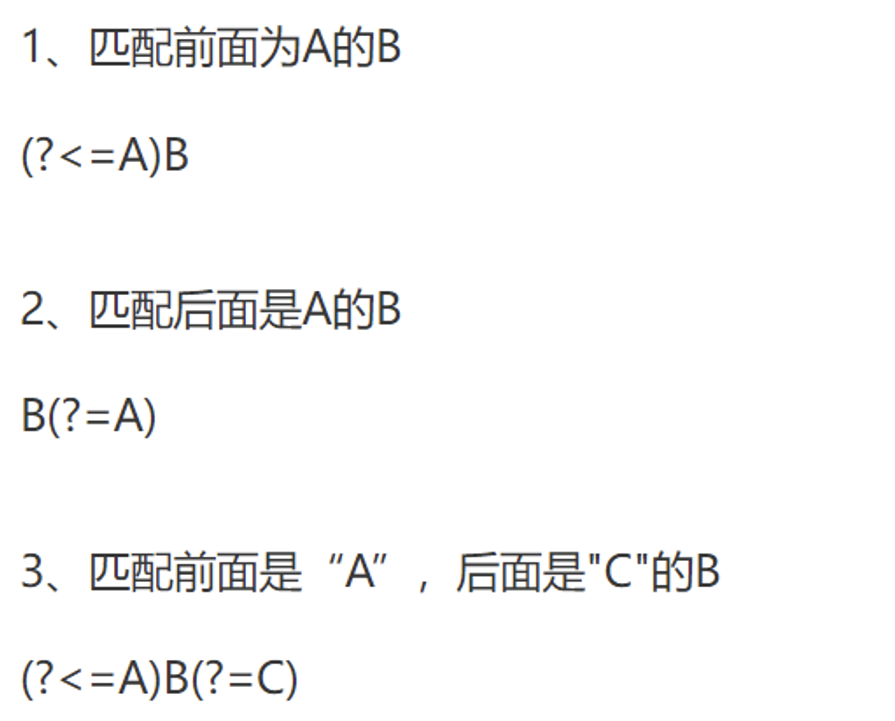

正则表达式匹配

第8章第3节

详表

http://web.suda.edu.cn/hejun/chapter8/regular_expression_table.html

匹配特定

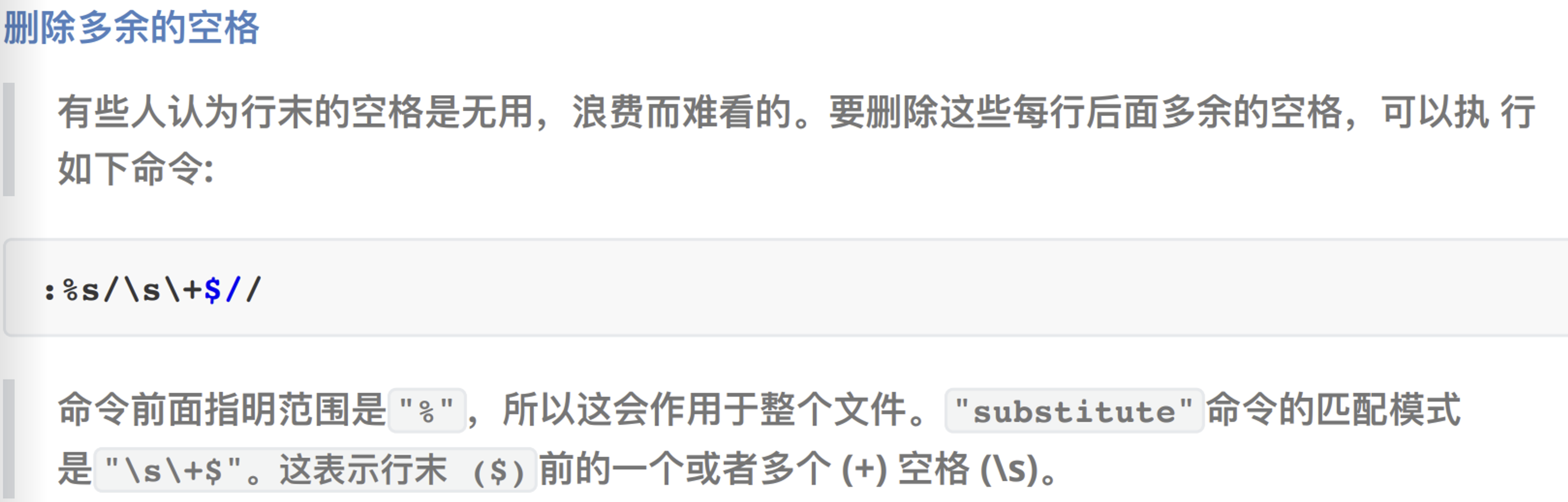

vim删除行末空格

UVM reg_field的易失位理解

在软件实现硬件驱动和固件层时,也会实现类似寄存器模型镜像值的方法,即在寄存器配置的底层函数中,

同时也声明一些全局的影子寄存器(shadow register)。这些影子寄存器的功能就是暂存当时写入寄存器的值,

而在后期使用时,如果这些寄存器是非易失的(non-volatile),那么便可以省略读取寄存器的步骤,转而使用影子寄存器的值,

这么做的好处在于响应更迅速,而不再通过若干个时钟周期的总线发起和响应,但另外一方面这么做的前提同我们测试寄存器模型的目的是一样的,

即寄存器的写入值可以准确地反映在硬件中的寄存器上。

https://blog.eetop.cn/blog-1561828-6266225.html

m_volatile,易失性标志位,在field中,当该位为1,表示每次调用needs_update时都会返回1,

即每次在用户check该寄存器是否需要update时,该field的返回都是需要update。

https://blog.eetop.cn/blog-1765812-6945802.html

VIM按键映射问题

Vim 里有很多键不能 map 的,大部分是因为终端不支持这样的组合键。

链接:https://www.zhihu.com/question/23225258/answer/24012145

【ctrl+v+i】可以強制輸入tab

ctags操作

ctags --list-languages

识别哪些语言

ctags --list-maps

默认哪些扩展名对应哪些语言

--langmap=SystemVerilog:.sv.v.svh.tv.vg.vinc

设置语言对应的拓展名

ctags --list-kinds

查看ctags可以识别的语法元素

SystemVerilog的ctags举例

--langdef=systemverilog

--langmap=systemverilog:.sv.svh.svi

--regex-systemverilog=/^[ \t]*(virtual)?[ \t]*class[ \t]*([a-zA-Z_0-9]+)/\2/c,class/

--regex-systemverilog=/^[ \t]*(virtual)?[ \t]*task[ \t]*.*::([a-zA-Z_0-9]+)[\t]*[(;]/\2/t,task/

--regex-systemverilog=/^[ \t]*(virtual)?[ \t]*function[ \t]*.*::([a-zA-Z_0-9]+)[ \t]*[(;]/\2/f,function/

--regex-systemverilog=/^[ \t]*module[ \t]*([a-zA-Z_0-9]+)/\1/m,module/

--regex-systemverilog=/^[ \t]*program[ \t]*([a-zA-Z_0-9]+)/\1/p,program/

--regex-systemverilog=/^[ \t]*interface[ \t]*([a-zA-Z_0-9]+)/\1/i,interface/

--regex-systemverilog=/^[ \t]*typedef[ \t]+.*[ \t]+([a-zA-Z_0-9]+)[ \t]*;/\1/e,typedef/

--regex-systemverilog=/^[ \t]*`define[ \t]*([a-zA-Z_0-9]+)/`\1/d,define/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*shortint[ \t]*([a-zA-Z_0-9]+).*/`\5/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*int[ \t]*(unsigned)?[ \t]*([a-zA-Z_0-9]+).*/`\6/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*longint[ \t]*(unsigned)?[ \t]*([a-zA-Z_0-9]+).*/`\6/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*byte[ \t]*([a-zA-Z_0-9]+).*/`\5/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*bit[ \t]*([a-zA-Z_0-9]+).*/`\5/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*logic[ \t]*([a-zA-Z_0-9]+).*/`\5/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*reg[ \t]*([a-zA-Z_0-9]+).*/`\5/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*integer[ \t]*([a-zA-Z_0-9]+).*/`\5/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*(rand)?[ \t]*time[ \t]*([a-zA-Z_0-9]+).*/`\5/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*real[ \t]*([a-zA-Z_0-9]+).*/`\4/v,variable

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*shortreal[ \t]*([a-zA-Z_0-9]+).*/`\4/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*chandle[ \t]*([a-zA-Z_0-9]+).*/`\4/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*string[ \t]*([a-zA-Z_0-9]+).*/`\4/v,variable/

--regex-systemverilog=/^[ \t]*(static)?[ \t]*(local)?[ \t]*(private)?[ \t]*event[ \t]*([a-zA-Z_0-9]+).*/`\4/v,variable/

--regex-systemverilog=/^[ \t]*`SVT_REPLACEABLE_DEFINE\([ \t]*([a-zA-Z_0-9]+),.*\)/`\1/d,define/

--systemverilog-kinds=+ctfmpied

--langdef=altsystemverilog

--regex-altsystemverilog=/^[ \t]*(extern)?[ \t]*(virtual)?[ \t]*(protected)?[ \t]*class[ \t]*([a-zA-Z_0-9]+)/\4/c,class/

--regex-altsystemverilog=/^[ \t]*(extern)?[ \t]*(virtual)?[ \t]*(protected)?[ \t]*task[ \t]*.*[ \t]+([a-zA-Z_0-9]+)[\t]*[(;]/\4/t,task

--regex-altsystemverilog=/^[ \t]*(extern)?[ \t]*(virtual)?[ \t]*(protected)?[ \t]*function[ \t]*.*[ \t]+([a-zA-Z_0-9]+)[ \t]*[(;]/\4/f,function/

--regex-altsystemverilog=/^[ \t]*(virtual)?[ \t]*task[ \t]*.*[ \t]+([a-zA-Z_0-9]+)[\t]*[(;]/\2/t,task/

--regex-altsystemverilog=/^[ \t]*(virtual)?[ \t]*function[ \t]*.*[ \t]+([a-zA-Z_0-9]+)[ \t]*[(;]/\2/f,function/

对应的vim配置

tags使用逗号分隔,每个tags使用分号结尾。在每次写入后,更新tags

set tags=./.tags;,/home/synopsys/vcs/O-2018.09-SP2/etc/uvm-1.2/.tags;

autocmd BufWritePost * call system("ctags -R --extras=+q --fields=+i -n -f .tags")

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号