日常记录(71)+181

Makefile

点击查看代码

comp=vcs -sverilog -debug_access_all -ntb_opts uvm-1.2

taa:

set -e

$(comp) taa.sv

./simv

tbb:

set -e

vcs -sverilog tbb.sv

./simv

tcc:

set -e

$(comp) tcc.sv

./simv

tdd:

set -e

$(comp) tdd.sv

./simv

tee:

set -e

$(comp) tee.sv

# ./simv +UVM_TIMEOUT="100s, YES" +UVM_PHASE_TRACE

./simv +UVM_TIMEOUT="100s, YES" +UVM_OBJECTION_TRACE

tff:

set -e

$(comp) tff.sv

./simv

tgg:

set -e

$(comp) tgg.sv

./simv

clean:

@rm -rf *.log simv* *.key csrc DVEf* work tags *.vdb urgReport

get_peek通信

实现6个方法

- get

- try_get

- can_get

- peek

- try_peek

- can_peek

注意点

- try和can用于非阻塞,不能延时,是函数。get如果没有延时也可以用函数,有延时用task。

- 一般形参默认是input,在这里定义的get函数、peek、try相关,需要手动说明output。(虽然ref可行,但是不太正规)

- can_* try_*的返回值,为1表示正常,即可以进行动作,后者并且进行了动作。

- input的机制是输入数据进行备份,在返回后丢弃。output的机制是在输入数据的时候重新初始化,在输出的时候数据赋值。ref是引用,前后的指针不变,对指针指向的内容操作。

(Verilog对参数的处理方式比较简单,在子程序的开头把input和inout的值复制给本地变量,在子程序退出时,则复制output和inout的值)

https://www.cnblogs.com/csjt/p/15819475.html - imp的末尾端口,定义的时候trans在前,类名在后。

module taa ();

import uvm_pkg::*;

class my_trans extends uvm_sequence_item;

`uvm_object_utils(my_trans)

// data or class properties

int a;

// initialization

function new(string name="my_trans");

super.new(name);

endfunction : new

endclass : my_trans

class Getter extends uvm_component;

`uvm_component_utils(Getter)

// data or class properties

uvm_get_peek_port#(my_trans) gpp;

// initialization

function new(string name="Getter ", uvm_component parent);

super.new(name, parent);

gpp = new("gpp", this);

endfunction : new

endclass : Getter

class Sender extends uvm_component;

uvm_get_peek_imp#(my_trans, Sender) gpi;

`uvm_component_utils(Sender)

function new(string name="Sender", uvm_component parent);

super.new(name, parent);

gpi = new("gpi", this);

endfunction : new

function void get(output my_trans a);

`uvm_info("GET_ADDR", $sformatf("address get %h", a), UVM_LOW)

a = new("a");

a.a = 1;

endfunction: get

function bit try_get(output my_trans a);

a = new("a");

a.a = 2;

return 1;

endfunction: try_get

function bit can_get();

return 1;

endfunction: can_get

function void peek(output my_trans a);

a = new("a");

a.a = 3;

endfunction: peek

function bit can_peek();

return 1;

endfunction: can_peek

function bit try_peek(output my_trans a);

a = new("a");

a.a = 4;

return 1;

endfunction: try_peek

endclass : Sender

class my_test extends uvm_test;

Sender sdr;

Getter gtr;

`uvm_component_utils(my_test)

function new(string name="my_test", uvm_component parent);

super.new(name, parent);

endfunction : new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

sdr = Sender::type_id::create("sdr", this);

gtr = Getter::type_id::create("gtr", this);

endfunction

function void connect_phase(uvm_phase phase);

gtr.gpp.connect(sdr.gpi);

super.connect_phase(phase);

endfunction

task run_phase(uvm_phase phase);

my_trans a;

bit status;

a = new("a");

phase.raise_objection(this);

`uvm_info("GET_ADDR_BEF", $sformatf("address get %h", a), UVM_LOW)

gtr.gpp.get(a);

`uvm_info("GET_ADDR_AFT", $sformatf("address get %h", a), UVM_LOW)

`uvm_info("VAULE_AFTER", $sformatf("after a is %d", a.a), UVM_LOW)

status = gtr.gpp.try_get(a);

`uvm_info("VAULE_AFTER", $sformatf("status : %d after a is %d", status, a.a), UVM_LOW)

status = gtr.gpp.can_get();

`uvm_info("VAULE_AFTER", $sformatf("status a is %d", status), UVM_LOW)

status = gtr.gpp.try_peek(a);

`uvm_info("VAULE_AFTER", $sformatf("status : %d after a is %d", status, a.a), UVM_LOW)

status = gtr.gpp.can_peek();

`uvm_info("VAULE_AFTER", $sformatf("status is %d", status), UVM_LOW)

gtr.gpp.peek(a);

`uvm_info("VAULE_AFTER", $sformatf("after a is %d", a.a), UVM_LOW)

phase.drop_objection(this);

endtask: run_phase

endclass : my_test

initial begin

run_test("my_test");

end

endmodule

输出结果

- 在get传入的trans,是不需要实例化的,这里实例化以后,获得了地址f0f27258

- 返回的地址是从被调用者那里实例化的结果。

UVM_INFO @ 0: reporter [RNTST] Running test my_test...

UVM_INFO taa.sv(94) @ 0: uvm_test_top [GET_ADDR_BEF] address get f0f27258

UVM_INFO taa.sv(38) @ 0: uvm_test_top.sdr [GET_ADDR] address get 00000000

UVM_INFO taa.sv(96) @ 0: uvm_test_top [GET_ADDR_AFT] address get f0f276c0

UVM_INFO taa.sv(97) @ 0: uvm_test_top [VAULE_AFTER] after a is 1

UVM_INFO taa.sv(100) @ 0: uvm_test_top [VAULE_AFTER] status : 1 after a is 2

UVM_INFO taa.sv(103) @ 0: uvm_test_top [VAULE_AFTER] status a is 1

UVM_INFO taa.sv(106) @ 0: uvm_test_top [VAULE_AFTER] status : 1 after a is 4

UVM_INFO taa.sv(109) @ 0: uvm_test_top [VAULE_AFTER] status is 1

UVM_INFO taa.sv(112) @ 0: uvm_test_top [VAULE_AFTER] after a is 3

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_objection.svh(1276) @ 0: reporter [TEST_DONE] 'run' phase is ready to proceed to the 'extract' phase

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_catcher.svh(705) @ 0: reporter [UVM/REPORT/CATCHER]

--- UVM Report catcher Summary ---

Number of demoted UVM_FATAL reports : 0

Number of demoted UVM_ERROR reports : 0

Number of demoted UVM_WARNING reports: 0

Number of caught UVM_FATAL reports : 0

Number of caught UVM_ERROR reports : 0

Number of caught UVM_WARNING reports : 0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 0: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 13

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[GET_ADDR] 1

[GET_ADDR_AFT] 1

[GET_ADDR_BEF] 1

[RNTST] 1

[TEST_DONE] 1

[UVM/RELNOTES] 1

[UVM/REPORT/CATCHER] 1

[VAULE_AFTER] 6

$finish called from file "/home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_root.svh", line 527.

$finish at simulation time 0

input output ref在线

module tbb ();

class c;

int v0;

int v1;

endclass

function void f1(input c c0);

c0.v0 = 3;

endfunction

function void f2(output c c0);

c0.v0 = 3;

endfunction

function void f3(ref c c0);

c0.v0 = 3;

endfunction

function void run();

c r=new();

c r2=new();

c r3=new();

r.v0 = 1;

r.v1 = 2;

f1(r);

$display("input %0x %0x",r.v0,r.v1);

r2.v0 = 1;

r2.v1 = 2;

f2(r2);

$display("output %0x %0x",r2.v0,r2.v1);

r3.v0 = 1;

r3.v1 = 2;

f3(r3);

$display("ref %0x %0x",r3.v0,r3.v1);

endfunction

initial begin

run();

end

endmodule

输出结果:

input本身拿到的是地址,而且是指向实例化的地址空间,可用。

但是和function void get(output my_trans a);相比,如果output改为input,整个是无法通信的,说明UVM内部通信不是简单的传递了,但是改成ref是可以通信的

input 3 2

output 3 2

ref 3 2

transport通信

要点说明

- 双向通信,响应端需要两个函数,nb_transport和transport,对应了非阻塞和阻塞。并且实例化中,前两个参数是item类型的。

module tcc ();

import uvm_pkg::*;

class my_trans extends uvm_sequence_item;

`uvm_object_utils(my_trans)

int data;

function new(string name="my_trans");

super.new(name);

endfunction : new

endclass : my_trans

class resp_trans extends uvm_sequence_item;

int resp_data;

`uvm_object_utils(resp_trans)

function new(string name="resp_trans");

super.new(name);

endfunction : new

endclass : resp_trans

class Sender extends uvm_component;

uvm_transport_port#(my_trans, resp_trans) tp;

`uvm_component_utils(Sender)

function new(string name="Sender", uvm_component parent);

super.new(name, parent);

tp = new("tp", this);

endfunction : new

endclass : Sender

class Responser extends uvm_component;

uvm_transport_imp#(my_trans, resp_trans, Responser) ti;

`uvm_component_utils(Responser)

function new(string name="Responser", uvm_component parent);

super.new(name, parent);

ti = new("ti", this);

endfunction : new

function void transport(my_trans tr, output resp_trans rtr);

rtr = new("rtr");

`uvm_info("RESP_GET", $sformatf("data value trans: %d", tr.data), UVM_LOW)

rtr.resp_data = 12;

endfunction: transport

function bit nb_transport(my_trans tr, output resp_trans rtr);

rtr = new("rtr");

`uvm_info("RESP_GET_NB", $sformatf("data value trans: %d", tr.data), UVM_LOW)

rtr.resp_data = 23;

return 1;

endfunction: nb_transport

endclass : Responser

class my_test extends uvm_test;

Responser rsper;

Sender sdr;

`uvm_component_utils(my_test)

function new(string name="my_test", uvm_component parent);

super.new(name, parent);

endfunction : new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

rsper = Responser::type_id::create("rspr", this);

sdr = Sender::type_id::create("sdr", this);

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

sdr.tp.connect(rsper.ti);

endfunction

task run_phase(uvm_phase phase);

my_trans tr=new("rt");

resp_trans rtr;

bit status;

tr.data = 1;

phase.raise_objection(this);

sdr.tp.transport(tr, rtr);

`uvm_info("GET_DATA_SENDER", $sformatf("rtr: %d", rtr.resp_data), UVM_LOW)

status = sdr.tp.nb_transport(tr, rtr);

`uvm_info("GET_DATA_NB_SENDER", $sformatf("status %d, rtr: %d",status, rtr.resp_data), UVM_LOW)

phase.drop_objection(this);

endtask: run_phase

endclass : my_test

initial begin

run_test("my_test");

end

endmodule

运行结果

UVM_INFO @ 0: reporter [RNTST] Running test my_test...

UVM_INFO tcc.sv(46) @ 0: uvm_test_top.rspr [RESP_GET] data value trans: 1

UVM_INFO tcc.sv(85) @ 0: uvm_test_top [GET_DATA_SENDER] rtr: 12

UVM_INFO tcc.sv(52) @ 0: uvm_test_top.rspr [RESP_GET_NB] data value trans: 1

UVM_INFO tcc.sv(88) @ 0: uvm_test_top [GET_DATA_NB_SENDER] status 1, rtr: 23

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_objection.svh(1276) @ 0: reporter [TEST_DONE] 'run' phase is ready to proceed to the 'extract' phase

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_catcher.svh(705) @ 0: reporter [UVM/REPORT/CATCHER]

--- UVM Report catcher Summary ---

Number of demoted UVM_FATAL reports : 0

Number of demoted UVM_ERROR reports : 0

Number of demoted UVM_WARNING reports: 0

Number of caught UVM_FATAL reports : 0

Number of caught UVM_ERROR reports : 0

Number of caught UVM_WARNING reports : 0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 0: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 8

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[GET_DATA_NB_SENDER] 1

[GET_DATA_SENDER] 1

[RESP_GET] 1

[RESP_GET_NB] 1

[RNTST] 1

[TEST_DONE] 1

[UVM/RELNOTES] 1

[UVM/REPORT/CATCHER] 1

$finish called from file "/home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_root.svh", line 527.

$finish at simulation time 0

end_of_elaboration_phase说明

说明与代码

该相位会检查之前是否有error_info出现,出现的话会调用fatal_info,然后退出。

而过了该相位在main_phase中的error_info是不会退出的。

module tdd ();

import uvm_pkg::*;

class test_base extends uvm_test;

`uvm_component_utils(test_base)

function new(string name="test_base", uvm_component parent);

super.new(name, parent);

endfunction : new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

`uvm_error("ERROR_INFO", $sformatf("this a err build_phase %m"))

`uvm_info("INFO_TEST", $sformatf("%m a info"), UVM_LOW)

endfunction

task main_phase(uvm_phase phase);

`uvm_error("ERROR_INFO", $sformatf("this a err run_phase %m"))

`uvm_info("INFO_TEST", $sformatf("%m a info"), UVM_LOW)

endtask:main_phase

task post_main_phase(uvm_phase phase);

`uvm_fatal("FATAL_INFO", $sformatf("%m fatal %m"))

`uvm_info("INFO_TEST", $sformatf("%m a info"), UVM_LOW)

endtask: post_main_phase

endclass : test_base

initial begin

run_test("test_base");

end

endmodule

输出结果

UVM_INFO @ 0: reporter [RNTST] Running test test_base...

UVM_ERROR tdd.sv(12) @ 0: uvm_test_top [ERROR_INFO] this a err build_phase tdd.\test_base::build_phase

UVM_INFO tdd.sv(13) @ 0: uvm_test_top [INFO_TEST] tdd.\test_base::build_phase a info

UVM_FATAL @ 0: reporter [BUILDERR] stopping due to build errors

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_catcher.svh(705) @ 0: reporter [UVM/REPORT/CATCHER]

--- UVM Report catcher Summary ---

Number of demoted UVM_FATAL reports : 0

Number of demoted UVM_ERROR reports : 0

Number of demoted UVM_WARNING reports: 0

Number of caught UVM_FATAL reports : 0

Number of caught UVM_ERROR reports : 0

Number of caught UVM_WARNING reports : 0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 0: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 4

UVM_WARNING : 0

UVM_ERROR : 1

UVM_FATAL : 1

** Report counts by id

[BUILDERR] 1

[ERROR_INFO] 1

[INFO_TEST] 1

[RNTST] 1

[UVM/RELNOTES] 1

[UVM/REPORT/CATCHER] 1

$finish called from file "/home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_root.svh", line 135.

$finish at simulation time 0

task phase执行和跳转

要点说明

- phase的跳转前最好是drop当前的phase,否则会有警告。跳转使用phase.jump(uvm_reset_phase::get());其中的uvm_reset_phase可以换成其它phase

- 该程序是一个无限循环的错误程序,默认9200s停止,为了尽快停止,使用uvm_top.set_timeout(200s, 0),0表示不可覆盖。如果为1,则可以在Makefile中传入参数+UVM_TIMEOUT="100s, No",No表示不可覆盖

- +UVM_PHASE_TRACE可以显示phase的轨迹,+UVM_OBJECTION_TRACE可以显示task_phase的raise和drop轨迹

- phase.raise_objection(this, "RESET_PHASE_NAME", 3),默认的中间参数是该raise的名称,而3表示raise的数量,默认是1、通过+UVM_OBJECTION_TRACE可以查看。

- jump的过程,向前可以跳到pre_reset_phase,向后可以跳到final_phase(function phase).

- 在同一timeslot,各个组件的task phase 的启动过程和一般多数的phase相同,是自下而上启动的,运行是并行的。

- build_phase本身过程是一棵树,虽然自上而下,但是内部是深度优先的。

- 在component中,除了build_phase的父类写有内容,其余的如run_phase\connect_phase等等,都是为空的。

module tee ();

import uvm_pkg::*;

class my_test extends uvm_test;

`uvm_component_utils(my_test)

function new(string name="my_test", uvm_component parent);

super.new(name, parent);

endfunction: new

task reset_phase(uvm_phase phase);

phase.raise_objection(this, "RESET_PHASE_NAME", 3);

`uvm_info("RESET_PHASE", $sformatf("%m reset_phase, %t", $time), UVM_LOW)

#10;

phase.drop_objection(this, "RESET_PHASE_NAME", 3);

endtask: reset_phase

task main_phase(uvm_phase phase);

phase.raise_objection(this);

fork

begin

`uvm_info("MAIN_PHASE", $sformatf("%m main_phase %t", $time), UVM_LOW)

#30;

`uvm_info("MAIN_PHASE", $sformatf("%m main_phase %t", $time), UVM_LOW)

end

begin

#10

phase.drop_objection(this);

phase.jump(uvm_reset_phase::get());

end

join

phase.drop_objection(this);

endtask: main_phase

endclass : my_test

initial begin

uvm_top.set_timeout(200s, 0);

run_test("my_test");

end

endmodule

有OBJECTION_TRACE:

点击查看代码

UVM_INFO @ 0: reporter [RNTST] Running test my_test...

UVM_INFO @ 0: reporter [TIMOUTSET] '+UVM_TIMEOUT=100s, YES' provided on the command line is being applied.

UVM_INFO @ 0: reporter [NOTIMOUTOVR] The global timeout setting of 200 is not overridable to 100 due to a previous setting.

UVM_INFO @ 0: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 0: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 0: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 0

UVM_INFO @ 10: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 10: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 10: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 10: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 10: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 10: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 10: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 10

UVM_INFO @ 20: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 20: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 20: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 20: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 20: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 20: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 20: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 20: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 20

UVM_INFO @ 30: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 30: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 30: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 30: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 30: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 30: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 30: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 30

UVM_INFO @ 40: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 40: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 40: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 40: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 40: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 40: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 40: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 40: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 40

UVM_INFO @ 50: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 50: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 50: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 50: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 50: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 50: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 50: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 50

UVM_INFO @ 60: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 60: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 60: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 60: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 60: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 60: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 60: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 60: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 60

UVM_INFO @ 70: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 70: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 70: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 70: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 70: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 70: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 70: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 70

UVM_INFO @ 80: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 80: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 80: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 80: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 80: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 80: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 80: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 80: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 80

UVM_INFO @ 90: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 90: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 90: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 90: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 90: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 90: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 90: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 90

UVM_INFO @ 100: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 100: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 100: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 100: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 100: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 100: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 100: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 100: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 100

UVM_INFO @ 110: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 110: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 110: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 110: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 110: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 110: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 110: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 110

UVM_INFO @ 120: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 120: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 120: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 120: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 120: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 120: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 120: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 120: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 120

UVM_INFO @ 130: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 130: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 130: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 130: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 130: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 130: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 130: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 130

UVM_INFO @ 140: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 140: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 140: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 140: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 140: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 140: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 140: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 140: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 140

UVM_INFO @ 150: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 150: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 150: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 150: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 150: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 150: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 150: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 150

UVM_INFO @ 160: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 160: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 160: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 160: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 160: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 160: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 160: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 160: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 160

UVM_INFO @ 170: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 170: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 170: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 170: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 170: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 170: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 170: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 170

UVM_INFO @ 180: main_objection [OBJTN_TRC] Object uvm_test_top dropped 1 objection(s): count=0 total=0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 180: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO @ 180: main_objection [OBJTN_TRC] Object uvm_test_top all_dropped 1 objection(s): count=0 total=0

UVM_INFO @ 180: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 180: main_objection [OBJTN_TRC] Object uvm_top subtracted 1 objection(s) from its total (all_dropped from source object uvm_test_top): count=0 total=0

UVM_INFO @ 180: reset_objection [OBJTN_TRC] Object uvm_test_top raised 3 objection(s) (RESET_PHASE_NAME): count=3 total=3

UVM_INFO @ 180: reset_objection [OBJTN_TRC] Object uvm_top added 3 objection(s) to its total (raised from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=3

UVM_INFO tee.sv(13) @ 180: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 180

UVM_INFO @ 190: reset_objection [OBJTN_TRC] Object uvm_test_top dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 190: reset_objection [OBJTN_TRC] Object uvm_test_top all_dropped 3 objection(s) (RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 190: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 190: reset_objection [OBJTN_TRC] Object uvm_top subtracted 3 objection(s) from its total (all_dropped from source object uvm_test_top, RESET_PHASE_NAME): count=0 total=0

UVM_INFO @ 190: main_objection [OBJTN_TRC] Object uvm_test_top raised 1 objection(s): count=1 total=1

UVM_INFO @ 190: main_objection [OBJTN_TRC] Object uvm_top added 1 objection(s) to its total (raised from source object uvm_test_top): count=0 total=1

UVM_INFO tee.sv(22) @ 190: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 190

UVM_FATAL /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1510) @ 200: reporter [PH_TIMEOUT] Explicit timeout of 200 hit, indicating a probable testbench issue

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_catcher.svh(705) @ 200: reporter [UVM/REPORT/CATCHER]

--- UVM Report catcher Summary ---

Number of demoted UVM_FATAL reports : 0

Number of demoted UVM_ERROR reports : 0

Number of demoted UVM_WARNING reports: 0

Number of caught UVM_FATAL reports : 0

Number of caught UVM_ERROR reports : 0

Number of caught UVM_WARNING reports : 0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 200: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 150

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 1

** Report counts by id

[MAIN_PHASE] 10

[NOTIMOUTOVR] 1

[OBJTN_TRC] 116

[PH_JUMP] 9

[PH_TIMEOUT] 1

[RESET_PHASE] 10

[RNTST] 1

[TIMOUTSET] 1

[UVM/RELNOTES] 1

[UVM/REPORT/CATCHER] 1

$finish called from file "/home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_root.svh", line 135.

$finish at simulation time 200

没有OBJECTION_TRACE:

点击查看代码

UVM_INFO @ 0: reporter [RNTST] Running test my_test...

UVM_INFO tee.sv(13) @ 0: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 0

UVM_INFO tee.sv(22) @ 10: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 10

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 20: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 20: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 20

UVM_INFO tee.sv(22) @ 30: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 30

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 40: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 40: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 40

UVM_INFO tee.sv(22) @ 50: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 50

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 60: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 60: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 60

UVM_INFO tee.sv(22) @ 70: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 70

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 80: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 80: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 80

UVM_INFO tee.sv(22) @ 90: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 90

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 100: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 100: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 100

UVM_INFO tee.sv(22) @ 110: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 110

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 120: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 120: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 120

UVM_INFO tee.sv(22) @ 130: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 130

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 140: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 140: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 140

UVM_INFO tee.sv(22) @ 150: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 150

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 160: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 160: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 160

UVM_INFO tee.sv(22) @ 170: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 170

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1556) @ 180: reporter [PH_JUMP] phase main (schedule uvm_sched, domain uvm) is jumping to phase reset

UVM_INFO tee.sv(13) @ 180: uvm_test_top [RESET_PHASE] tee.\my_test::reset_phase reset_phase, 180

UVM_INFO tee.sv(22) @ 190: uvm_test_top [MAIN_PHASE] tee.\my_test::main_phase main_phase 190

UVM_FATAL /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_phase.svh(1510) @ 200: reporter [PH_TIMEOUT] Explicit timeout of 200 hit, indicating a probable testbench issue

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_catcher.svh(705) @ 200: reporter [UVM/REPORT/CATCHER]

--- UVM Report catcher Summary ---

Number of demoted UVM_FATAL reports : 0

Number of demoted UVM_ERROR reports : 0

Number of demoted UVM_WARNING reports: 0

Number of caught UVM_FATAL reports : 0

Number of caught UVM_ERROR reports : 0

Number of caught UVM_WARNING reports : 0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 200: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 32

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 1

** Report counts by id

[MAIN_PHASE] 10

[PH_JUMP] 9

[PH_TIMEOUT] 1

[RESET_PHASE] 10

[RNTST] 1

[UVM/RELNOTES] 1

[UVM/REPORT/CATCHER] 1

$finish called from file "/home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_root.svh", line 135.

$finish at simulation time 200

task的域domain

要点说明

- 默认的时间域为common_domain

- uvm_domain定义出一个domain,实例化以后,可以设置:set_domain(domain_name)

- uvm_domain的类型继承于uvm_phase,继承于uvm_object,继承于uvm_void

- 在不同的领域下,则其中的task_phase内的小phase是异步的。而run_phase、以及其它的function phase,仍然是是同步的。

- 调用在connect_phase中,是要等组件们都实例化。默认的set_domain有第二的参数hier,默认是继承的,为1.

module tff ();

import uvm_pkg::*;

class my_env1 extends uvm_component;

`uvm_component_utils(my_env1)

function new(string name="my_env1", uvm_component parent);

super.new(name, parent);

endfunction: new

task reset_phase(uvm_phase phase);

phase.raise_objection(this);

#10;

`uvm_info("RESET_PH", $sformatf("10 is finish"), UVM_LOW)

phase.drop_objection(this);

endtask: reset_phase

endclass : my_env1

class my_env2 extends uvm_component;

`uvm_component_utils(my_env2)

uvm_domain env2_domain;

function new(string name="my_env2", uvm_component parent);

super.new(name, parent);

env2_domain = new("env2_domain_name");

endfunction: new

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

set_domain(env2_domain);

endfunction:connect_phase

task reset_phase(uvm_phase phase);

#1;

`uvm_info("ENV2_RESET", $sformatf("1 is finish"), UVM_LOW)

endtask: reset_phase

endclass : my_env2

class base_test extends uvm_test;

`uvm_component_utils(base_test)

my_env1 env1;

my_env2 env2;

function new(string name="base_test", uvm_component parent);

super.new(name, parent);

endfunction: new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

env1 = my_env1::type_id::create("env1", this);

env2 = my_env2::type_id::create("env2", this);

endfunction: build_phase

endclass : base_test

initial begin

run_test("base_test");

end

endmodule

输出结果为

注释掉set_domain(env2_domain);,则不同。

UVM_INFO @ 0: reporter [RNTST] Running test base_test...

UVM_INFO tff.sv(15) @ 10: uvm_test_top.env1 [RESET_PH] 10 is finish

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_catcher.svh(705) @ 10: reporter [UVM/REPORT/CATCHER]

--- UVM Report catcher Summary ---

Number of demoted UVM_FATAL reports : 0

Number of demoted UVM_ERROR reports : 0

Number of demoted UVM_WARNING reports: 0

Number of caught UVM_FATAL reports : 0

Number of caught UVM_ERROR reports : 0

Number of caught UVM_WARNING reports : 0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 10: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 4

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[RESET_PH] 1

[RNTST] 1

[UVM/RELNOTES] 1

[UVM/REPORT/CATCHER] 1

$finish called from file "/home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_root.svh", line 527.

$finish at simulation time 10

sequence发送

要点说明

- uvm_do_on_pri_with(trans, seqr, weight, constraint),可以去掉on、pri,或者with,都是发送的宏。分别表示了发送的内容,由谁发送,发送权重,以及约束。

- pri是优先级,默认优先级为-1,为低,数字越高则优先级越高。

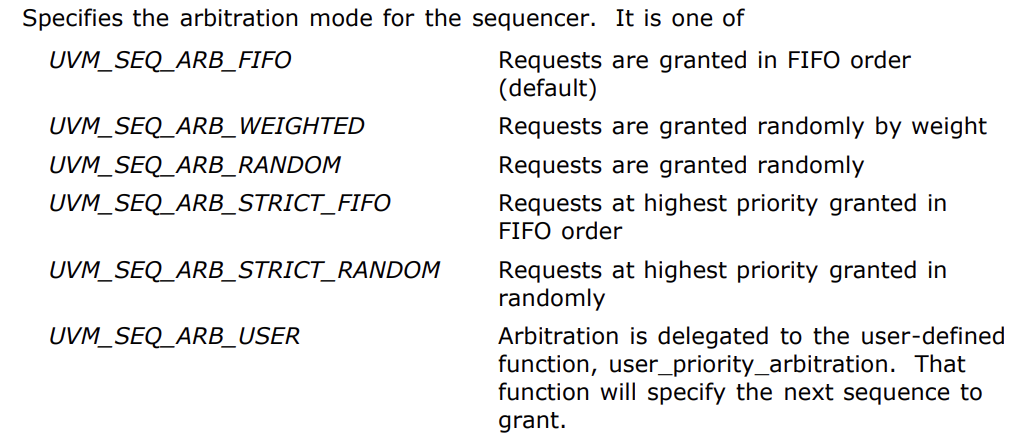

- seq并行发送的时候,默认是fifo形式的,即不考虑优先级,不考虑随机性等。

- seqr.set_arbitration()设置一个seqr上有多个seq发送的仲裁算法,UVM1.2变更了该方法为:添加了UVM_前缀。

- 其中的STRICT可以实现优先级控制,RANDOM完全随机,WEIGHT考虑权重。严格的FIFO、严格RANDOM,使得优先级更高的一直先发送。

- seqr内部是一个fifo的,而seq发送的时候按照该fifo顺序。

- lock、unlock用于锁定,在该seq_item到达后获得对seqr的独享权限,直到释放。

- grab、ungrab用于锁定,直接放到seqr的fifo队列最前,获得独享后,直到释放。

- function is_relevant 是在每次发送前检查的,返回值是0则该seq失效,不再发送。

- task wait_for_relevant和is_relevant配合,等到所有seq失效或者发送完,执行该函数,然后使得失效的seq重新生效。

- 必须使得is_relevant重新生效,否则该失效一直持续,则一直执行wait_for_relevant可能导致死循环(可能)

- uvm_create宏用于实例化seq_item,uvm_send_pri用于带着优先级发送。而添加约束则需要uvm_rand_send_pri_with,带着优先级和约束。uvm_create可以使用new替代,使用这样而不是uvm_do_on_pri_with的整套宏,可以使用randc等的方式,用同一块内存。

- uvm_send的本质上是uvm_do去掉了实例化过程(手册1.2)

- uvm_do的宏,包括了start_item\finish_item两个步骤。而其中的start_item有两个task,后一个task是pre_do。finish_item有一些function和task,最前的是function的mid_do,最后的是function的post_do

module tgg ();

import uvm_pkg::*;

class my_trans extends uvm_sequence_item;

rand int data;

`uvm_object_utils(my_trans)

function new(string name="my_trans");

super.new(name);

endfunction: new

endclass: my_trans

class my_seq1 extends uvm_sequence#(my_trans);

`uvm_object_utils(my_seq1)

my_trans mtr;

bit pre_mid_post=0;

function new(string name="my_seq1");

super.new(name);

endfunction: new

task body();

lock();

/* grab(); */

repeat (5) begin

`uvm_do_pri_with(mtr, 100, {data==1;})

end

unlock();

/* ungrab(); */

repeat (4) begin

`uvm_create(mtr);

`uvm_rand_send_pri_with(mtr, 100, {data==1;})

end

pre_mid_post = 1;

mtr = new("mtr");

start_item(mtr);

mtr.randomize() with {data==1;};

finish_item(mtr);

endtask: body

task pre_do(bit is_item);

if (pre_mid_post) begin

`uvm_info("PRE_DO", $sformatf("vaule param is %d", is_item), UVM_LOW)

end

endtask: pre_do

function void mid_do(uvm_sequence_item this_item);

my_trans mtr;

if (pre_mid_post) begin

$cast(mtr, this_item);

mtr.data +=10;

`uvm_info("MID_DO", $sformatf("value param is %d", mtr.data), UVM_LOW)

end

endfunction: mid_do

function void post_do(uvm_sequence_item this_item);

my_trans mtr;

if (pre_mid_post) begin

$cast(mtr, this_item);

`uvm_info("POST_DO", $sformatf("value param is %d", mtr.data), UVM_LOW)

end

endfunction: post_do

endclass: my_seq1

class my_seq2 extends uvm_sequence#(my_trans);

`uvm_object_utils(my_seq2)

my_trans mtr;

int count=0;

function new(string name="my_seq2");

super.new(name);

endfunction: new

task body();

repeat (20) begin

`uvm_do_on_pri_with(mtr, this.m_sequencer, 500, {data==2;});

count++;

end

endtask: body

function bit is_relevant();

if (count>=10) begin

return 0;

/* return 1; */

end else begin

return 1;

end

endfunction: is_relevant

task wait_for_relevant();

#2;

count = 0;

endtask: wait_for_relevant

endclass: my_seq2

typedef uvm_sequencer#(my_trans) my_seqr;

class my_drv extends uvm_driver#(my_trans);

`uvm_component_utils(my_drv)

function new(string name="my_drv", uvm_component parent);

super.new(name, parent);

endfunction: new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

endfunction: build_phase

task run_phase(uvm_phase phase);

my_trans mtr;

forever begin

seq_item_port.get_next_item(mtr);

`uvm_info("GET_DATA", $sformatf("%t, message %d",$time, mtr.data), UVM_LOW)

seq_item_port.item_done();

end

endtask: run_phase

endclass: my_drv

class my_test extends uvm_test;

my_seqr seqr;

my_drv drv;

`uvm_component_utils(my_test)

function new(string name="my_test", uvm_component parent);

super.new(name, parent);

endfunction: new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

seqr = my_seqr::type_id::create("seqr", this);

drv = my_drv::type_id::create("drv", this);

/* seqr.set_arbitration(UVM_SEQ_ARB_STRICT_FIFO); */

/* seqr.set_arbitration(UVM_SEQ_ARB_RANDOM); */

seqr.set_arbitration(UVM_SEQ_ARB_WEIGHTED);

/* seqr.set_arbitration(UVM_SEQ_ARB_STRICT_RANDOM); */

endfunction: build_phase

function void connect_phase(uvm_phase phase);

drv.seq_item_port.connect(seqr.seq_item_export);

endfunction: connect_phase

task run_phase(uvm_phase phase);

my_seq1 seq1 = new("seq1");

my_seq2 seq2 = new("seq2");

phase.raise_objection(this);

fork

seq2.start(seqr);

seq1.start(seqr);

join

#10;

phase.drop_objection(this);

endtask: run_phase

endclass: my_test

initial begin

run_test("my_test");

end

endmodule

输出结果

- 2的优先级高,先发送,但是1有lock,所以等到fifo后独占,如果是grab,则直接独占。

- 显示了pre_do\mid_do\post_do的过程,参数为is_item, this_item, this_item,用的时候需要cast转化。

- 2因为num计数达到,先发送,但是到10个就失效了,

- 等到时间为2的时候,生效,继续发送。

UVM_INFO @ 0: reporter [RNTST] Running test my_test...

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 2

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 1

UVM_INFO tgg.sv(43) @ 0: uvm_test_top.seqr@@seq1 [PRE_DO] vaule param is 1

UVM_INFO tgg.sv(52) @ 0: uvm_test_top.seqr@@seq1 [MID_DO] value param is 11

UVM_INFO tgg.sv(112) @ 0: uvm_test_top.drv [GET_DATA] 0, message 11

UVM_INFO tgg.sv(60) @ 0: uvm_test_top.seqr@@seq1 [POST_DO] value param is 11

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO tgg.sv(112) @ 2: uvm_test_top.drv [GET_DATA] 2, message 2

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_objection.svh(1276) @ 12: reporter [TEST_DONE] 'run' phase is ready to proceed to the 'extract' phase

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_catcher.svh(705) @ 12: reporter [UVM/REPORT/CATCHER]

--- UVM Report catcher Summary ---

Number of demoted UVM_FATAL reports : 0

Number of demoted UVM_ERROR reports : 0

Number of demoted UVM_WARNING reports: 0

Number of caught UVM_FATAL reports : 0

Number of caught UVM_ERROR reports : 0

Number of caught UVM_WARNING reports : 0

UVM_INFO /home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 12: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 37

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[GET_DATA] 30

[MID_DO] 1

[POST_DO] 1

[PRE_DO] 1

[RNTST] 1

[TEST_DONE] 1

[UVM/RELNOTES] 1

[UVM/REPORT/CATCHER] 1

$finish called from file "/home/synopsys/vcs-mx/O-2018.09-1/etc/uvm-1.2/base/uvm_root.svh", line 527.

$finish at simulation time 12

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号