日常记录(21)赋值assign与strboe

赋值assign与strboe

在行为级里,如initial里,reg类型(wire不行)可以使用assign和deassign语句强制赋值和释放。也可以使用force和release语句强制赋值和释放。

task的output类型,当在module里调用该task,应该传递reg类型变量,wire则不行

module tee ();

reg a1;

wire a2;

task tax;

output reg a;

assign a=0;

endtask

initial begin

tax(a1);

tax(a1);

end

endmodule

P83:于斌,Verilog HDL

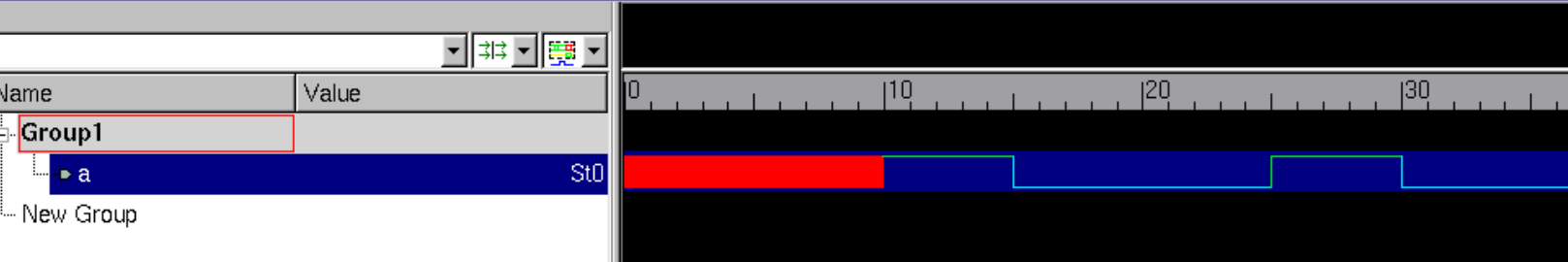

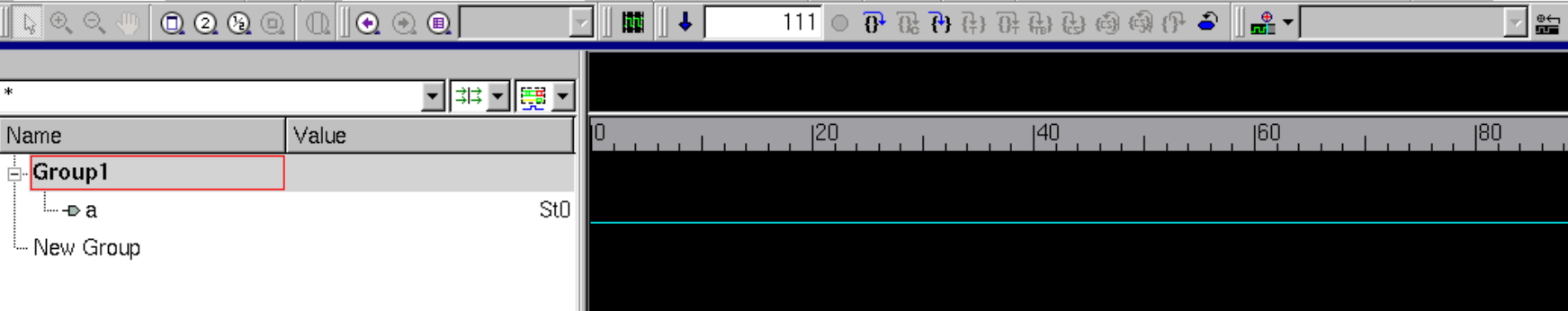

在行为级建模,assgn语句的优先级可能更高。(vcs仿真环境)以下的代码中,是按照延时输出的。然而取消那句assign的注释,则仿真结果从开始到结束为0(物理连线)。

module tee ();

reg a1;

wire a2;

task tax;

output reg a;

//assign a=0;

#10 a=1;

#5 a=0;

endtask

initial begin

tax(a1);

tax(a1);

assign a1=1;

end

assign a2=1;

endmodule

automatic的使用,自动获取新的空间,使得可重入

原始:https://blog.csdn.net/xuhuihw/article/details/82781839

以下是function和task的使用方法,计算阶乘的过程中,若没有automatic,则输出值都为1,因为最后一层的op参数,将上层堆栈空间的op覆盖为了1,那肯定不行

module tryfact;

function integer factorial (input [31:0] operand);

if (operand >= 2)

factorial = factorial (operand - 1) * operand;

else

factorial = 1;

endfunction: factorial

task automatic factor();

input [31:0] op;

output [31:0] fact;

if(op>=2)

begin

factor(op-1, fact);

fact=fact*op;

end

else

fact=1;

endtask: factor

integer result;

initial begin

for (int n = 0; n <= 7; n++) begin

result = factorial(n);

$display("%0d factorial=%0d", n, result);

end

end

integer result2;

initial begin

for (int nx = 0; nx <= 7; nx++) begin

factor(nx, result2);

$display("%0d task factor=%0d", nx, result2);

end

end

endmodule: tryfact

strobe

integer在外面,行为级里面,那个是sv的语法,不是Verilog的

module ssx ();

integer a=1;

initial begin

$display("disp ans is %d", a);

$strobe("strobe ans is %d", a);

a=2;

$display("disp ans is %d", a);

$strobe("strobe ans is %d", a);

end

endmodule

输出结果:

display实时输出,strobe在当前时刻结束后,对值进行统一输出。

disp ans is 1 disp ans is 2 strobe ans is 2 strobe ans is 2

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号