ARM Security Technology - Building a Secure System using TrustZone Technology

关键词:TrustZone、AMBA3 AXI、AXI-to-APB、Monitor Mode、SMC、SCR NS、CP15、TZAPI等等。

参考文档:《ARM Security Technology Building a Secure System using TrustZone Technology》

Chapter 1首先介绍什么是安全?有哪些威胁?需要做哪些工作才能确保安全?

Chapter 2接着介绍了常见系统安全方案?以及TrustZone的硬件安全方案?

Chapter 3然后详细介绍了TrustZone硬件架构:系统架构、处理器架构、调试架构。

Chapter 4罗列了涉及到的所有IP。

在介绍了硬件架构之后,Chapter 5介绍了软件架构:安全启动、Monitor Mode、多处理器安全、TrustZone API等。

最后Chapter 6介绍了一个Gadget2008示例。

Chapter 1 Introduction

Class-breaking attacks:是指一种可复制的攻击,往往是指对同一类设备。

Hack attack:仅可进行软件攻击,包括病毒和恶意软件等。

Shack attack:指低成本硬件攻击,攻击设备较易获取。攻击者往往可以接触设备,但是没有专业设备或专业知识对IC进行攻击。

Lab attack:最复杂最具破坏性的,可以借助实验室设备对设备进行逆向工程。

Chapter 2 SystemSecurity

2.1 System security

常见三种系统安全方案:External hardware security module、Internal hardware security module、Software virtualization,及其优缺点对比。

2.2 TrustZone hardware security

保护关键Key的必须安全模块Cryptographic hardware blocks。

基于TrustZone架构实现安全启动、经过验证的调试。

Chapter 3 TrustZone Hardware Architecture

3.2 System architecture

AMBA3 AXI为每个读写通道增加了控制信号,表示Non-Secure或者Secure状态。

AWPROT[1]: Write transaction – low is Secure and high is Non-secure. ARPROT[1]: Read transaction – low is Secure and high is Non-secure.

所有总线主设备发起传输前必须这是这些信号,总线或者从设备解码逻辑必须符合安全规则。

AXI-to-APB桥提供了APB外设兼容TrustZone安全技术的能力。

总线传输上的NS位,可以看成是第33给地址位:安全传输32位地址空间,非安全传输32位地址空间。

3.3 Processor architecture

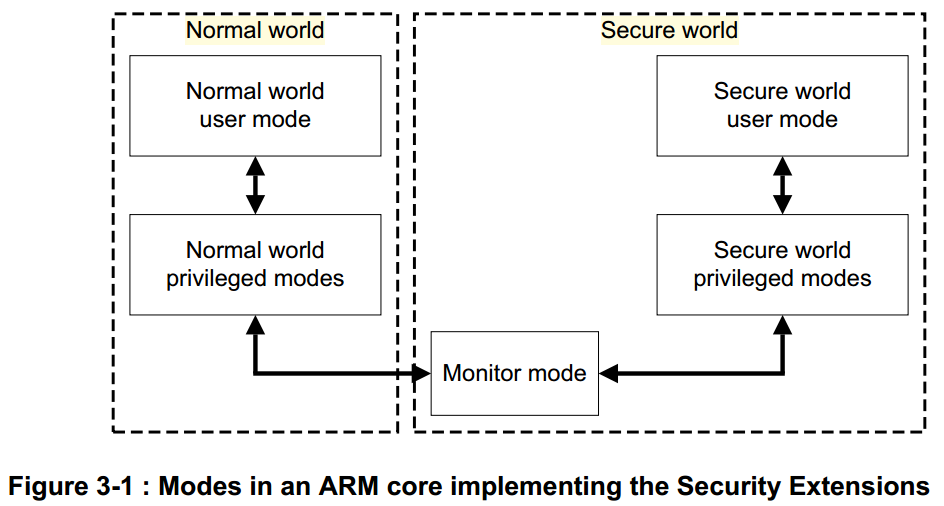

每个物理核被虚拟成两个核:一个安全核、一个非安全核。这两个核的切换由Monitor mode负责。

非安全核仅能看到非安全系统资源;安全核可以看到所有资源。

安全世界和非安全世界切换

两个虚拟核通过分时使用物理核实现,他们之间的切换由Monitor Mode负责。

触发进入Monitor Mode的手段有:SMC、IRQ、FIQ、external Data Abort、external Prefetch Abort。

CP15的SCR寄存器NS位表示当前安全还是非安全世界执行。

L1内存系统安全

MMU、Caches、TCM、ACP(Accelerator Coherence Port)。

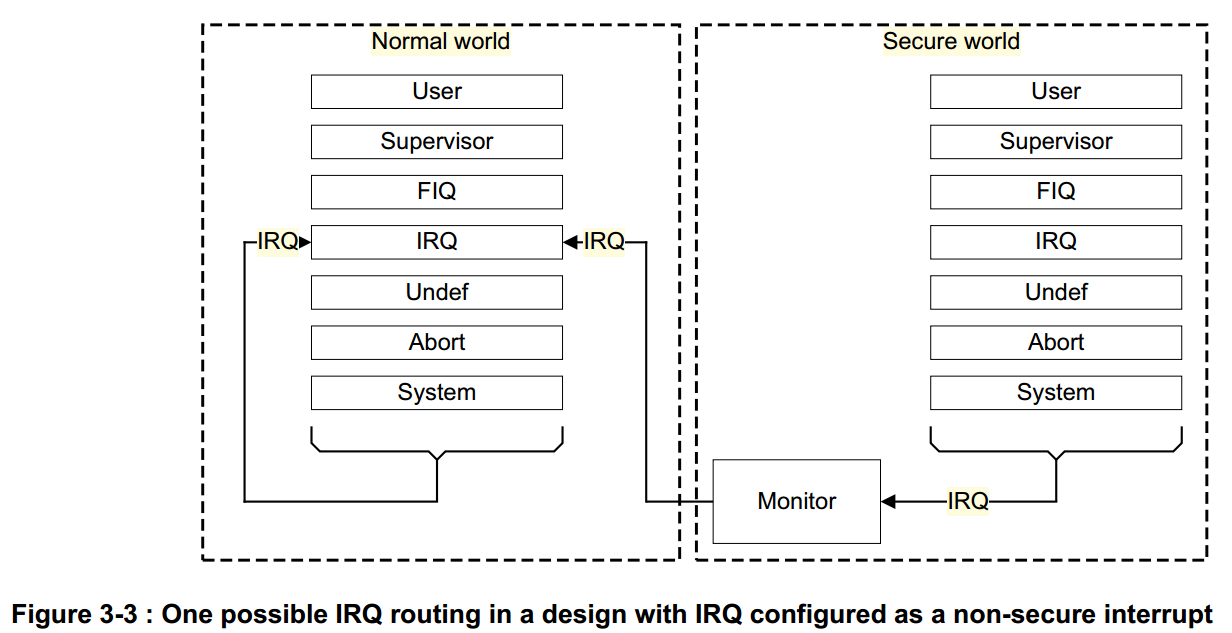

中断安全

ARM建议IRQ作为普通世界中断源,FIQ作为安全世界中断源。

如果当前CPU运行在对应安全状态,中断产生后不会导致Monitor Mode切换。反之,则会导致上下文切换,并且跳转到另一个世界执行。

处理器异常向量表包含三组:普通世界、安全世界、Monitor Mode。

安全处理器配置

CP15

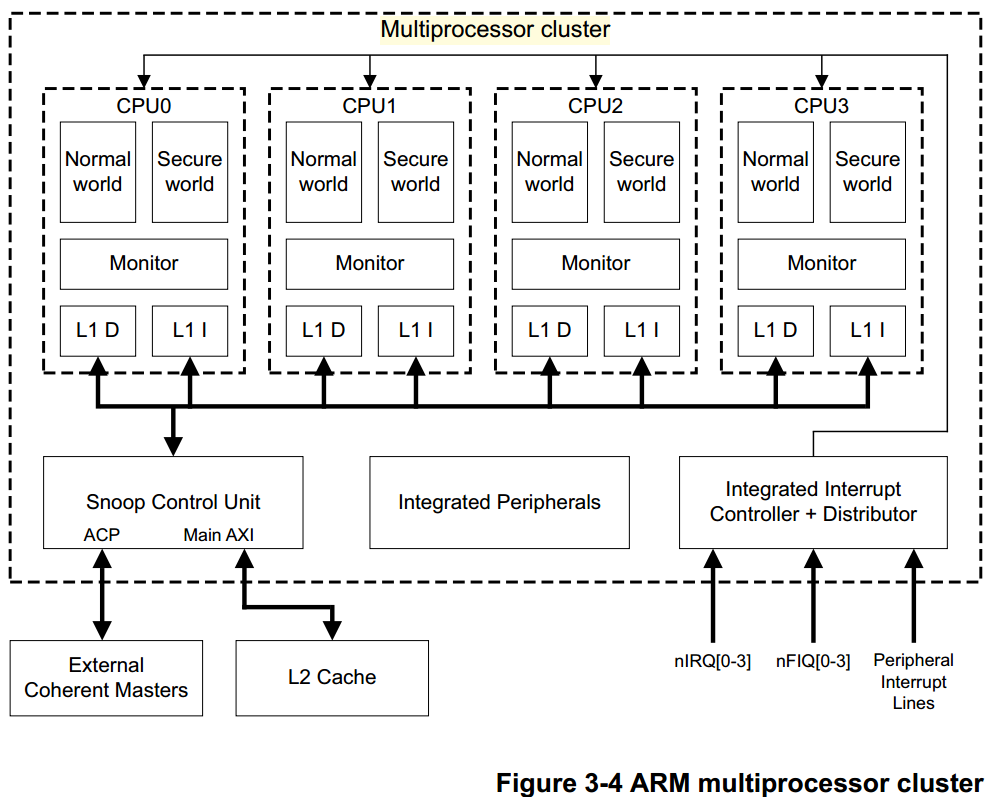

多核处理器安全

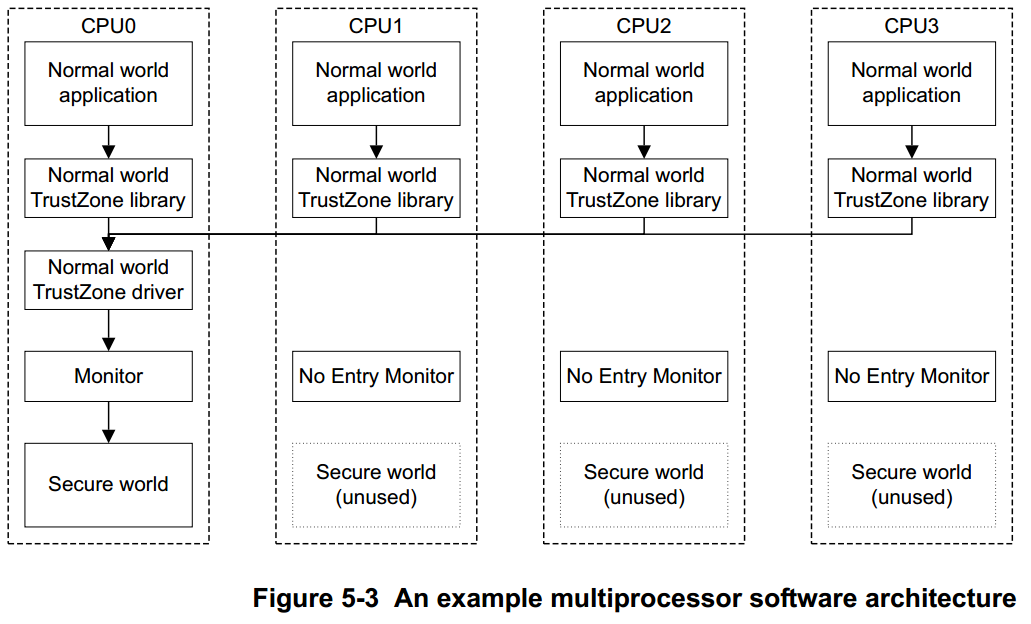

多核处理器中每个物理核都包含一个普通世界虚拟核和一个安全世界虚拟核。

如下1个cluster的4核CPU,被虚拟成8个核。

3.4 Debug architecture

ARM的调试解决方案可以分为两部分:处理器调试和系统调试。

Processor debug control

TrustZone调试将调试介入控制分成独立配置的4部分:

- Secure privileged invasive (JTAG) debug - SPIDEN

- Secure privileged non-invasive (trace) debug - SPNIDEN

- Secure user invasive debug - SUIDEN

- Secure user non-invasive debug - SUNIDEN

Multiprocessor debug control

Cluster中每个核都包含独立的DBGEN、NIDEN、SPIDEN和SPNIDEN。

Performance analysis

CP15中包含Performance Monitor。

System debug control

ARM CoreSight是系统调试解决方案,可用于调试或跟踪处理器和其他系统组件。

Chapter 4 TrustZone Hardware Library

4.1 System IP

4.1.1 Matrix

PrimeCell® High-Performance Matrix - PL301:实现AMBA3 AXI总线,对系统安全和非安全进行系统范围的隔离。

4.1.2 Cache Controller

PrimeCell Level 2 Cache Controller - PL310:L2缓存,标记每个cache line的安全状态。

4.1.3 DMA Controller

PrimeCell DMA Controller - PL330:实现安全世界和非安全世界并发工作。

4.1.4 TZASC

PrimeCell TrustZone Address Space Controller - PL380:将一段存储区域划分为若干安全和或非安全区。

TZASC作为一个AXI组件将其从属地址空间划分成一系列安全或非安全内存空间。TZASC仅可由安全软件进行编程,并拒绝非安全传输到一个配置为安全的区域。

4.1.5 TZMA

PrimeCell Infrastructure AMBA3 AXI TrustZone Memory Adapter - BP141:将片内ROM和STAM一段内存设置为安全区域和非安全区域。

TZMA用于配置SOC片内静态内存(ROM/SRAM)为安全区域。将一块较大内存配置为安全和非安全区域的成本要低于为每个区域使用独立的内存。

TZMA允许将一块最大2MB内存配置为两个区域,低地址为安全区,高地址为非安全区。

安全区和非安全区一般以4KB为单位,可以通过送到TZMA的信号R0SIZE配置。

R0ZISE可由TZPC一个外设发出的TZPCR0ZISE进行动态设置。

TZMA不能用于对动态内存分区;或超过一个安全区的情况,此时可由TZASC进行配置。

4.1.6 GIC

PrimeCell Generic Interrupt Controller - PL390:设置安全或非安全中断。

GIC同时支持安全和非安全世界的支持优先级的中断源。

4.1.7 TZPC

PrimeCell Infrastructure AMBA3 TrustZone Protection Controller - BP147:是APB总线具备安全设置功能。

TZPC挂载于APB总线上,用于提供控制信号给其他设备。

4.2 Processor IP

介绍可以作为智能卡安全核的处理器,也可以和TrustZone核结合使用,提供更高安全性能。

Chapter 5 TrustZone Software Architecture

5.1 Software overview

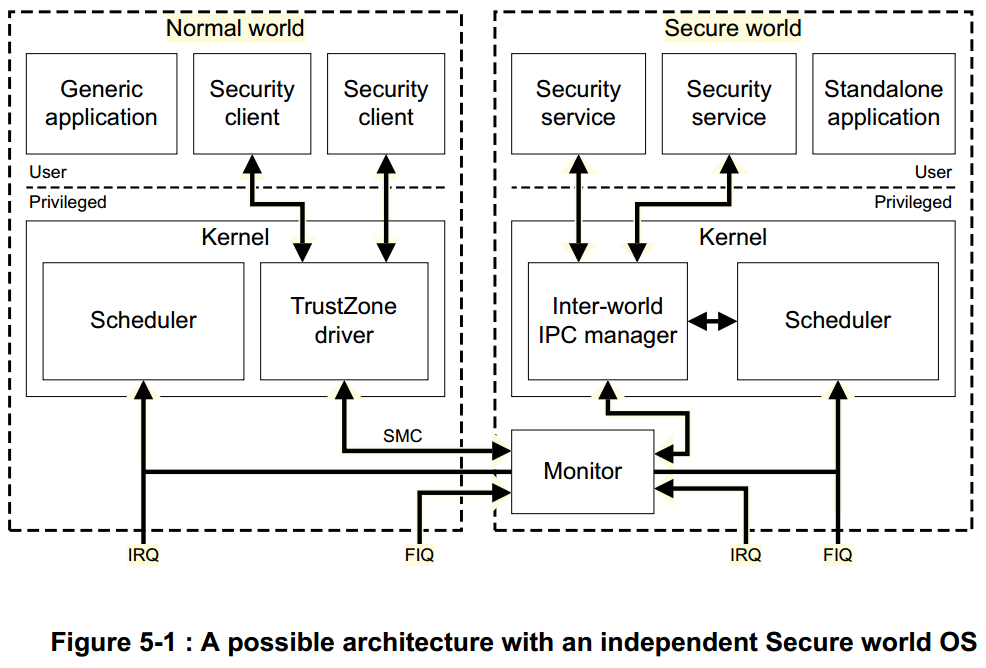

实现TrustZone功能两种软件结构:安全OS和同步库调用。

安全OS缺点是复杂,但是功能更强大。可以模拟实现安全应用并发执行、使用MMU对不同安全应用形成隔离等等。

同步库函数调用实现简单,但是每次技能处理一个安全相关任务、库函数完全被普通世界操作系统通过SMC调用和管理、安全世界不能独立执行。

5.2 Booting a secure system

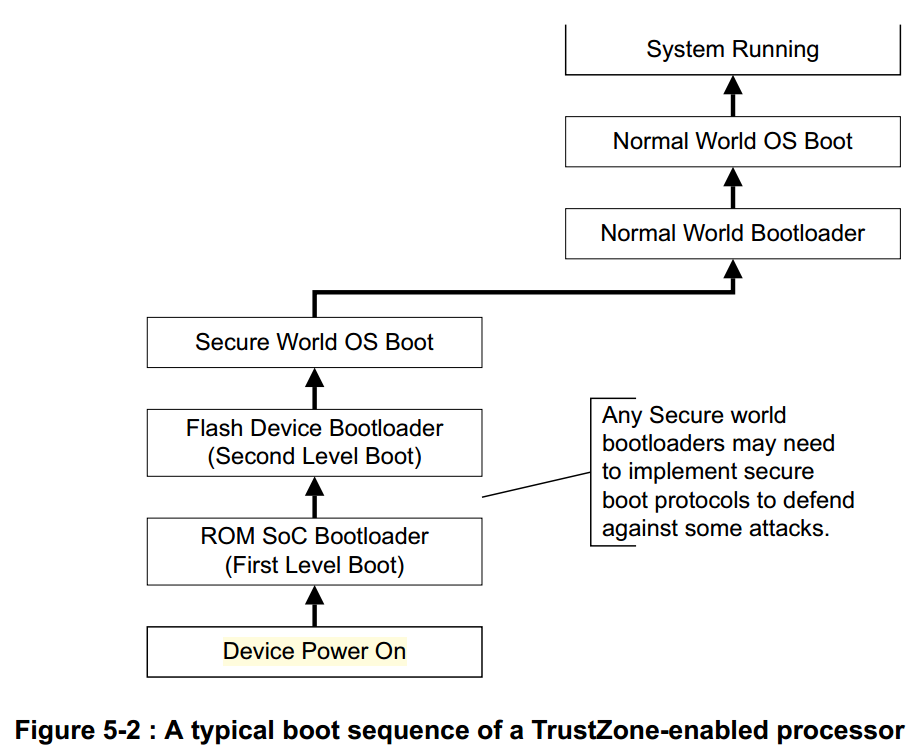

启动流程

启动过程是一个系统安全的关键点,可以通过更改镜像文件实现系统进行攻击。所以在启动过程中对镜像进行验证是必要的。

所以从Bootrom启动开始,每一步进行安全检查,直到所有安全世界和普通世界运行,形成一个完成的信任链。

一个典型的TrustZone处理器启动流程:

BootRom:负责初始化关键外设,比如初始化外部存储控制器并从中读取二级Bootloader。这里需要对二级Bootlader的合法性进行验证,通过后才能跳转到二级Bootlaoder。

二级Bootloader:负责加载并验证安全OS,通过后启动安全OS。

安全OS:负责启动普通世界OS。

安全启动

安全启动从BootRom开始对启动每个阶段,对每个镜像文件基于密码的检查,杜绝未授权或恶意修改。

加密签名协议:使用PrK对镜像生成一个签名,并且和二进制软件一同发布;设备中存有相应的PuK,PuK可用于验证二进制文件是否被修改。

所有阶段镜像在执行之前必须被验证,才能确保形成完整的启动流程信任链。

5.3 Monitor mode software

模式监控软件管理CPU在安全和非安全状态切换,类似于进程切换:保存将要退出CPU状态,恢复将要进入CPU状态。

普通世界进入模式监控可以通过如下手段:interrupt、external abort、SMC;安全世界进入模式监控通过写CPSR寄存器。

安全模式软件是安全世界和普通世界切换的纽带,一般建议执行期间关闭中断使能。

模式监控上下文切换

模式监控上下文切换需要保存的信息有:

- 所有ARM通用寄存器

- 所有协处理器,比如NEON或VFP等。

- 所有CP15中不同世界独立配置寄存器。

硬件异常:IRQ、FIQ、external abort。

软件异常:SMC。

Lazy context switching:针对VFP和NEON状态保存消耗大的设备。

5.4 Secure software and multiprocessor systems

安全世界的执行会降低普通世界调度效率,可以通过将所有的安全任务仅在一个核上运行。

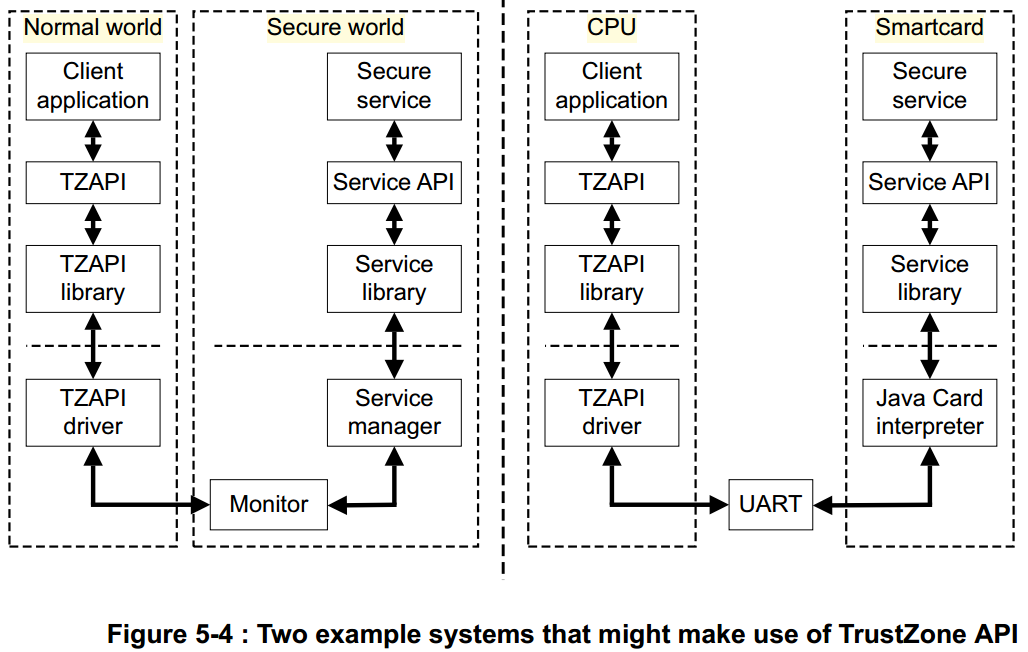

5.5 TrustZone API

通过TZAPI,非安全世界客户端发送命令到安全世界请求服务。

Chapter 6 TrustZone System Design

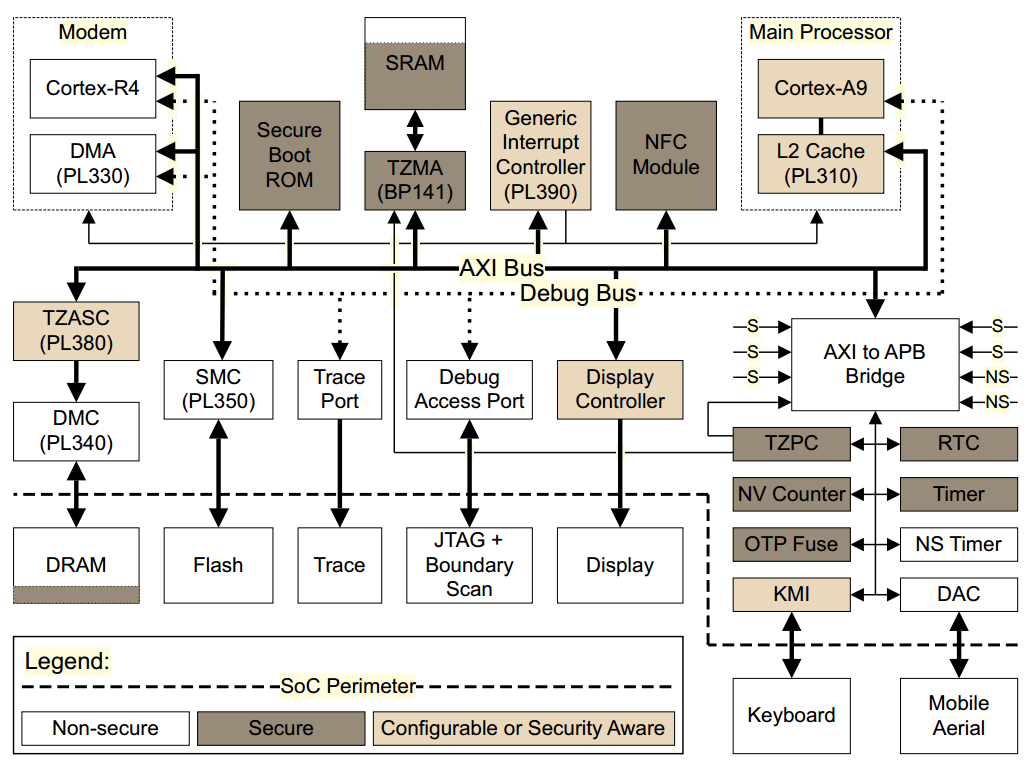

一个名为Gadget2008 SOC安全设计方案介绍。

6.3.4 Putting the hardware together

TZASC在AXI总线和DMC中间,对DRAM进行安全和非安全多区域划分。如何划分?对齐地址是多少?最多多少个分区?

TZMA在AXI总线和SRAM之间,仅能划分成安全和分安全两个分区。还可由TZPC对分区进行动态调整。

TZPC对外设安全进行控制。

BootROM/NV Counter/OTP完全位于安全区,SRAM可以划分成安全和非安全两个区。

GIC可以被安全或非安全中断源。

浙公网安备 33010602011771号

浙公网安备 33010602011771号