创龙 瑞芯微 RK3588 国产2.4GHz八核 工业开发板—视频图像处理框架

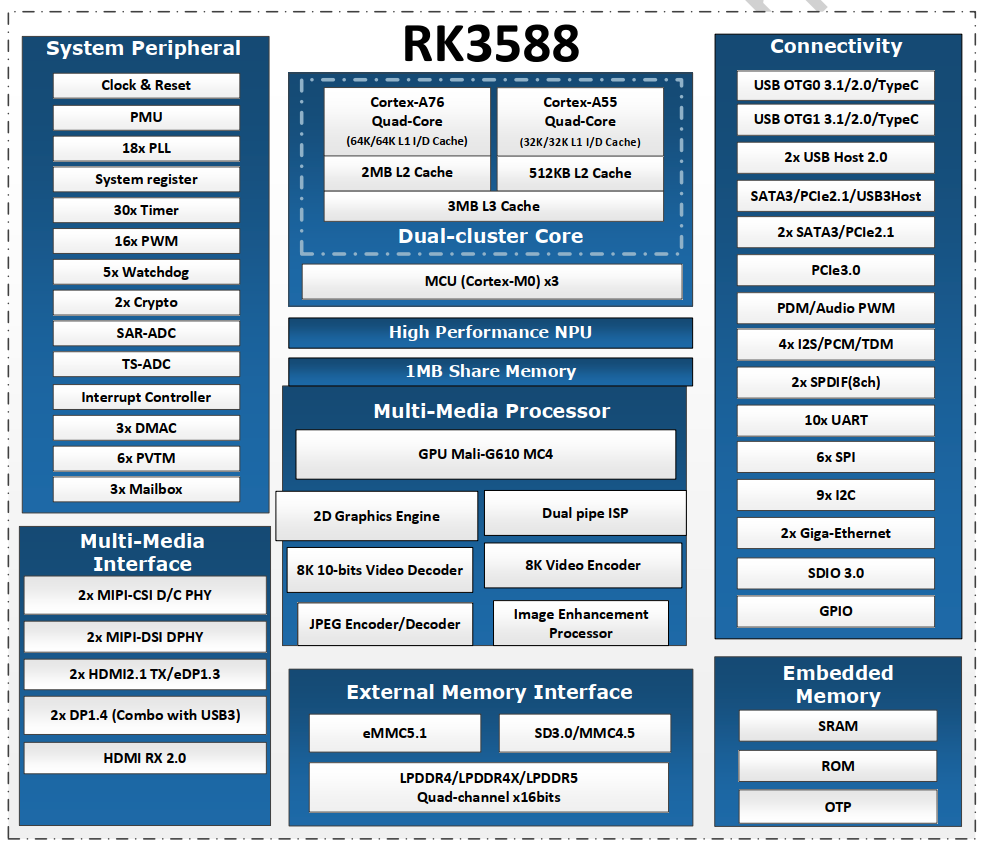

RK3588/RK3588J SoC

本文围绕创龙科技研发的 TL3588-EVM 评估板及 SOM-TL3588 核心板,介绍基于 RK3588/RK3588J SoC 的视频图像处理框架。涵盖视频图像输入(MIPI RX CSI2、HDMI RX 等)、输出(HDMI/eDP、MIPI TX 等)、编解码、Graphics Engine 及视觉算法加速模块,详述各模块特性与参数,还说明评估板输入输出接口支持的分辨率、设备型号等,为评估板视频图像处理应用开发提供参考。

为方便说明RK3588的视频图像处理框架,本文将相关接口和协处理器划分为以下5个部分:

(1)视频图像输入

接口:MIPI RX CSI2、DVP、HDMI RX 2.0、PCIe2.1/3.0;

协处理器:ISP(Image Signal Processor)。

(2)视频图像输出

接口:HDMI/eDP TX、DP TX、MIPI TX DSI2、BT656/BT1120;

协处理器:VOP2(Video Output Processor V2)。

(3)视频图像Graphics Engine

2D协处理器:RGA3(Raster Graphic Acceleration V3);

3D协处理器:GPU Mali-G610 MC4。

(4)视频图像编解码

协处理器:VPU(Video Process Unit)。

(5)视频图像视觉算法加速

协处理器:NPU(Neural Process Unit)、GPGPU(General Purpose computing on GPU,同上述GPU Mali-G610 MC4)。

视频图像输入

MIPI RX CSI2接口

(1)支持的格式:RAW8/10/12/14,YUV422

(2)支持4个MIPI CSI DPHY

MIPI DPHY V1.2标准,支持2Lane,最高2.5Gbps/Lane;

支持将2个MIPI CSI DPHY 2Lane合并为1x 4Lane使用。

(3)支持2个MIPI DPHY/CPHY复用的DCPHY

MIPI CPHY V1.1标准,支持合并为1x 4Lane使用,最高2.5Gbps/Lane。

(4)支持的组合

Camera x6:2 MIPI DCPHY(4Lane) + 4 MIPI CSI DPHY(2Lane);

Camera x5:2 MIPI DCPHY(4Lane) + 1 MIPI CSI DPHY(4Lane) + 2 MIPI CSI DPHY(2Lane);

Camera x4:2 MIPI DCPHY(4Lane) + 2 MIPI CSI DPHY(4Lane)。

常见视频输入数据量理论带宽及Lane数量要求:

备注:以下相关评估计算不含数据传输协议相关开销(大约几个百分点)。

Raw8下1080P@60fps数据量为1920 x 1080 x 1 x 8 x 60 / 10^9 ≈ 0.995 Gbps //1Lane

YUV422下1080P@60fps数据量为1920 x 1080 x 2 x 8 x 60 / 10^9 ≈ 1.990 Gbps //1Lane

Raw8下UHD 4K@60fps数据量为3840 x 2160 x 1 x 8 x 60 / 10^9 ≈ 3.980 Gbps //2Lane

YUV422下UHD 4K@60fps数据量为3840 x 2160 x 2 x 8 x 60 / 10^9 ≈ 7.960 Gbps//4Lane

以OV13850为例进行评估说明:

根据OV13850数据手册说明,使用4个Lane时最大输出为4224x3136@30fps Raw10。此时,总数据量约为4224 x 3136 x 1 x 10 x 30 / 10^9 ≈ 3.974Gbps,平摊到4个Lane约0.993Gbps/Lane,小于2.5Gbps/Lane。

备注:使用Raw格式输入时,还应考虑ISP的处理能力,请参考ISP小节。

DVP接口

(1)支持1个DVP接口;

(2)支持BT.601/BT.656/BT.1120;

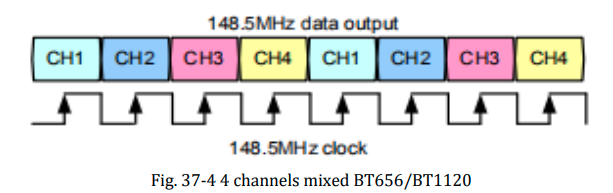

(3)支持2/4通道的BT.656/BT.1120混合的逐行或隔行输入,可实现4路AHD输入;

(4)最高像素时钟150MHz(8bit位深,最高支持1路1080P@60fps和4路720P@30fps)。

更多内容请参考产品资料“6-开发参考资料\数据手册\核心板元器件\CPU\”目录下的《Rockchip RK3588 TRM V1.0-Part1-20220309》。

ISP

Dual Pipe ISP,从DVP/CSI接收Camera图像并进行图像处理。

(1)输入接口

最多同时支持7路接入:MIPI CSI x6 + DVP x1。

(2)图像数据处理能力

48M:8064x6048@15fps dual ISP;

32M:6528x4898@30fps dual ISP;

16M:4672x3504@30fps single ISP。

HDMI RX接口

(1)HDMI 2.0

最高支持UHD 4K@60fps。

(2)HDMI 1.4b

最高支持1080P@120fps;

支持UHD 4K@24/25/30fps;

最高支持DCI 4K@24fps。

PCIe接口

(1)PCIe 2.1(与USB3.1和SATA3.0复用)

支持RC模式,1Lane;

最大理论带宽:5Gbps(支持1080P@60fps RGB24视频输入,数据量约为2.985Gbps)。

(2)PCIe 3.0

支持RC/EP模式,4Lane;

支持1x 4Lane,2x 2Lane,4x 1Lane,1x 2Lane + 2x 1Lane;

最大理论带宽:8Gbps x 4 = 32Gbps(支持8K@30fps YUV420视频输入,数据量约29.830Gbps)。

备注:PCIe接口常用于接收来自FPGA的图像输入。

视频图像输出

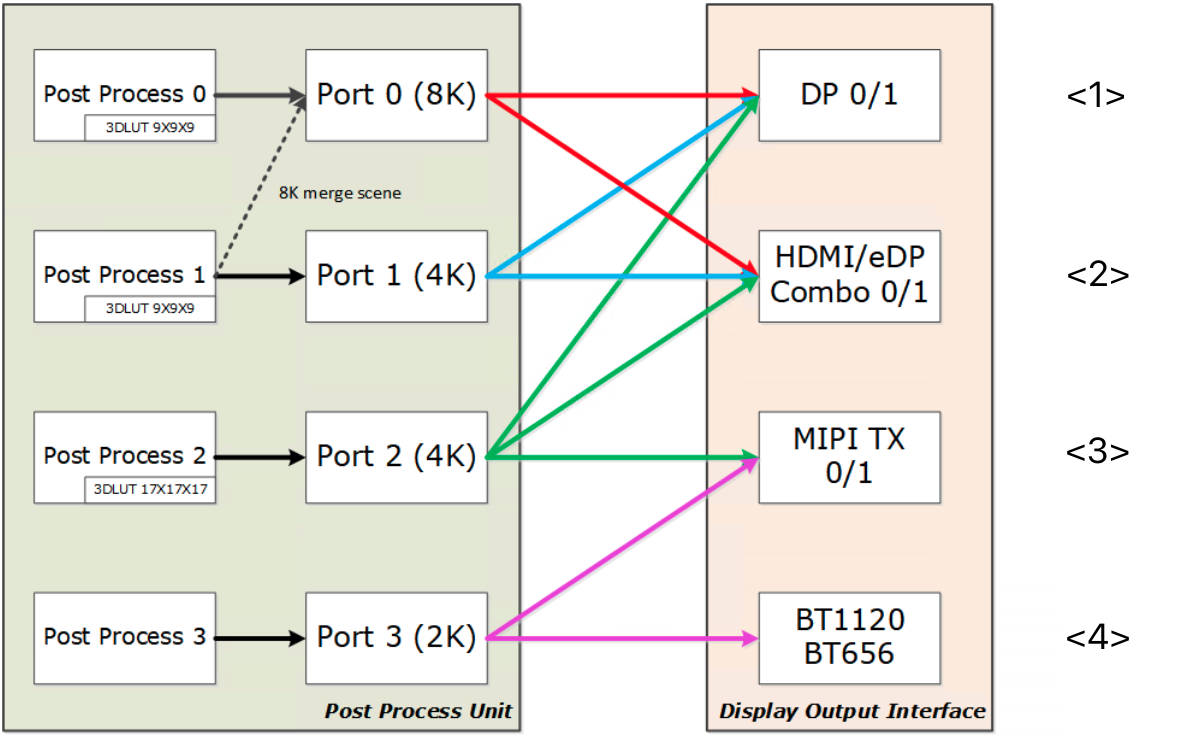

VOP2会从内存中读取视频数据和UI数据进行处理(缩放、裁剪、图层叠加等),然后将数据发送到不同显示接口进行图像的显示。

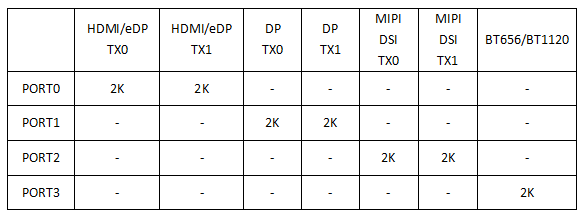

VOP2及显示输出接口:

更多内容请参考产品资料“6-开发参考资料\数据手册\核心板元器件\CPU\”目录下的《Rockchip RK3588 TRM V1.0-Part2 20220309》。

VOP2的处理及接口能力决定了最终的图像输出能力。

(1)DP 0/1

7680x4320@30fps:Port0 + Port1;

4096x2304@60fps:Port0/Port1/Port2;

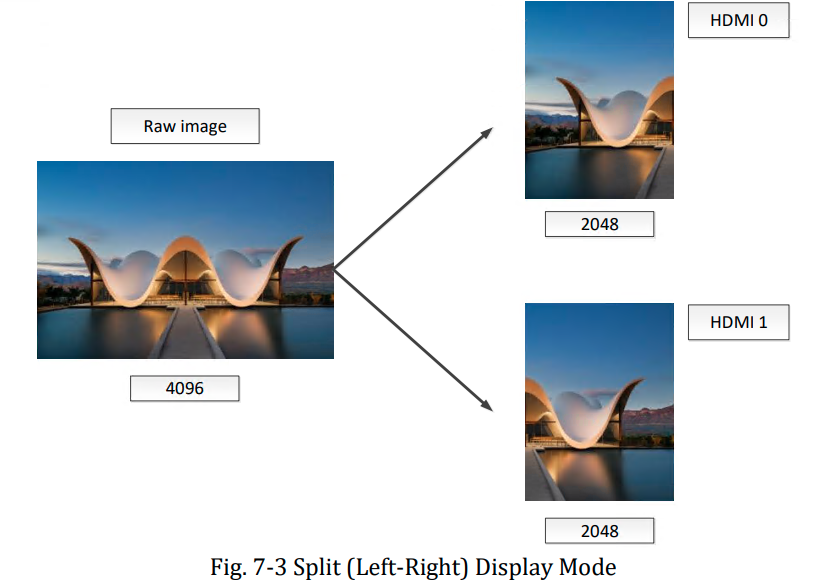

Split mode:1帧4K图像的左图(2K)输出到DP TX0,右图(2K)输出到DP TX1,实现双DP显示。(Split mode:参考下文HDMI TX Split mode示例图)。

(2)HDMI/eDP Combo 0/1

7680x4320@60fps:Port0 + Port1 -> HDMI;

4096x2304@60fps:Port0/Port1/Port2 -> HDMI/eDP;

Split mode:1帧4K图像的左图(2K)输出到HDMI/eDP TX0,右图(2K)输出到HDMI/eDP TX1,实现双HDMI/eDP显示(Split mode:参考下文HDMI TX Split mode示例图)。组合情况如下:

HDMI0 + HDMI1;

HDMI0 + eDP1;

eDP0 + HDMI1;

eDP0 + eDP1;

(3)MIPI TX 0/1

4096x2304@60fps:Port2;

2048x2304@60fps:Port3;

Split mode:1帧4K图像的左图(2K)输出到MIPI TX0,右图(2K)输出到MIPI TX1,实现双MIPI显示。(Split mode:参考下文HDMI TX Split mode示例图);

Copy mode:MIPI TX0和MIPI TX1的图像内容是一致的,来自Port2/Port3。

(4)BT656/BT1120

1920x1080@60fps:Port3(最大分辨率是2K)。

部分可实现的显示输出组合如下:

- 4路:4K + 4K + 4K + 2K;

- 3路:8K + 4K + 2K;

- 7路:2K + 2K +2K +2K + 2K + 2K + 2K(使用Split mode)。

视频图像编解码

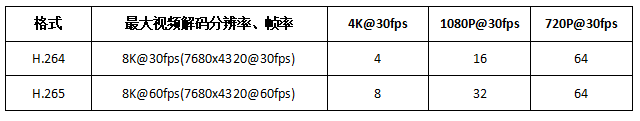

视频解码

根据理论数据量,对于H.264格式,最大支持1路8K@30fps视频解码,可支持多路并行视频解码,支持4路4K@30fps视频解码,或16路1080P@30fps视频解码,或64路720P@30fps视频解码。

同理,对于H.265格式,最大支持1路8K@60fps视频解码,或支持8路4K@30fps视频解码,或32路1080P@30fps视频解码,或64路720P@30fps视频解码。

备注:以上为理论值,仅供参考。

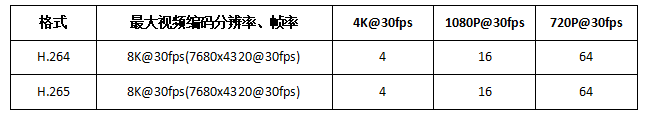

视频编码

根据理论数据量,对于H.264格式,在8K@30fps视频输入时最大支持1路视频编码,可支持多路并行视频编码,在4K@30fps视频输入时支持4路视频编码,在1080P@30fps视频输入时支持16路视频编码,在720P@30fps视频输入时可支持64路视频编码。

同理,对于H.265格式,在8K@30fps视频输入时支持1路视频编码,在4K@30fps视频输入时支持4路视频编码,在1080P@30fps视频输入时支持16路视频编码,在720P@30fps视频输入时支持64路视频编码。

备注:以上为理论值,仅供参考。

JPEG解码

支持96 x 96到8192 x 8192分辨率(64M pixels)。

JPEG编码

(1)支持48 x 48到65536 x 65536分辨率;

(2)支持YUV400/YUV411/YUV420/YUV422/YUV440/YUV444;

(3)支持最高1080P@280fps;

(4)支持MJPEG。

视频图像Graphics Engine

RGA3

RGA3是一个2D图形处理加速引擎,可以实现图像的旋转,缩放,裁剪,混合和RGB/YUV转换等。主要特性如下:

(1)输入:ARGB/RGB888/RGB565/YUV420/YUV422/BPP,最大8192x8192;

(2)输出:ARGB/RGB888/RGB565/YUV420/YUV422,最大4096x4096;

(3)旋转:90/180/270度;

(4)Alpha Blending功能支持:global alpha,per pixel alpha和fading。

ARM Mali-G610 MP4

ARM Mali-G610 MP4支持2D/3D图形处理加速。主要特性如下:

3D API支持:OpenGLES 1.1/2.0/3.2,Vulkan1.2。

视频图像视觉算法加速

NPU(Neural Process Unit)

NPU是一个神经网络推理加速引擎。主要特性如下:

(1)算力6 TOPS(INT8);

(2)包括3个NPU核心,并支持3核心协同工作,双核心协同工作,或单核心独立工作;

(3)支持INT4,INT8,INT16,FLOAT16,BFLOAT16和TF32;

(4)支持多任务和多场景的并行处理;

(5)支持的深度学习框架:TensorFlow,Caffe,Tflite,Pytorch,Onnx NN,Android NN等。

GPGPU(General Purpose computing on GPU)

ARM Mali-G610 MP4也是一个GPGPU,通过OpenCL进行通用计算,可实现计算加速和神经网络推理加速,理论上可以提供接近0.5TFLOPS算力(非官方数据,来源于网上资料)。

计算加速:OpenCL 2.2 Full Profile;

神经网络推理加速:TVM(基于OpenCL),使用参考:https://tvm.apache.org/docs。

由于篇幅过长等原因,部分内容均不逐一展示,如需获取完整版详细资料,请关注创龙科技微信公众号或官网,或者评论区留言,感谢您的支持!

浙公网安备 33010602011771号

浙公网安备 33010602011771号