CH395Q INT脚变化说明

测试环境:CH32v307+CH395Q;SPI接口,直连电脑

芯片固件版本:0x4A

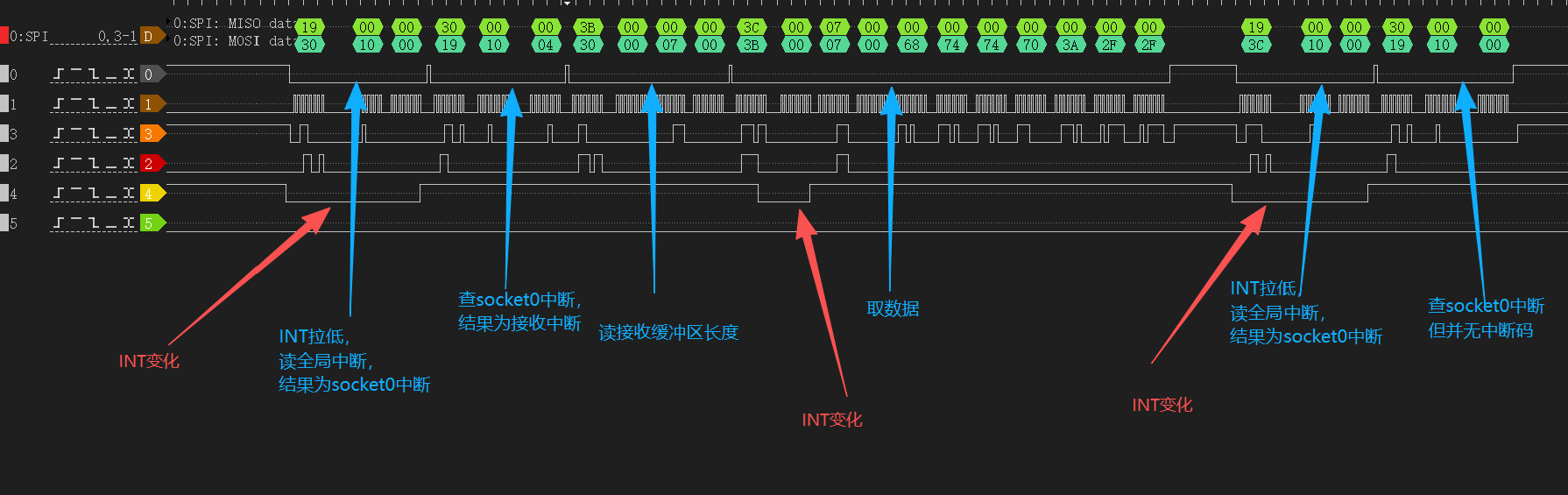

1.接收一包数据的流程,逻辑分析仪时序如下(其中,通道0为片选,通道1为时钟,通道2/3为数据,通道4为INT脚)

常规接收流程不做过多解释,主要看一下INT脚变化:

第一次INT变化:芯片收到包,拉低INT脚,代码中逻辑执行glob中断(0x19命令),执行完拉高INT脚;

第二次INT变化:前面执行完glob中断后,芯片发现接收缓存中存有数据长度,再次拉低INT脚,当执行取数据的动作(0x3C命令)后,拉高INT脚

第三次INT变化:前面第二次拉低时,芯片内部已经将glob中断标志以及socket0的中断(接收中断)置位,而执行完取数据的动作(0x3C命令)后,将socket0接收中断标志清除了,没有同步把对应的glob中断清除,所以有了第三次INT脚的变化(实际没有影响,并不会产生多余的中断状态码)

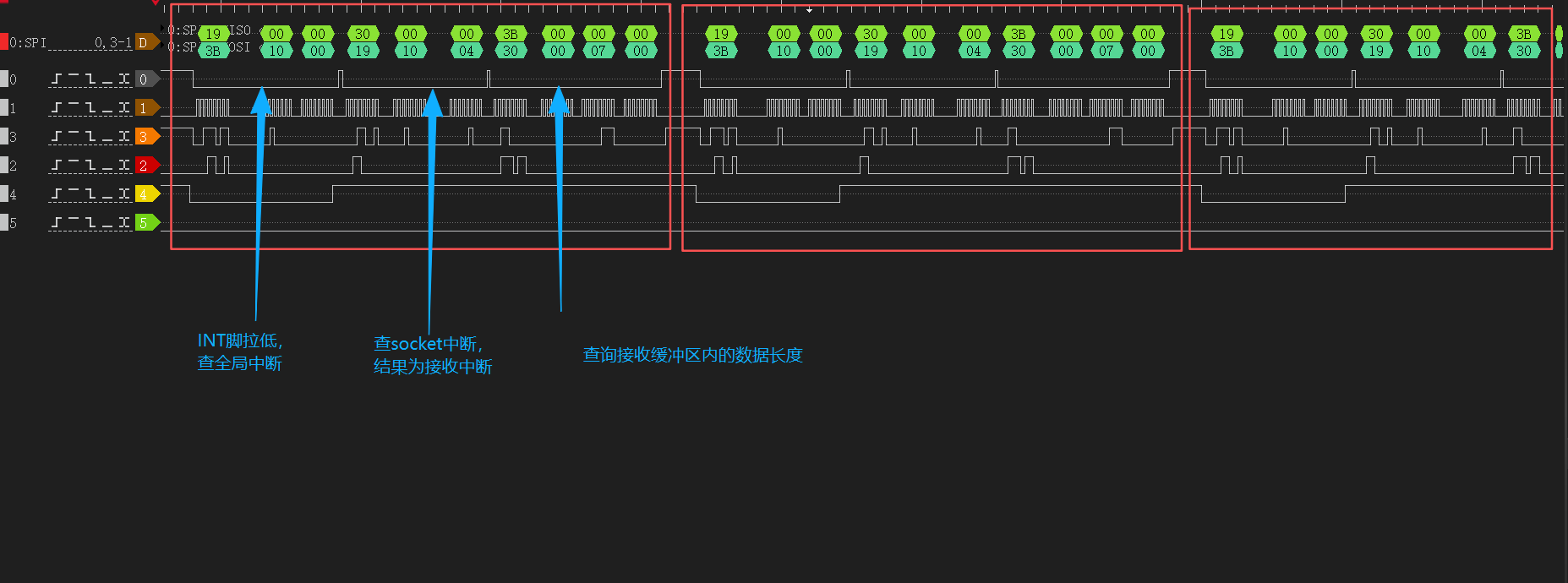

2.接收数据,但并不将数据从接收缓冲区取出,那么芯片会一直持续产生中断(socket的接收中断),INT脚变化如下

3.发生数据(机制:每次调用send命令发送数据前,要判断send_free中断,只有产生了这个中断,才可以调用send命令发送下一包数据)

浙公网安备 33010602011771号

浙公网安备 33010602011771号