HDLBits(10)2.14

3 电路

3.1 组合逻辑

3.1.1 基础门

- Wire: assign out = in ;

- GND: assign out = 1'b0 ;

- NOR: assign out = ~ (in1 | in2) ;

- Another Gate: assign out = in1 & (~in2) ;

- Two Gate: assign out = (in1 ~^ in2) ^ in3 ;

* 异或门:out = a ~^ b = a^~ b = ~ (a ^b)

- More Gates:

assign out_and = a & b;

assign out_or = a | b;

assign out_xor = a ^ b;

assign out_nand = ~(a & b);

assign out_nor = ~(a | b);

assign out_xnor = ~(a ^ b);

assign out_anotb = a & (~b);- 7420:

assign p1y = ~(p1a & p1b & p1c & p1d);

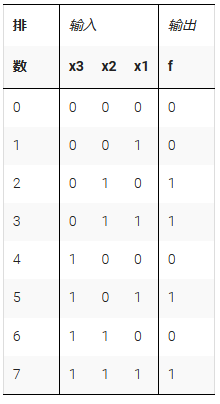

assign p2y = ~(p2a & p2b & p2c & p2d);- Truthtable:

assign f = ((~x3) & x2 & (~x1)) | ((~x3) & x2 & x1) | (x3 & (~x2) & x1) | (x3 & x2 & x1);

- Two bit equality

创建一个具有两个 2 位输入A[1:0]和B[1:0]的电路,并产生一个输出z。如果A = B ,则z的值应为 1 ,否则z应为 0

assign z = (A == B) ? 1'b1 : 1'b0 ;

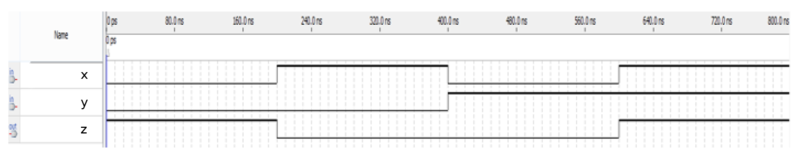

- Simple circuit A

创建模块A实现函数 z = (x^y) & x

module top_module (input x, input y, output z);

assign z = (x^y) &x;

endmodule- Simple circuit B

module top_module ( input x, input y, output z );

assign z = ~(x^y);

endmodule- Combine circuit A and B

module top_module (input x, input y, output z);

assign z = (((x^y)&x)|(x~^y))^(((x^y)&x)&(x~^y));

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号