数字电路--H74139

H74139是双2-4译码器,最近才搞懂其大致的原理,稍微记录记录。

工作原理的VHDL代码:

-- H74139 双2-4译码器,VHDL主要代码

libray IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity H74139 is

PORT(A1, B1, G1: in STD_LOGIC;

A2, B2, G2: in STD_LOGIC;

Y: out STD_LOGIC_VECTOR(10 to 13); --

Y: out STD_LOGIC_VECTOR(20 to 23));

end H74139;

ARCHITECTURE dataflow of H74139 is

begin

Y10 <= '0' when(A1='0')and(B1='0')and(G1='0')

else '1';

Y11 <= '0' when(A1='1')and(B1='0')and(G1='0')

else '1';

Y12 <= '0' when(A1='0')and(B1='1')and(G1='0')

else '1';

Y13 <= '0' when(A1='1')and(B1='1')and(G1='0')

else '1';

--...Y(23 downto 20) --类似以上的规律,就不浪费空间了

end dataflow;

单个2-4译码器的真值表

---- 2-4译码器真值表 ----

G B A | Y0 Y1 Y2 Y3

0 0 0 | 0 1 1 1

0 0 1 | 1 0 1 1

0 1 0 | 1 1 0 1

0 1 1 | 1 1 1 0

1 0/1 0/1 | 1 1 1 1

--------------------------------

通过真值表可以发现规律:将GBA看作由高位到低位表示的二进制数i,则输出端的Yi为0其他为高电平。

当i>3时,即使能端(G)为1时输出全部为高电平。

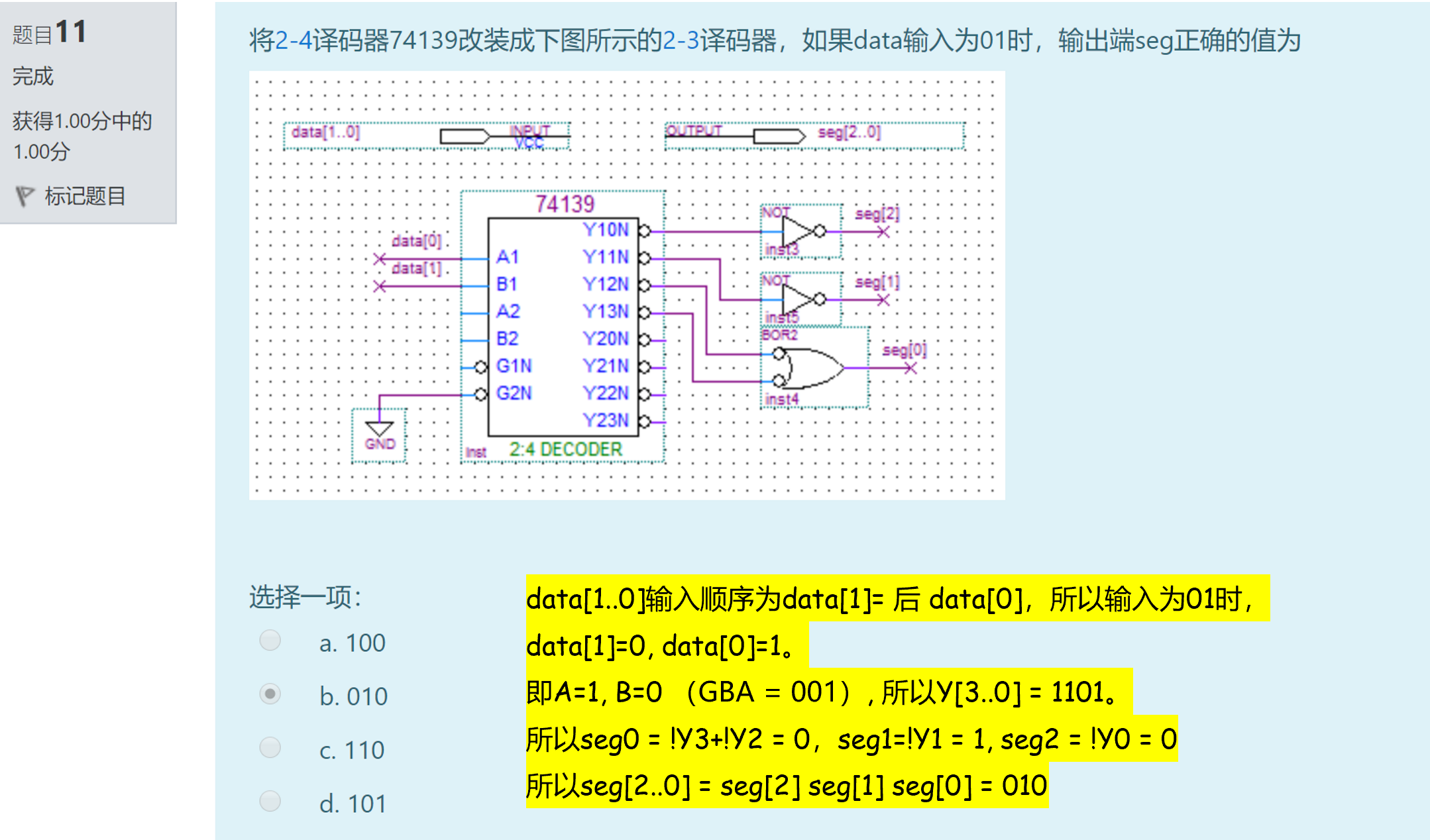

来一道题目分析分析。提起注意,在设置STD_LOGIC_VECTOR时,若B downto A,则信号接收顺序为B-->A;若是A to B,则信号的接收顺序为A-->B。

浙公网安备 33010602011771号

浙公网安备 33010602011771号