CDC 设计原则与同步器解析

在现代芯片设计中,时钟域交叉(Clock Domain Crossing,CDC)问题几乎无法避免。随着设计复杂度不断增加,系统中往往存在多个时钟域,而跨时钟域信号传输不可避免地带来了亚稳态(Metastability)风险。本文将探讨 CDC 的设计原则、同步器的作用以及提高设计鲁棒性的方法。

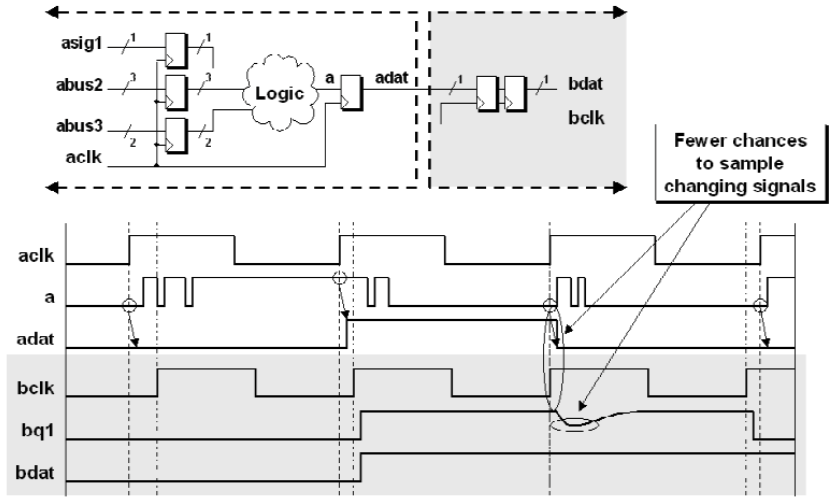

为何 CDC 中亚稳态不可避免

当信号从一个时钟域传输到另一个时钟域时,由于时序不匹配,很可能在触发器采样瞬间进入亚稳态。亚稳态并非完全消除的,而只能通过合理的设计控制并降低其影响。如果设计不当,亚稳态效应会沿着电路传播,造成不可预测的逻辑行为,严重时会导致整个芯片功能失效。

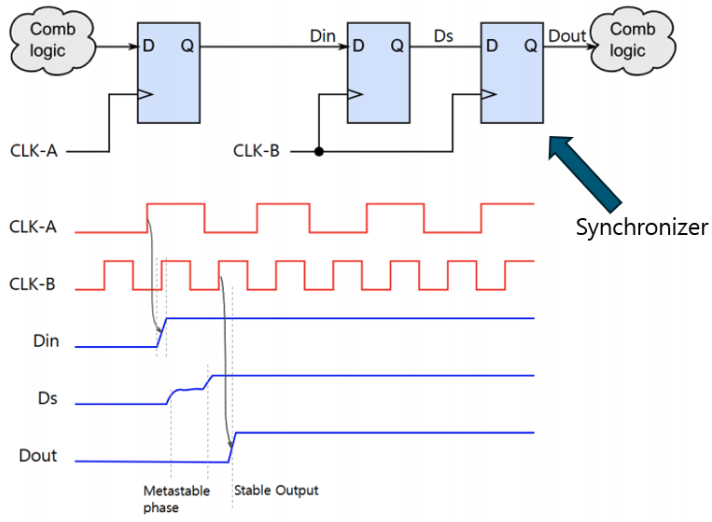

同步器的作用

同步器(Synchronizer)是应对亚稳态的常用结构。最经典的形式是双触发器同步器(Double-Flop Synchronizer)。其核心思路是:

第一个触发器可能进入亚稳态;

第二个触发器提供足够时间让信号恢复稳定;

单一扇出(Single Fan-Out)避免了亚稳态信号扩散到多个单元,从而保护相关性。

在一些高速设计中,还会采用三触发器或更多级同步器,以进一步提升稳定性。

亚稳态概率与可靠性

亚稳态持续的时间符合一个指数衰减规律,其概率公式为:

P(t) ≈ e^(−t/τ)

其中 τ(tau)为解析时间常数,与触发器特性及环境噪声相关。

随着解析时间 t 的增加,未解决亚稳态的概率迅速下降。

通过合适的同步器结构,可以实现极高的平均失效间隔时间(MTBF,Mean Time Between Failures),从而保证芯片在大规模运行条件下的稳定性。

设计原则总结

为了实现鲁棒的 CDC 接口,设计者应遵循以下原则:

1、必须使用同步器

所有跨时钟域的控制信号都应通过双级或多级触发器同步。

2、避免扇出扩散

同步器输出信号应尽量单一扇出,避免未稳定信号同时驱动多个逻辑单元。

3、根据时钟频率决定级数

对于高速时钟,考虑采用三触发器甚至更多级同步器。

4、关注复位信号

CDC 中的异步复位也可能引入亚稳态,需要相应的同步机制。

5、进行 CDC 检查与验证

借助 EDA 工具进行 CDC 静态检查,确保设计中所有跨时钟域路径都被正确处理。

学习与实践路径

对于从事 IC 设计的工程师或学生,CDC 是一项必须掌握的技能。要深入理解并熟练应用这些原则,系统化学习非常重要。这里推荐 EDA Academy (www.eda-academy.com) :

你可以找到覆盖 CDC、时序分析、同步器设计的专业课程,既有理论解析,也有工程实战案例。

平台上有大量最新网课,帮助你在 RTL 设计、验证和 CDC 检查工具使用上快速提升。

如果你在 CDC 或相关领域有丰富经验,还可以注册成为导师开设课程,分享你的知识与实践。

只需使用邮箱注册,即可免费订阅 newsletter,定期收到最新课程与行业动态。

更值得一提的是,平台有销售联盟计划,推广课程即可获得 20%-50% 的佣金。学习、教学与分享三者结合,形成完整闭环。

CDC 设计原则的核心在于:接受亚稳态不可避免,但通过同步器和合理的设计原则,可以把风险控制在极低水平。双触发器同步器是最常见的结构,而多级同步器则适用于高速或高可靠性场景。掌握这些知识,不仅能提升个人设计能力,还能在团队开发和芯片量产中避免重大风险。

浙公网安备 33010602011771号

浙公网安备 33010602011771号