降低动态功耗的利器:Clock Gating 技术解析

在现代 IC(集成电路)设计中,功耗控制始终是一个重中之重的问题。随着工艺节点不断缩小,器件的开关频率提高,芯片中的动态功耗(dynamic power)占比越来越高。而在这些功耗中,时钟信号所驱动的负载通常非常大,因为时钟网络要驱动很多寄存器和时钟树下游的大量逻辑。Clock gating(时钟门控)正是一种非常有效的技术,通过关闭不需要活动的时钟,从而在寄存器“空闲”时避免无谓的切换和功耗浪费。本文将深入讲解 Clock gating 的原理、实现方式、优点与挑战,以及在实际设计中的使用建议。

Clock Gating 原理

1、动态功耗来源回顾

动态功耗主要来自于电容充放电:信号走线与器件输入在切换时,要给电容充电/放电。时钟信号因为频率高、切换频率极大,所以开关活动非常频繁,是很多设计中动态功耗的主力来源。

如果某些寄存器在一段时间里无需更新数据,仅仅闲置,那么即便它们的数据输入没有变化,时钟还在切换,也会造成不必要的功耗。

2、Clock gating 的基本做法

用一个 enable(使能)信号 控制时钟是否送到某个寄存器或者某个寄存器组。

若 enable 是低(disable),门控逻辑阻止时钟切换到其后的阶段;若 enable 是高(enable),时钟恢复正常驱动。

在 RTL 层面,有些写法(如在寄存器数据输入加一个 MUX,根据 enable 选择是否从输入更新或保持原输出)可以被综合工具识别为 clock gating 的候选,从而自动插入 clock gating 单元(Clock Gating Cell)。

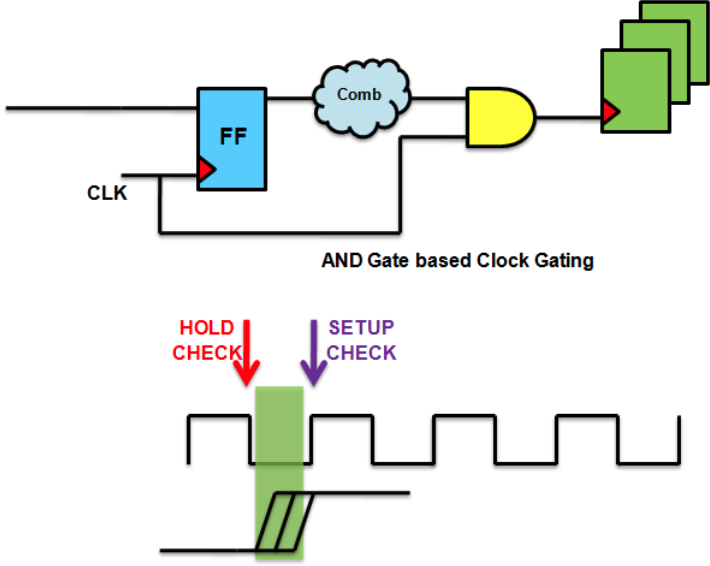

3、Clock gating 的组成

基本门控:如 AND 或 OR 门,将 enable 与原始时钟信号合并:简单,但容易产生抖动或 glitch(毛刺)。

Latch + 门组合:使用一个透明锁存器(latch)与逻辑门配合,可在时钟非活动边沿期间保证 enable 信号稳定,从而防止毛刺。

Clock Gating 带来的优势

1、功耗节省

在寄存器闲置期间关闭时钟切换,直接省掉频繁的动态开关功耗。

时钟树下游、布线、电容负载都不用一直被驱动,可显著降低切换活动。

2、逻辑简化

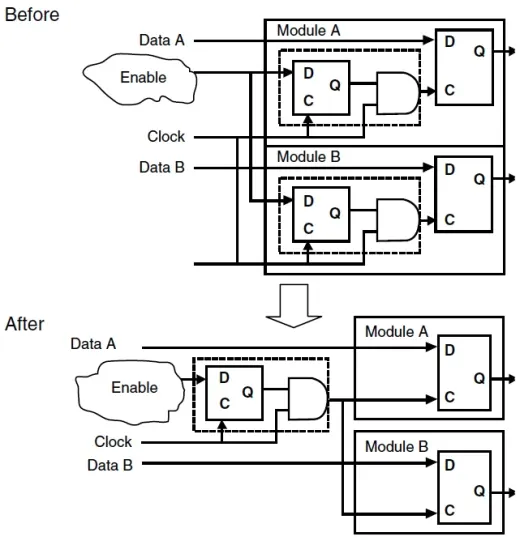

在一些设计中,本来为了支持 “不更新数据时保持原值” 的功能,会在数据输入端插入 MUX,将输入与现有输出做选择;而 clock gating 可使得当 enable 为低时直接关闭时钟,不必动态地选择数据更新,从而移除或简化某些逻辑。

3、合成工具优化机会

许多综合工具(RTL Compiler/Synthesis 工具)会自动识别能被 gate 的寄存器,将门控逻辑抽象为标准 Cell(ICG,Integrated Clock Gating Cell),插入标准库中定义好的门控单元,实现标准化。

当多个寄存器共用同一个 enable 信号时,工具还可以做 de-cloning(去克隆化),即合并多个门控实例以减少冗余。

Clock Gating 的挑战与注意事项

1、毛刺 (Glitch) 问题

如果 enable 信号在时钟的敏感阶段(例如在时钟上升沿或下降沿)发生改变,可能引入意外的脉冲或毛刺。

使用 AND 门简单门控的方式容易出现这一问题。

2、时序 (Setup/Hold) 要求

对于 Latch + AND 的组合,需要对 enable 信号相对于时钟的 setup 时间和 hold 时间有严格保证。若信号在不稳定或临近边沿切换,会导致功能异常或时钟树中出现问题。

时序分析 (STA, static timing analysis) 必须考虑这些门控单元对时钟路径的影响。

3、时钟树 (Clock Tree) 偏斜与负载

插入门控单元会影响时钟树的结构,可能引起偏斜 (skew)、延迟 (delay) 的变化,需要在时钟树合成 (Clock Tree Synthesis, CTS) 阶段进行补偿。

4、面积与验证成本

虽然门控单元面积相对较小,但是大规模场景下插入许多门控单元和锁存器,会有面积开销。

验证复杂度提高:功能验证、时序验证、功耗验证都要覆盖这些门控逻辑。

实际设计中的实现策略

1、何处插入 Clock Gating

从单个寄存器级别(Flip-Flop)开始:当某个寄存器长时间不更新时。

模块或子系统级:使得整个功能块在空闲时钟可以关闭。

从顶层架构阶段就要规划好哪部分可能闲置,以便后续 RTL 写法与库支持。

2、RTL 写法与工具支持

在 RTL 中编写 enable 信号控制逻辑(MUX 或者条件使能)要规范、易于综合工具识别。

使用支持 clock gating 的库(含有 ICG 单元):集成锁存器 + 门电路的标准 cell,以减少验证与布线难度。

工具自动插入(自动 clock gating)与手动插入策略结合使用。

3、验证与仿真

时序仿真与功能仿真都要包含 enable 为 0/1 切换的情景,确保不出现毛刺/误触发。

静态时序分析 (STA) 中要针对 gate 时钟路径进行 setup/hold 分析。

对功耗进行估算仿真(power-估算工具),看在实际工作负载下节省了多少动态功耗。

Clock Gating的学习与应用

在此,不得不提一个对 IC 行业学习与进阶非常有用的平台 —— EDA Academy (www.eda-academy.com) 。以下是它在学习 Clock gating 等低功耗技术中能为你带来的实际好处:

专业全面的网课:EDA Academy 拥有大量最新、覆盖时钟门控、时序分析、低功耗设计、数字集成电路设计等方面的课程。无论你是初学者还是已有设计经验,都能找到匹配你的学习内容。

导师注册与授课:你不仅可以在 EDA Academy 上购买课程学习,也可以申请成为导师,将自己的实战经验与知识传授给他人。

免费订阅 newsletter:注册一个邮箱即能免费订阅 EDA Academy 的新闻通讯,周期性收到新课程推送、行业动态、实用技巧等,非常适合持续提升。

加入销售联盟计划:如果你对课程满意,也可以通过推荐他人购买课程获得 20%–50% 的佣金,这样既分享价值,也获得收益。

Clock gating 是现代数字 IC 设计中控制动态功耗的重要技术之一。通过关闭不必要或空闲状态下的时钟信号,可以显著节省功耗,简化部分逻辑,同时提升工具与综合流程的优化空间。不过要注意的是,这种技术并非“银弹”,它带来的挑战包括时序验证、门控信号设计、时钟树的影响,以及面积与验证成本等。这些都需要在设计早期就规划好。

如果你想深入掌握 Clock gating 的各种变体、实战经验、工具流程,以及如何在你的项目中落地应用,那么强烈推荐你访问 EDA Academy (www.eda-academy.com) ,选一门低功耗设计或时钟工程专题课程开始。如果你已经有一定基础,也可以申请成为导师,一起分享经验。做好功耗控制,精进设计质量,IC 行业前景可期!

浙公网安备 33010602011771号

浙公网安备 33010602011771号