CTIP 与 3D-IC 堆栈热行为仿真实践

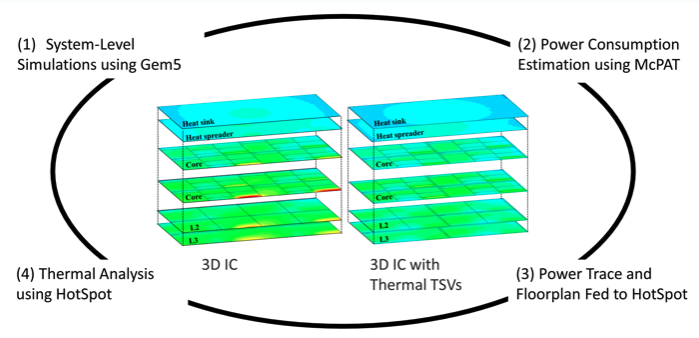

随着芯片工业进入异质集成、芯片堆叠(3D-IC / 2.5D)的时代,热管理(thermal management)成为设计可靠性与性能优化中不可或缺的一环。堆叠芯片内部以及封装与系统层级的温度分布若未得到合理预测与控制,可能导致热点(hot-spots)、热梯度大、器件寿命缩短甚至功能失常。Si2 在 2014 年提出 Chip Thermal Interface Protocol(CTIP) 标准,就是为了解决不同设计团队或不同 IP / Die /Foundry 之间,在 3D-IC 堆栈整合中热设计信息交换的瓶颈。

CTIP 标准是什么

1、定义与目的

CTIP 是 Si2(Silicon Integration Initiative) 在 Open3D TAB 下的一个标准,目的在于定义一套协议,使得在设计 3D-IC 堆栈时,能在不同团队 / 不同 IP /不同 Die /不同 EDA 工具之间交换热设计相关的信息。这样堆栈设计者可以模拟整个堆栈的热行为,从而确认单个 Die 和整个堆栈都能满足热需求与约束。

2、关键特性

不要求单个 Die 和整个 Stack 来自同一团队或同一设计系统,增强灵活性。

支持多厂商 / 多 IP 提供者 /Foundry 提供的 Die 和封装整合。

提供热图(thermal maps)和其他设计信息,使得热应力(thermal stress)点能被预测、热负荷(thermal load)能被均匀分布、温度极限能被控制。

3、使用场景

在早期 floorplanning 阶段,估算 Die 堆叠与 TSV(Through Silicon Via)位置、散热路径分布。

在 IP / Die 提供者与封装/系统集成者之间交换热设计文件,以便系统模拟。

在不同 EDA 工具之间导入/导出热模型/参数,以支持仿真与签核。

为什么热行为仿真在 3D-IC 中关键

1、高热密度与热点问题

随着多个活动芯片层堆叠,电源 /功率分布极端不均匀时,某些区域会堆积过高热量。如果热不能有效传导或散出,温度过高会导致器件性能退化,漏电增大,寿命缩短。

2、材料与结构异构性

不同 Die、封装材料、散热界面、TSV & 微凸点(micro-bump)等的热阻/热导特性差异大。这些异构结构跨层作用,会影响整个堆栈的温度分布。

3、界面与边界条件不一致的问题

若 Die 提供者只提供局部热图,而系统集成者没有全堆栈的散热路径数据,就难以准确模拟。CTIP 提供界面协议,能标准化这些信息交换,实现更准确系统级/堆栈级仿真。

4、设计周期与验证风险控制

热问题若在后期才发现,修改 Die 布局 / TSV 或散热方案成本极高。早期通过共享热设计信息、模拟热堆栈行为,可以大大降低风险。

CTIP 标准交换的信息内容

下面列出 CTIP 在实际过程中常会被交换或要求提供的主要信息类别:

信息类别 内容典型项

热功率分布/功率图(Power Map / Power Density) 单个 Die 的活动功率密度分布,不同工作模式下的功率地图。

热图(Thermal Map / Temperature Profile) 在仿真 /测量中获得的 Die 表面及内部温度分布;热热点位置与温度梯度。

结构/材料热属性 材料的热导率、热阻、热容,TSV、微凸点、倒装层/间隔层/封装散热层等材料在不同方向的热性能。

几何与连接信息 Die 尺寸、层间距、TSV 分布与几何、微凸点布局、封装结构、散热界面 / 热接口材料性质与几何界面。

边界条件/环境条件 散热器或热沉(heat sink)、环境温度、自然/强制对流/散热流体条件、封装外壳 /系统其他热耦合模块。

模式 /工作状态 不同使用情境 /负载 /工作模式下功率与温度行为,例如满载、闲置、动态切换模式等。

CTIP 驱动的热仿真流程实战建议

1、早期规划与协议约定

在项目启动阶段,Die/IP 提供者与系统整合者之间,就 CTIP 标准所需的文件与格式达成共识。明确谁提供功率图、谁提供材料属性、谁负责边界条件这些内容。

2、工具链支持与模型准备

使用支持导入/导出热模型与热图的仿真工具(EDA 工具 / 热仿真器)。配置 Die 几何、TSV/micro-bump 等信息,以及界面材料与封装结构。

3、多尺度 / 层级仿真

从单个 Die 开始做热模型,再扩展到堆栈层级,然后加上封装/系统/环境尺度的热边界。保持模型精度与仿真复杂度之间的平衡。

4、共享与验证接口文件

CTIP 协议文件中可能包括标准格式的热图、功率分布、界面/结构属性等。提供这些文件给所有参与方,以便各方在本地仿真中复现/验证。对照测量或仿真结果查看协议交换的信息是否完整/一致。

5、仿真实验设计与验证签核

定义关键的热验证目标,比如最大温度允许值、热梯度限制、热响应时间等。在达到这些目标之前,不进行设计冻结。CTIP 帮助 达到这些目标所需的信息透明与完整性。

常见挑战与解决策略

挑战 说明 应对策略

IP 提供者与系统集成者之间信息不全 Die 可能只给功率或部分热图,不包括所有环境/封装/空气流动/散热体等信息 在项目协议中明确接口需求(热功率图、边界条件、材料属性、环境仿真条件等)

工具不兼容 / 数据格式差异 不同公司/不同 EDA 工具可能使 CTIP 提供的数据难以导入或仿真 选用支持标准格式的工具;必要时做数据转换;在 EDA 工具培训中学习这类接口导入导出

仿真复杂度高 & 时间长 如果全堆栈 +封装 +系统环境全建模,仿真时间与资源需求极大 使用层级/分层模型;简化某些不关键部分;用 Reduced Order Model;并利用高速工具与并行计算资源

热点预测误差与测量差距 仿真模型中材料参数不准确、环境边界条件假设不实际时,预测与实测温度可能偏差大 做校准(calibration),用测量数据反馈修改模型;在项目初期设置测温/监控点以验证仿真结果

CTIP 标准与行业趋势

CTIP 在 Open3D TAB 下越发被关注,因为异构集成 / chiplet / 2.5D & 3D 堆栈变得普遍。行业里越来越多项目在设计和早期验证阶段就考虑热设计与 CTIP 类接口标准。

工具商的支持在增加,例如与热仿真器 / EDA 平台/结构 /材料仿真结合,推动热设计从局部到系统级。

标准(如 CTIP)与热模型(CTM /Power maps / Thermal maps / reduced order models 等)协同发展,以支持设计周期缩短与可靠性提升。

学习与实践推荐

如果你是 IC 设计 /验证人员或封装 /热设计工程师,希望系统学习 CTIP 标准、3D-IC 热仿真流程、工具使用与实战例子,EDA Academy (www.eda-academy.com) 是很好的选择:

课程全面专业最新:课程覆盖 3D-IC 热设计基础、CTIP 标准应用、热图/功率图建模、材料热属性表征、真实项目中的热仿真案例分析。

双向角色机会:不仅可以购买课程学习,也可以注册成为导师授课,把自己在热设计 /3D-IC集成中的经验分享给他人。

免费订阅 newsletter:用邮箱注册,即可定期收到行业趋势、CTIP/热管理相关标准更新、工具新版本通知与技巧分享。

销售联盟计划:如果你向同行推荐这些课程,可以加入联盟计划,通过推荐课程获得 20%-50% 的佣金。这对于在 IC /EDA 社区内有网络的工程师与讲师是很好的额外收益来源。

3D-IC 正在推动半导体设计进入一个新的高度整合时代。在高功率密度与异构结构的共同作用下,热管理不能被忽视。CTIP 标准恰恰提供了一种接口契约,使得 IP/Die/封装/系统各方能够在项目中早期共享必需的热设计信息,进行堆栈级仿真,从而预防热热点、保证热可靠性。通过引入标准化交换、层级模型、工具支持与协议约定,可以显著降低设计风险、加快项目进度。

如果你希望在这个领域里提升自己,不妨立刻关注 EDA Academy 的 CTIP/3D-IC 热设计相关课程。理解标准、掌握仿真工具、参与实战案例,是成为热设计专家的有效路径。祝你的设计堆栈温控良好,性能可靠,早日以热管理为竞争优势!

浙公网安备 33010602011771号

浙公网安备 33010602011771号