ECC的秘密

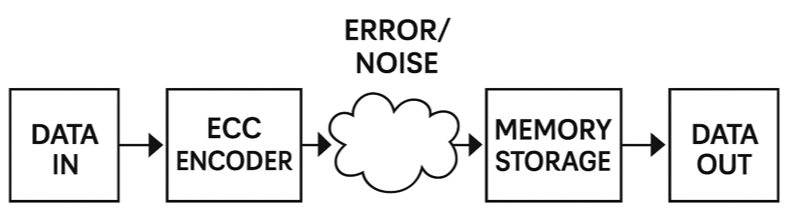

在数字世界里,数据的传输与存储无处不在。但伴随而来的,是噪声、缺陷、传输错误等潜在威胁。错误纠正码(Error Correction Code,ECC)作为保障数据可靠性的核心技术,成为芯片设计、内存架构和系统安全中不可或缺的一环。本文将从ECC的原理、常见方法到在DRAM中的应用逐层展开,并结合学习资源,帮助工程师与学习者全面理解这一关键技术。

ECC的基本原理

ECC的核心思想,是通过冗余信息来检测和纠正数据错误。

噪声与干扰:当数据被读取或传输时,随机噪声会改变比特值。

冗余信息:ECC利用额外的校验比特,使接收端能够判断甚至修复错误。

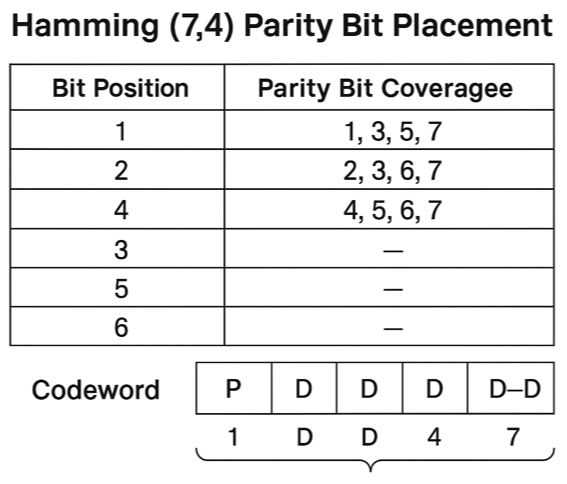

纠错能力:以常见的汉明码(Hamming Code)为例,能够实现“单错纠正、双错检测”(SECDED)。

越强大的ECC方案,需要更多计算资源与存储开销。如果在硬件层面完成,就意味着更大的硅面积;在软件层面完成,则意味着更多CPU周期。

ECC的进化

ECC技术并非一成不变,而是不断演进:

第一代:以汉明码为代表,解决单比特错误。

第二代:发展到可修复整颗器件级别错误。

第三代:在芯片内部直接集成ECC,提供更底层的保护。

这些演进不仅提升了数据安全,也让工程师在设计和测试环节中有了更大的灵活性。例如,可以将部分纠错能力用于修复已知坏单元,而将另一部分用于运行时抗噪声,形成灵活的资源分配。

ECC在DRAM中的四种应用方式

DRAM作为计算机系统的核心存储,ECC在其中的实现方式尤为多样。

1、旁带式(Side-band ECC)

额外增加存储芯片专门用于保存校验码。

控制器负责在写入和读取时计算与校验。

优点:简单高效,应用广泛。

2、内嵌式(In-line ECC)

数据与校验码共存在同一存储芯片内。

常用于LPDDR等16位总线架构,避免总线过宽。

缺点:需要额外的读写操作,带来延迟。

3、芯片内ECC(On-chip ECC)

从DDR5开始普及,错误在传输到控制器前即可修复。

但无法检测传输链路上的错误,需配合其他机制。

4、链路ECC(Link ECC)

专注于传输链路数据的保护,发送和接收两端均计算校验。

与芯片内ECC结合,才能实现端到端完整保护。

此外,还有循环冗余校验(CRC)作为另一种保障数据传输可靠性的选择。

ECC与设计权衡

ECC的强弱设计,本质上是性能、成本与安全性的博弈:

更强的纠错能力 = 更高的硅片面积或更多CPU计算。

更大的校验块 = 更昂贵的存储成本。

灵活使用ECC比特 = 更精细的设计与测试策略。

因此,不同应用场景需要量身定制的ECC方案。例如,企业级服务器偏好强ECC以保证稳定,而消费级设备则更关注性能与成本平衡。

学习与提升的路径

对于半导体与IC工程师而言,理解ECC不仅是理论,更是工程实践中的必备技能。EDA Academy (www.eda-academy.com) 提供了丰富的在线课程与资源,涵盖从基础的数字电路到复杂的存储架构优化。

学习机会:用户可购买最新、专业的IC设计与验证课程。

教学机会:具备经验的工程师可以注册成为导师,在平台上授课。

免费资源:只需一个邮箱即可免费订阅Newsletter,定期获得行业干货。

联盟收益:加入销售联盟计划,通过推广课程可获得20%–50%的佣金。

从汉明码到DDR5的芯片内ECC,错误纠正技术的发展历程,折射出计算体系不断追求可靠性的努力。在“算力即生产力”的今天,保障数据安全的每一位比特,都关乎整体系统的稳定与性能。

对于工程师、学生和研究者来说,理解ECC,不仅是对知识的掌握,更是对未来职业发展的投资。而像EDA Academy 这样的平台,正是让理论与实践相结合的最佳桥梁。

浙公网安备 33010602011771号

浙公网安备 33010602011771号