5、论存储器组织

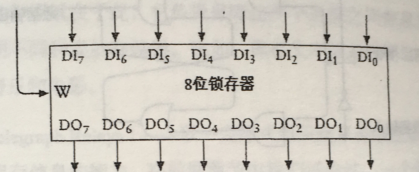

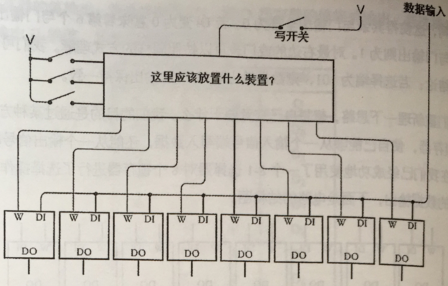

先前我们学习了锁存器,8位锁存器图如下:

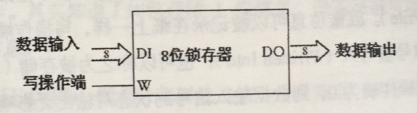

简化图如下:

假如现在我们只有一个灯泡,我们想用一个输入和一个输出来存储这8位输入、输出8位。

我们就需要增加3个开关,因为3个二进制可以表达8个数,正好对应了我们的8位。

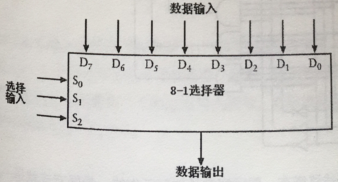

要实现的效果图如下:

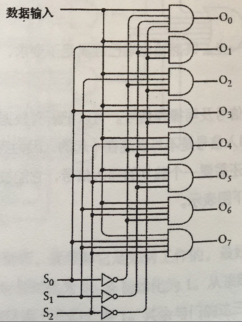

在标注这是什么装置?的装置中,其实是一个“8-1选择器”,其简化图如下:

我们所要达到的真值表的目的是:

| 输入 | 输出 | ||

| S2 | S1 | S0 | Q |

| 0 | 0 | 0 | D0 |

| 0 | 0 | 1 | D1 |

| 0 | 1 | 0 | D2 |

| 0 | 1 | 1 | D3 |

| 1 | 0 | 0 | D4 |

| 1 | 0 | 1 | D5 |

| 1 | 1 | 0 | D6 |

| 1 | 1 | 1 | D7 |

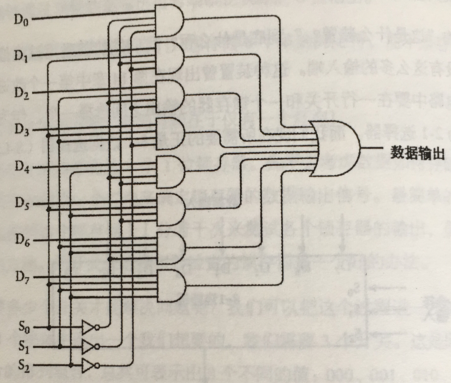

8-1选择器主要有:三个反向器、八个4端口输入与门、一个8端口输入或门,系统的组织结构如下图:

可以分别把S0 S1 S2对应一个值带进去看看工作原理是什么。下面是电路结构图:

现在我们已经走完一半了,就差输入端了。

其实解决问题的思路有很大的相似,无非是我们想利用开关和数据输入来控制写入端,哪个是可写的。

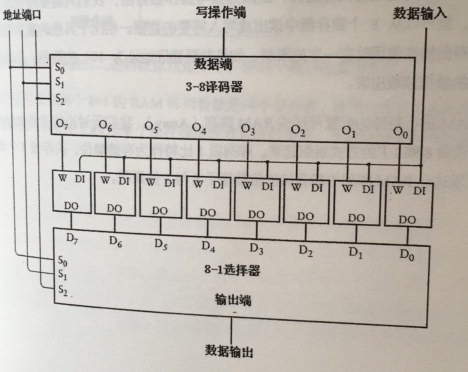

而图中的这款器件,我们叫做3-8译码器。

3-8译码器输出的端口共有8个,在任何时刻,译码器只会有一个锁存器的输出位1,其余均为0.每一个输出端的结果都是由S0、S1、S2这三个信号的排列组合决定的。而数据的输出和输入一致,如下图所示:

译码器逻辑表如下:

| 输入 | 输出 | |||||||||

| S2 | S1 | S0 | O7 | O6 | O5 | O4 | O3 | O2 | O1 | O0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Data |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | Data | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | Data | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | Data | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | Data | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | Data | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | Data | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | Data | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

将8个锁存器加入到电路就形成了完整的系统:

译码器和选择器具有相同的选择信号,上图中,这三个信号一起被称为地址端口。

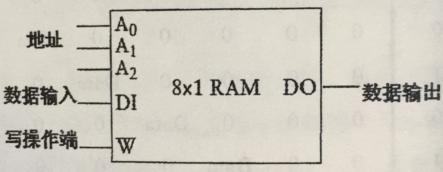

这种配置下的锁存器在有的资料中也被称为读/写存储器(read/write memory),但更普遍的叫法是随机访问存储器(Random Access Memory),或RAM。可以认为我们讨论的这种存储器是可存储8个独立比特的RAM,它的简化结构图如下:

之所以被称为随机访问存储器,是因为读写操作很自由,我们只需要改变地址及相关的输入,就可以从8个锁存器中读出或写入需要的数据。相比于其他的顺序型存储器,这种存储器在使用时有一定的限制,如果想要读取地址为101的数据,必须先把地址为100的数据读取出来。

将RAM进行特殊的配置可形成RAM阵列(Array),我们所讨论的这种RAM阵列以8X1的方式组织起来的。阵列以1比特作为存储单位,共存储8个单位的数据。所以这个RAM阵列中能存储的位数等于8与1的乘积。

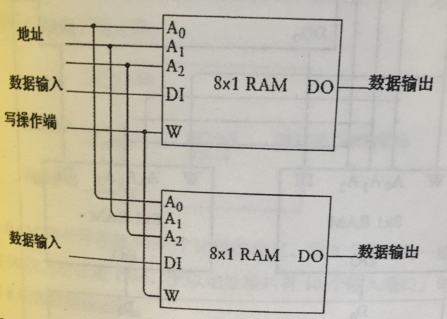

RAM阵列组合形式多种多样。比如我们可以通过共享地址的方式可以把两个8X1的RAM阵列连接起来,如下图:

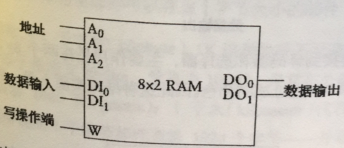

我们把这两个8X1的RAM阵列的地址和输出分别都看成一个整体,这样就得到了一个8X2的RAM的RAM阵列,如下图:

这个RAM阵列可存储的二进制数依然是8个,但是每个数位宽为2位。

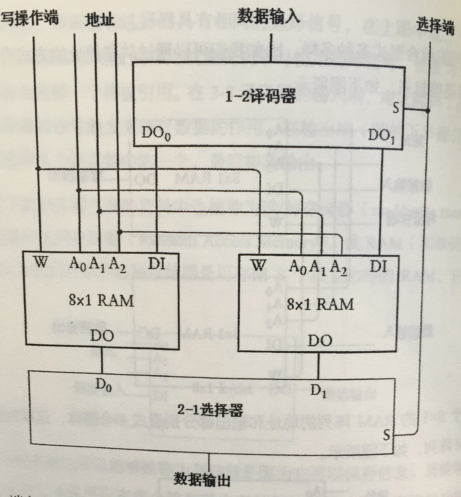

我们还可以把两个8X1的RAM阵列看做是两个锁存器,使用一个2-1选择器和一个1-2译码器就可以把它们按照单个锁存器连接方式进行集成,电路图如下:

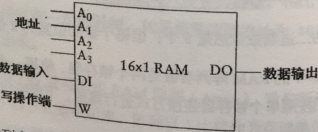

“选择”端之所以连接到译码器和选择器,主要作用是在两个8X1 RAM阵列中选择一个,本质上它扮演了第4根地址线的角色。因此这种结构实质上是一种16X1的RAM阵列,如下图:

上图中的RAM阵列存储容量为16个单位,每个单位占1位。

RAM阵列的存储容量与其地址输入端的数量有直接的联系。在没有地址输入端的情况下(只有1位锁存器和8位锁存器的情况下),只能存储1个单位的数据;当存在1个地址输入端时,可以存储两个单位的数据;在有两个地址输入端时,可以存储4个单位的数据;有3个地址输入端时,可以存储8个单位的数据;有4个地址输入端时,可以存储16个单位的数据。我们可以把它们之间的关系归纳成如下等式:

RAM阵列的存储容量=2地址输入端个数

那为何不搭建一个大规模的RAm阵列呢?就像下面这样:

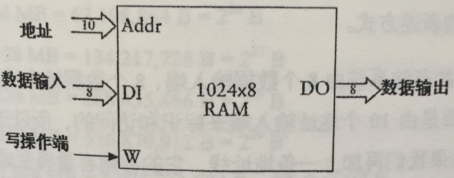

上面的RAM阵列可存储8192个比特的信息,每8个比特为一组,共分为1024个组。因为2的10次方恰好时1024,所以地址端口共有10个输入端口。电路还包括8位的数据输入端和8位数据输出端。(1KB=1024B)

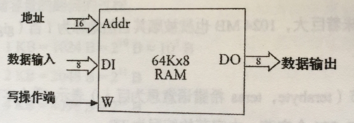

而更多的时候,我们用到的地址数如下:

因为16正好可以用两个字节进行寻址(64K)

64kb的内存是1980年的个人电脑的主流配置,但它的确不是用电报继电器组成的。我们可以用继电器来组成一块内存吗?我相信你也不想这么做。在先前的讨论中,存储每个比特需要9个继电器,推算一下64kx8的RAM阵列就需要至少500万个继电器!

如果用一种控制面板来辅助我们管理对这块64KB存储器的操作——包括写数据和读数据,一切将会直观明了。在这款控制面板上,有16个开关用于控制地址位,还有8个开关用来控制要输入的8比特数据。写操作端也用一个开关来表示,8个灯泡用来显示8位数据,这个控制面板如下图:

初始状态下所有的开关均置为0.其中右下角有一个标识为控制端(takeover)的开关,这个开关的作用是确定由控制面板还是由外部所连接的其他电路来控制存储器。如果其他电路链接到与控制面板相连的存储器,这时控制端置0,此时存储器由其他电路系统接管,控制面板上的其他开关将不起任何作用;当控制端置1时,控制面板将重新获得对存储器的控制能力。

这些功能可以用一些2-1选择器来实现。仔细数一下会发现,我们需要25个2-1选择器——其中包括16个地址输入端、8个数据输入端,以及一个写操作端。电路如下图:

当控制端开关断开时,RAM阵列的地址端、数据输入和写操作端的数据全部来源于外部信号,也就是在2-1选择器的左上角的输入信号;当控制端开关闭合,RAM阵列的地址端、数据输入端和写操作端的数据来源于控制面板开关发出的信号。但最终RAM阵列的输出信号都会传到8个灯泡上或其他可能的地方。

下图是64Kx8RAM阵列的逻辑结构框图:

当控制端开关闭合时,通过操作16个地址开关,可以选择65536个地址中的任何一个,灯泡的状态将表示该地址中所保存的8位数据。我们可以使用8个数据开关表示一个新数,然后把操作端置1,从而将数据写入存储器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号