FPGA回忆记事(一):基于Nios II的LED实验

实验一:基于Nios II的LED实验

一、 创建Quartus II工程

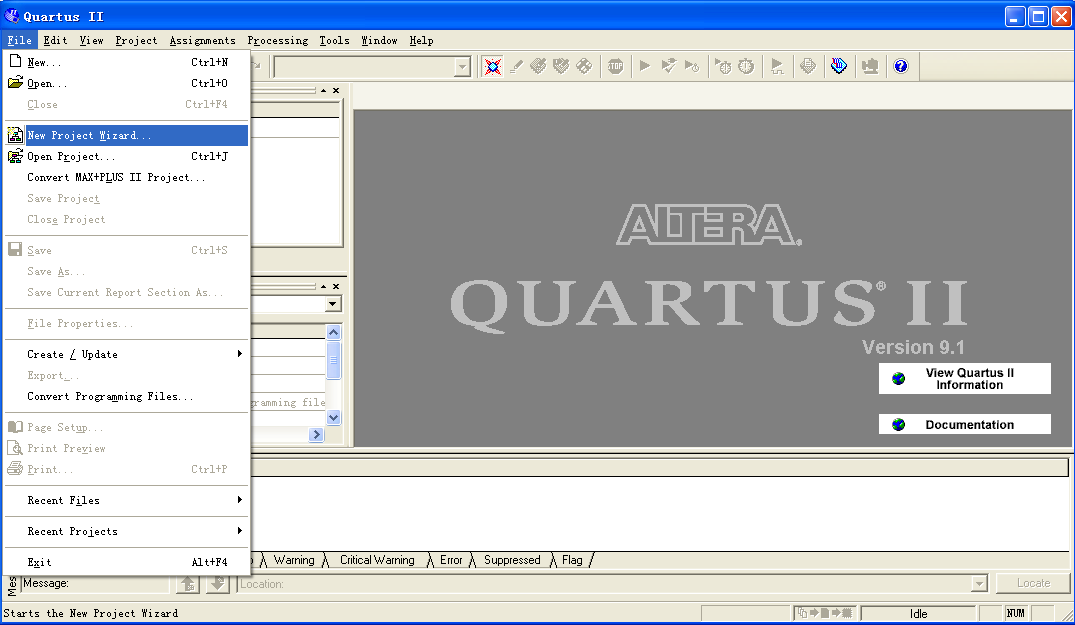

1、打开Quartus II环境。开始->程序->Altera->Quartus II 9.1。

2、点主菜单File->New Project Wizard…,创建新工程。

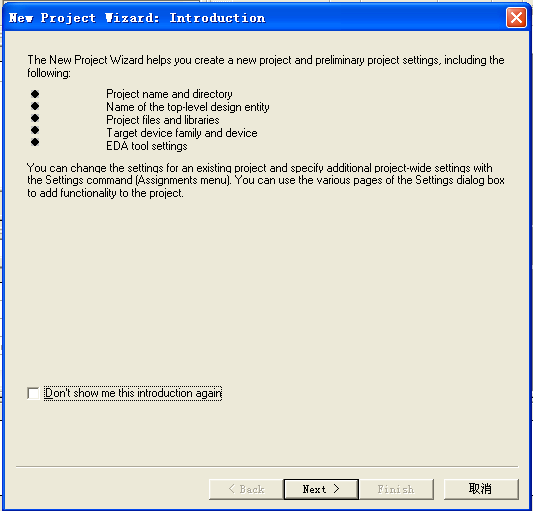

3、弹出如下窗口,点Next,进行下一步操作。

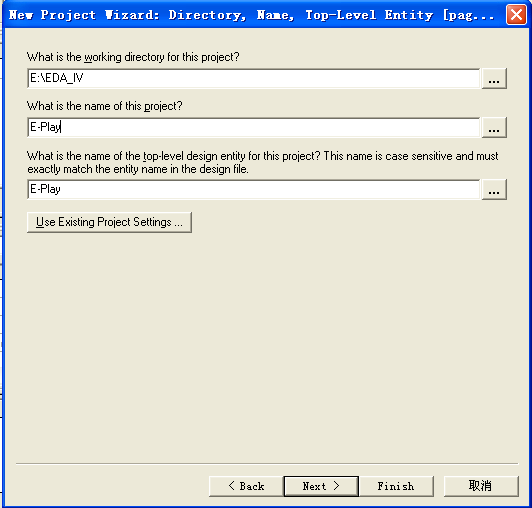

4、输入新建工程路径,工程名及工程顶层实体,点Next,下一步。

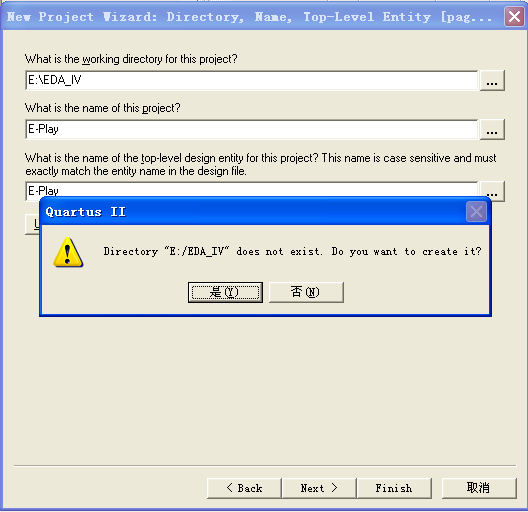

如所输入工程路径文件夹不存在,则会弹如下窗口,点“是”,创建工程文件夹。

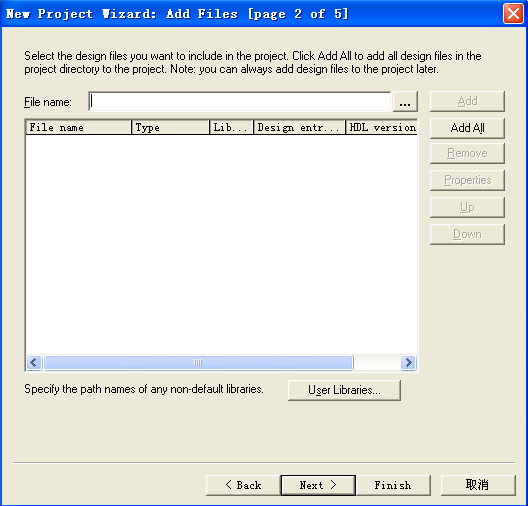

5、弹出如下窗口,按默认,点Next,下一步操作。

6、选择目标板上对应的正确芯片型号,点Next,下一步操作。

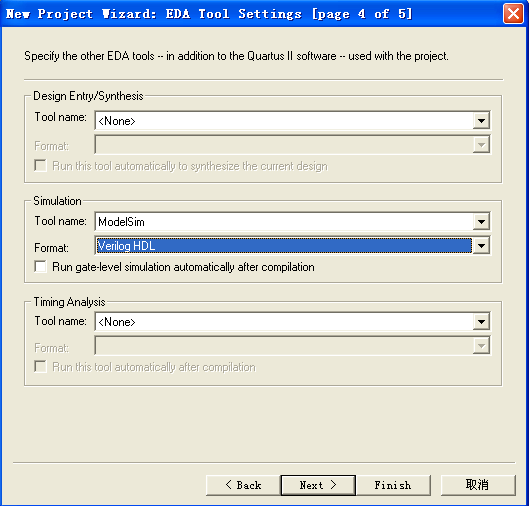

7、设置仿真格式,选择Verilog HDL,点Next,下一步操作。

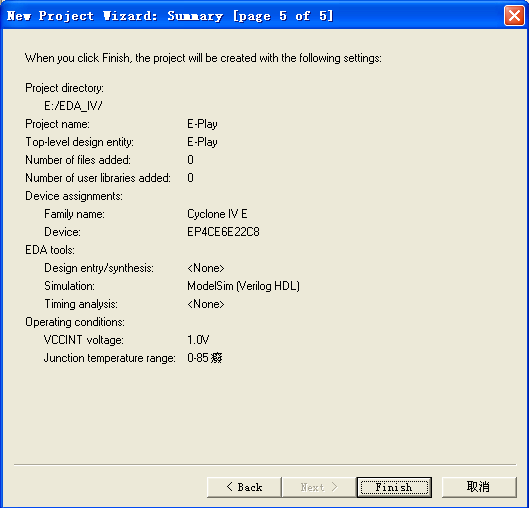

8、点Finish,完成工程结构创建。

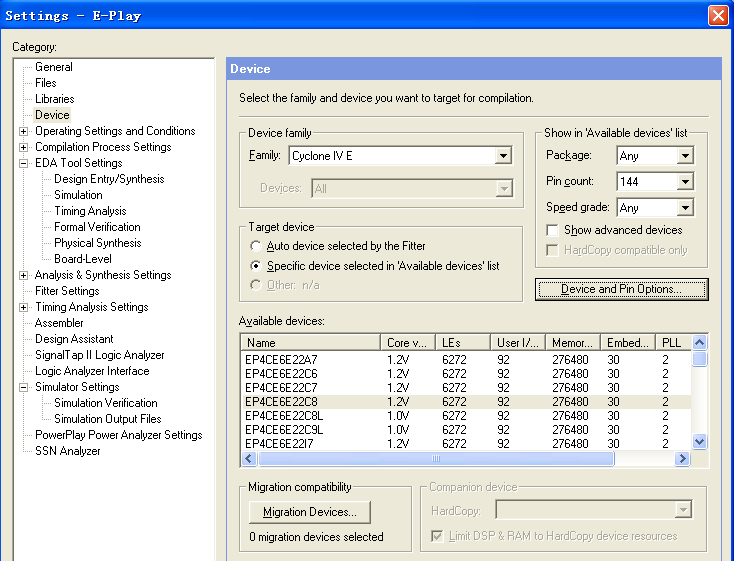

9、点击Assignment-Device。

10、选择Device & Pin Option,进行器件及管脚选项设置。

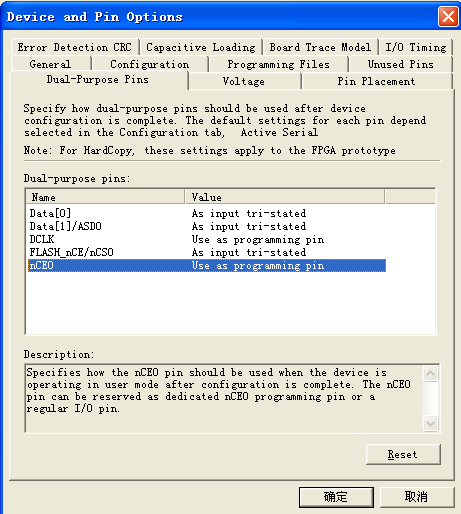

11、选择Dual-Purpose Pins,在弹出的如下对话框中双击Use as programming pin,然后在下拉框中选择Use as regular I/O,点确定,点OK。

12、选择Unused Pins选项,把没用到管脚设为三态输入“As input tri-stated”,其它选项按默认,点确定,完成设置。

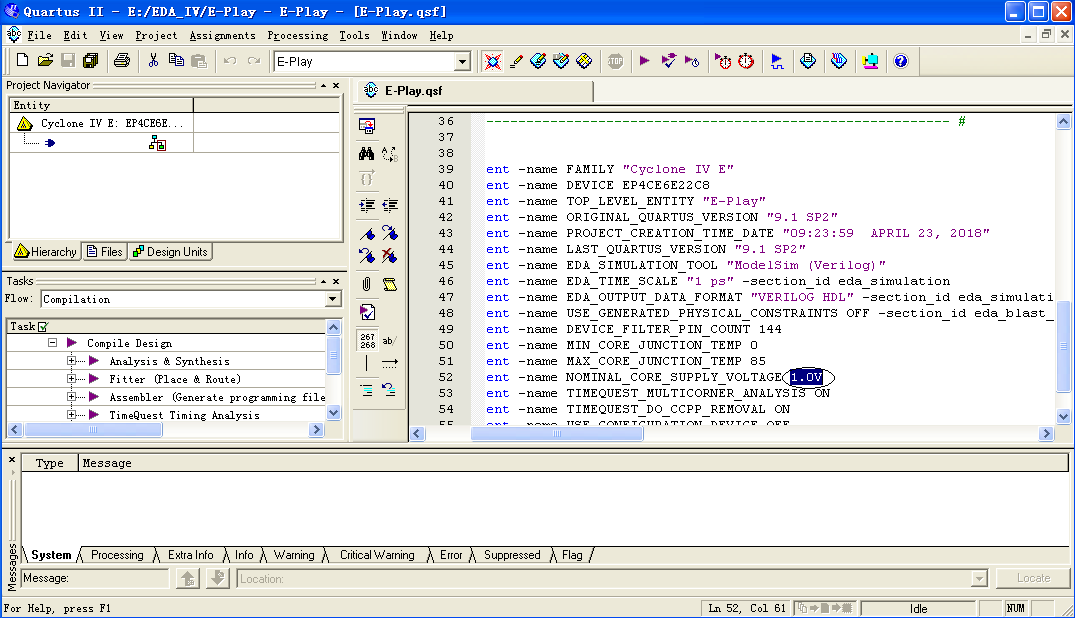

13、附:由于芯片变更,将需要做如下调整以适应新的芯片核心电压,步骤如下:

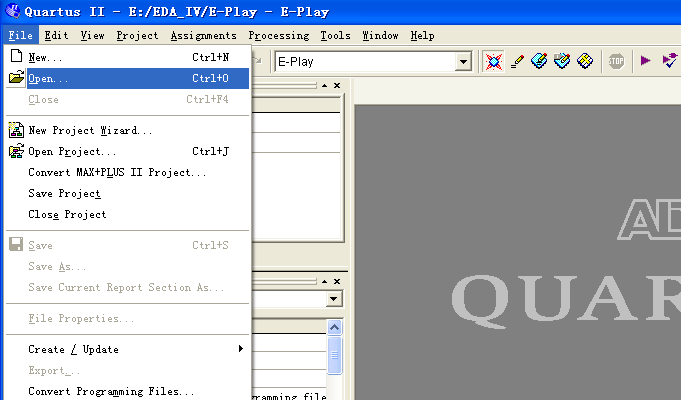

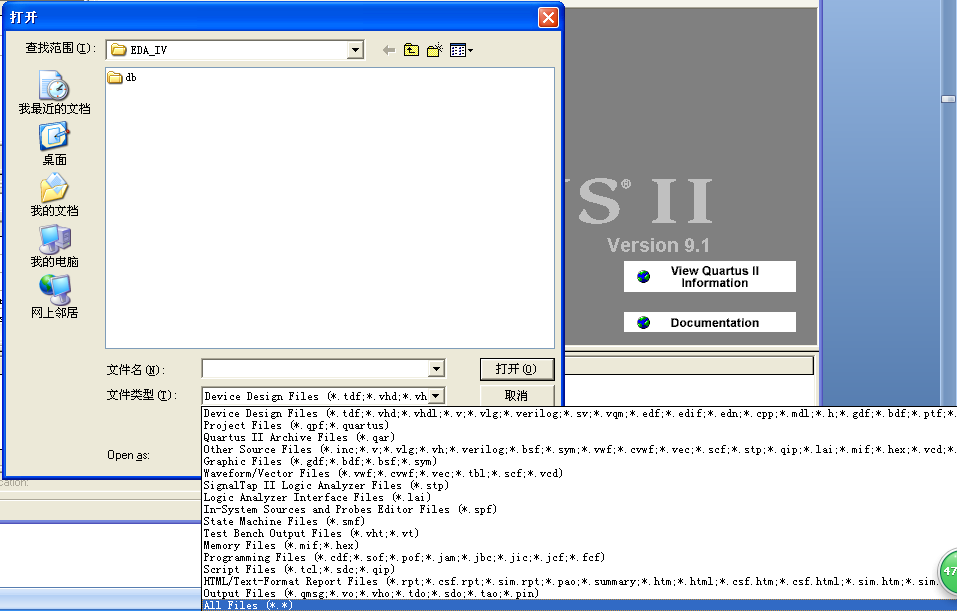

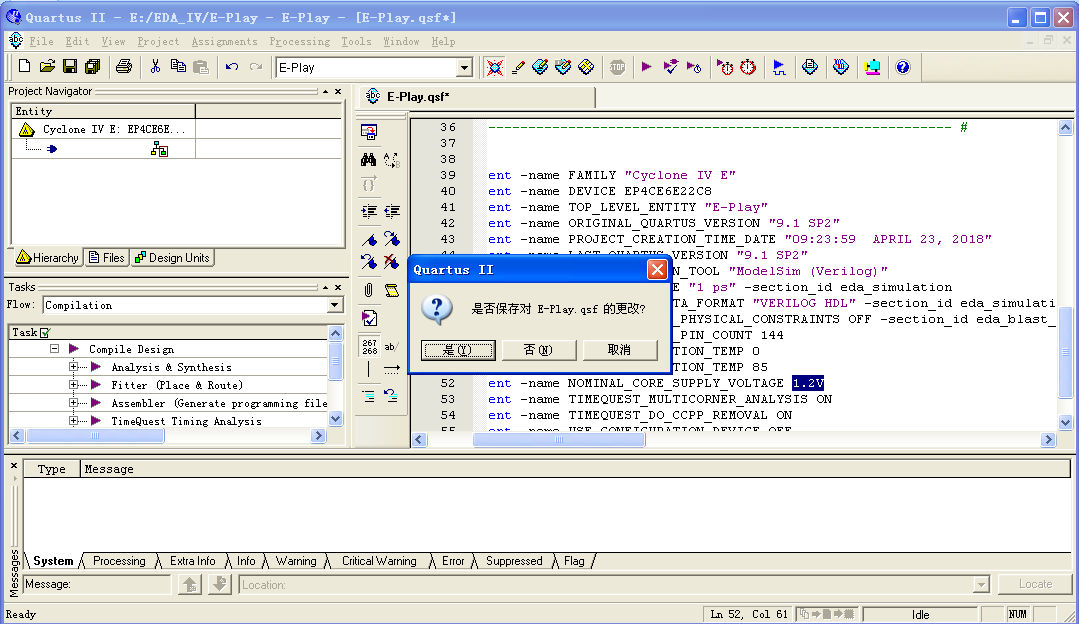

1.选择file-open并将工程所在路径打开如图:

2.选择File菜单下的open,在文件类型下拉框中选All files,在所在工程文件夹下找到.qsf文件打开。

3.将set_global_assignment-name NOMINAL_CORE_SUPPLY_VOLTAGE 1.0V后面的1.0V改为1.2V。然后保存。

二、SOPC Builder创建系统模块

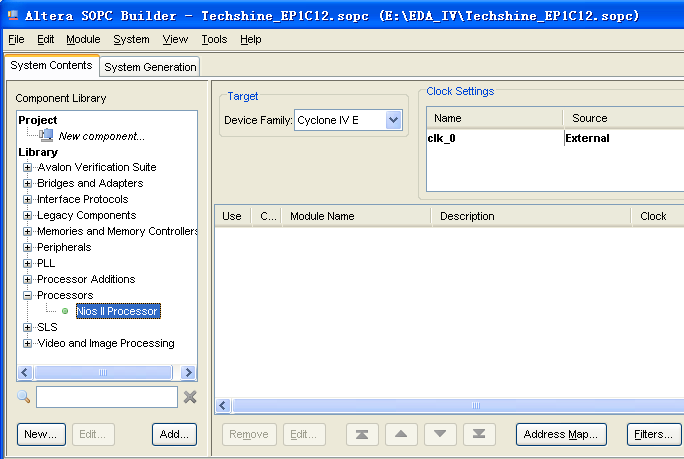

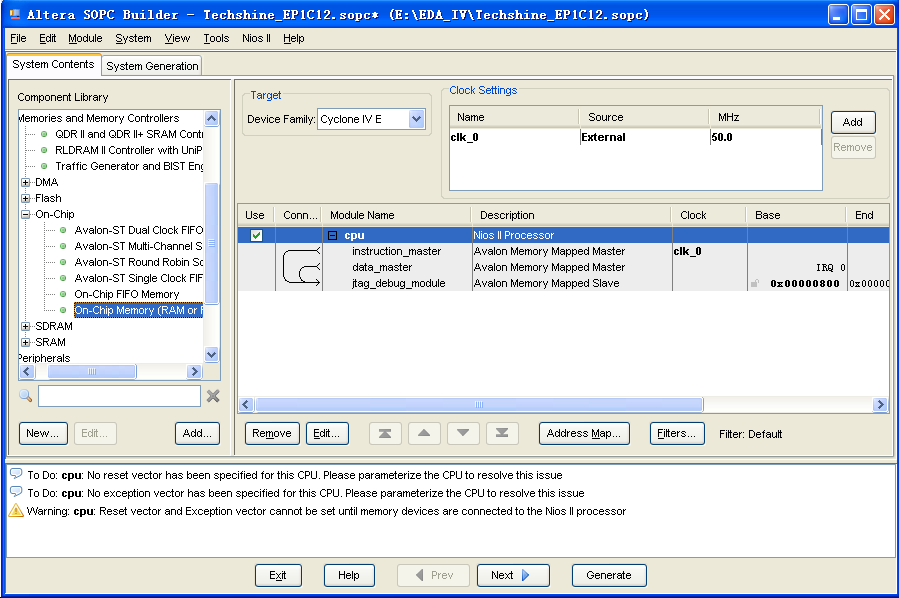

1、 在Quartus II环境中选择菜单Tools->SOPC Builder…,打开SOPC Builder向导。

2、创建新系统,输入系统模块名称,如“Techshine_EP1C12”,选择适当的目标描述语言。

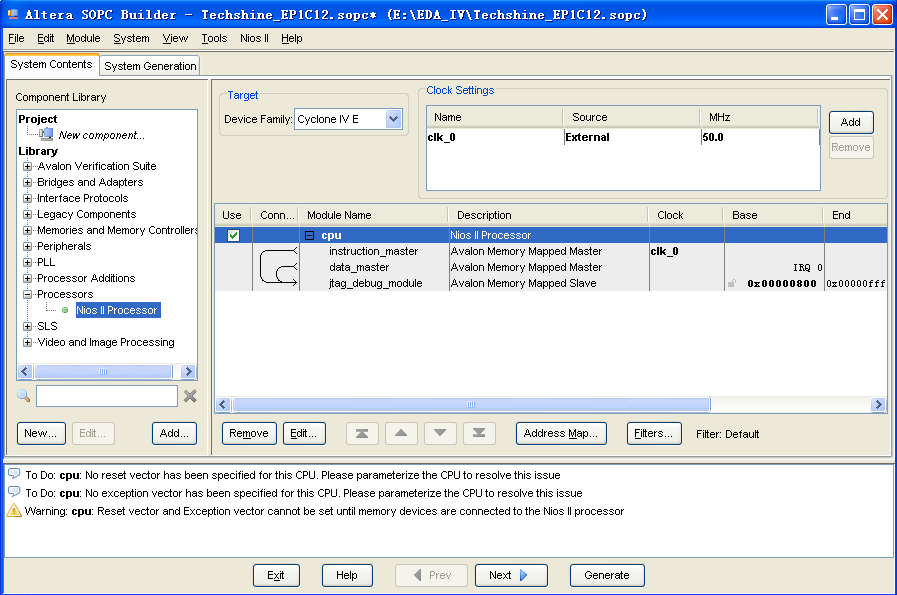

3、在左端元件池窗口列表中选处理器项,点Add…或双击鼠标左键,添加CPU。

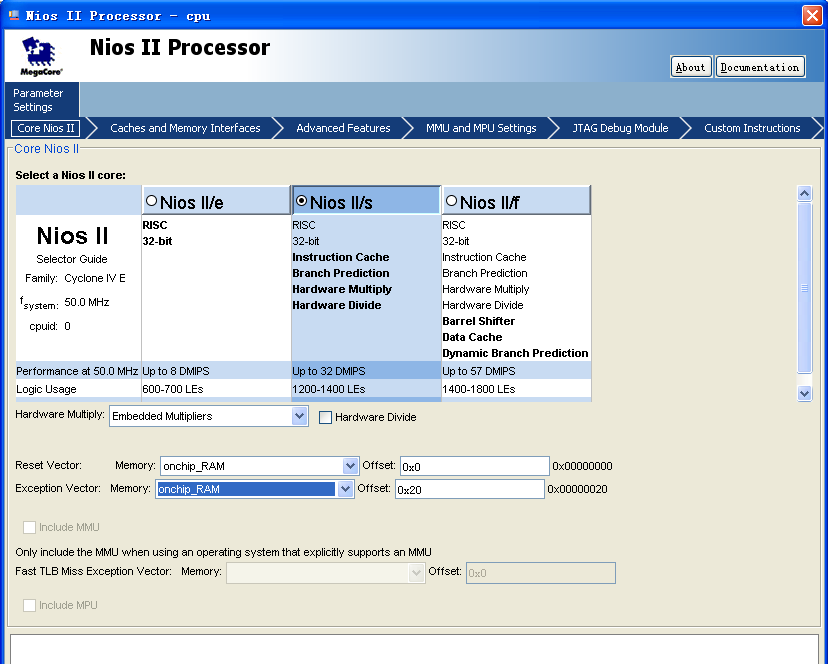

4、选择适当的NIOS II Core,推荐用“Nios II/s”模式,点Next,进一步设置

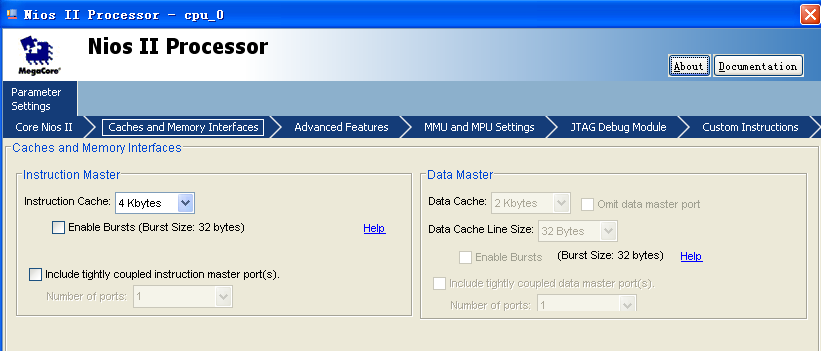

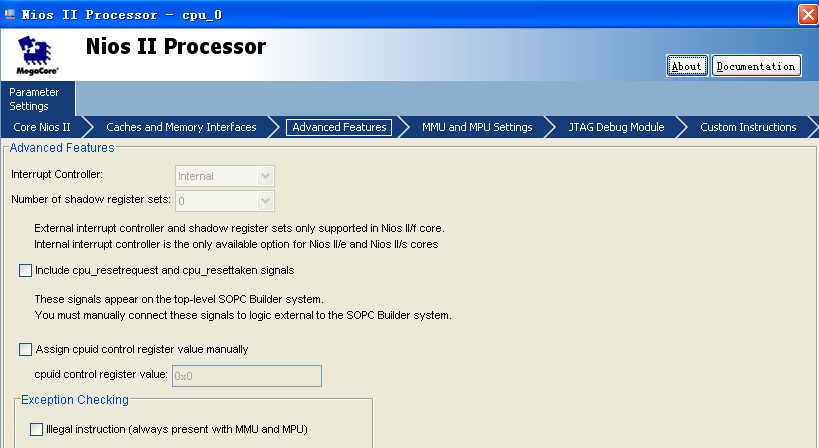

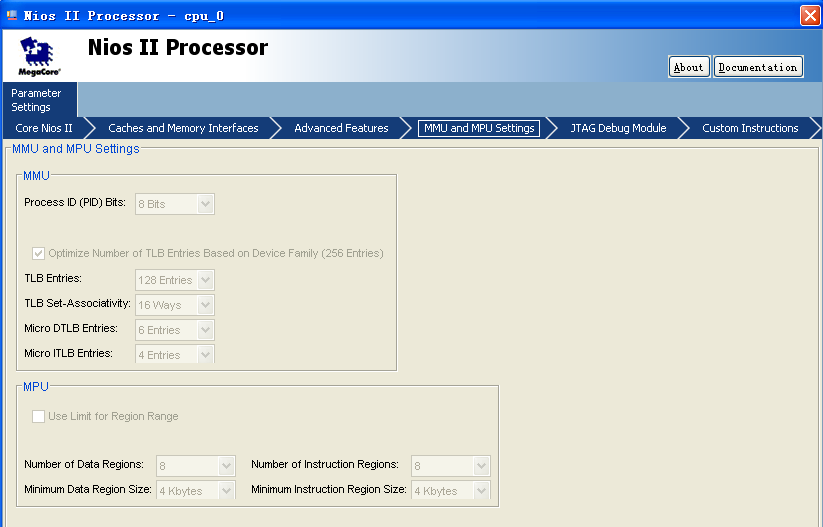

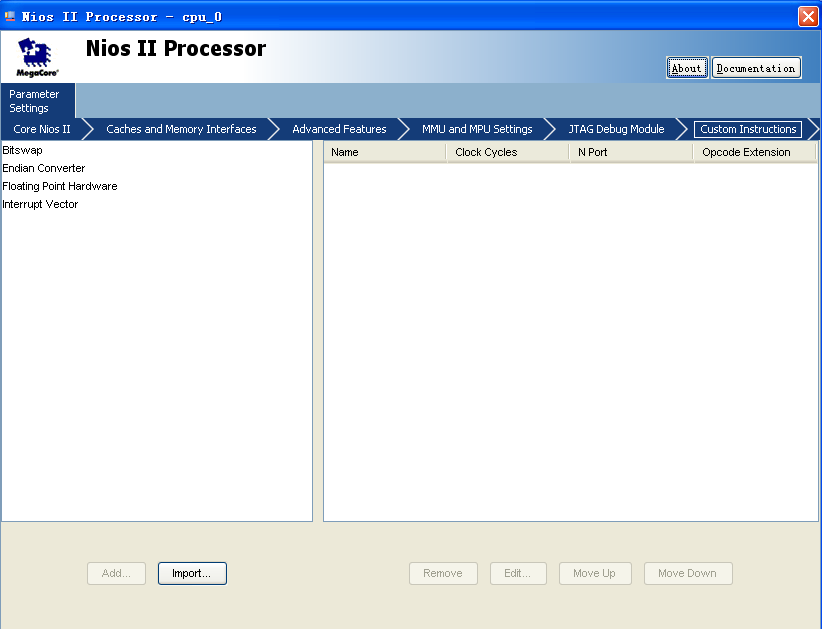

5、对Cashes and Memory Interfaces设置、Advanced Features设置、MMU and MPU settings设置,可选择默认,点Next,下一步设置。

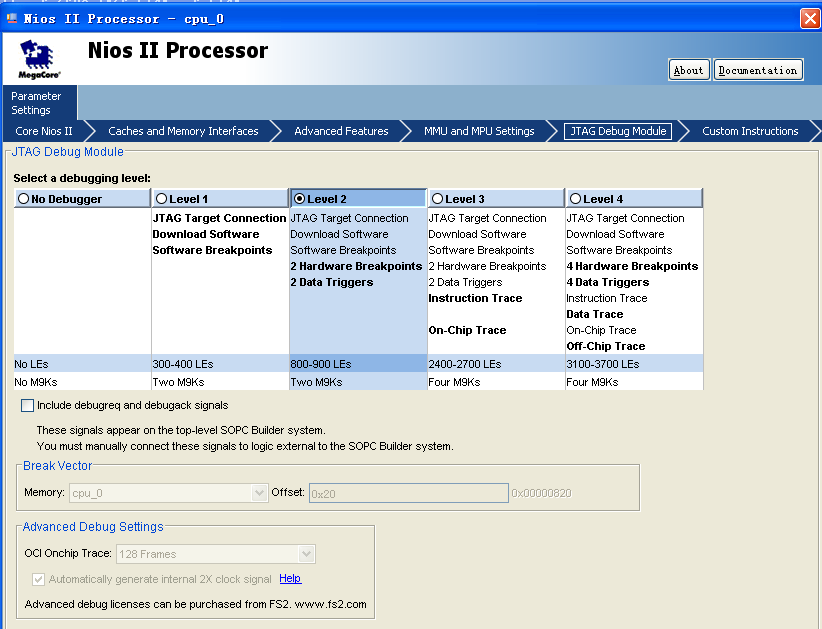

6、选择适当的JTAG Debug Module,推荐设为“Level 2”以上级别,点Next,选择默认,点Finish,完成创建CPU。

7、在右边目标资源窗口中,鼠标右键点新建的CPU项,选择Rename,对新建的CPU改名。

默认为“cpu_0”,改为“cpu”。

8、在元件池Memory下,选择On-Chip Memory(RAM or ROM),添加片上存储器。

9、弹出片上存储器选项,选RAM,大小设置为8Kbytes,点Finish,完成设置,并改名为:onchip_RAM。

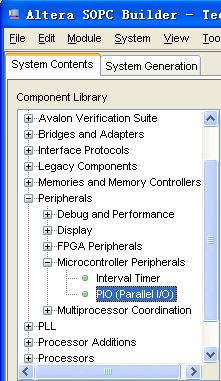

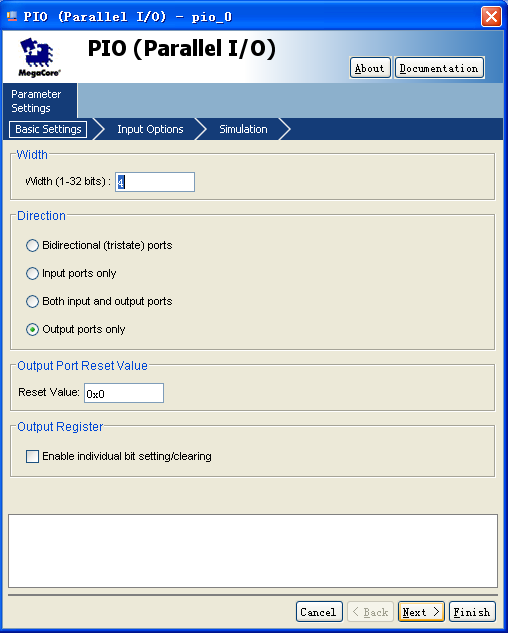

10、在元件池Peripherals下,选择Microcontroller Peripherals,选择PIO,点Add…或双击鼠标右键,添加IO。

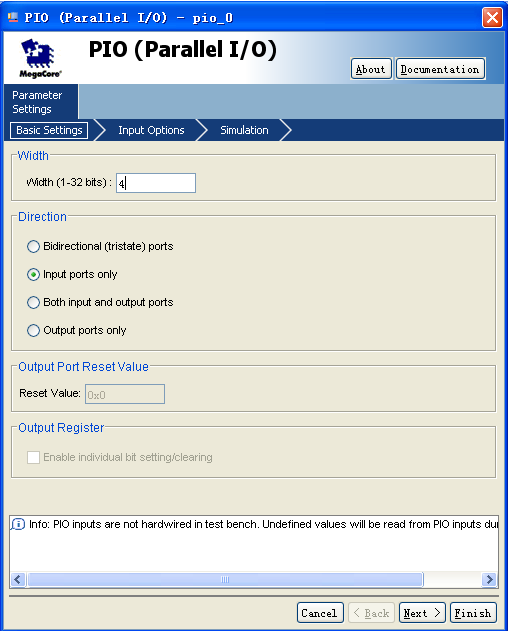

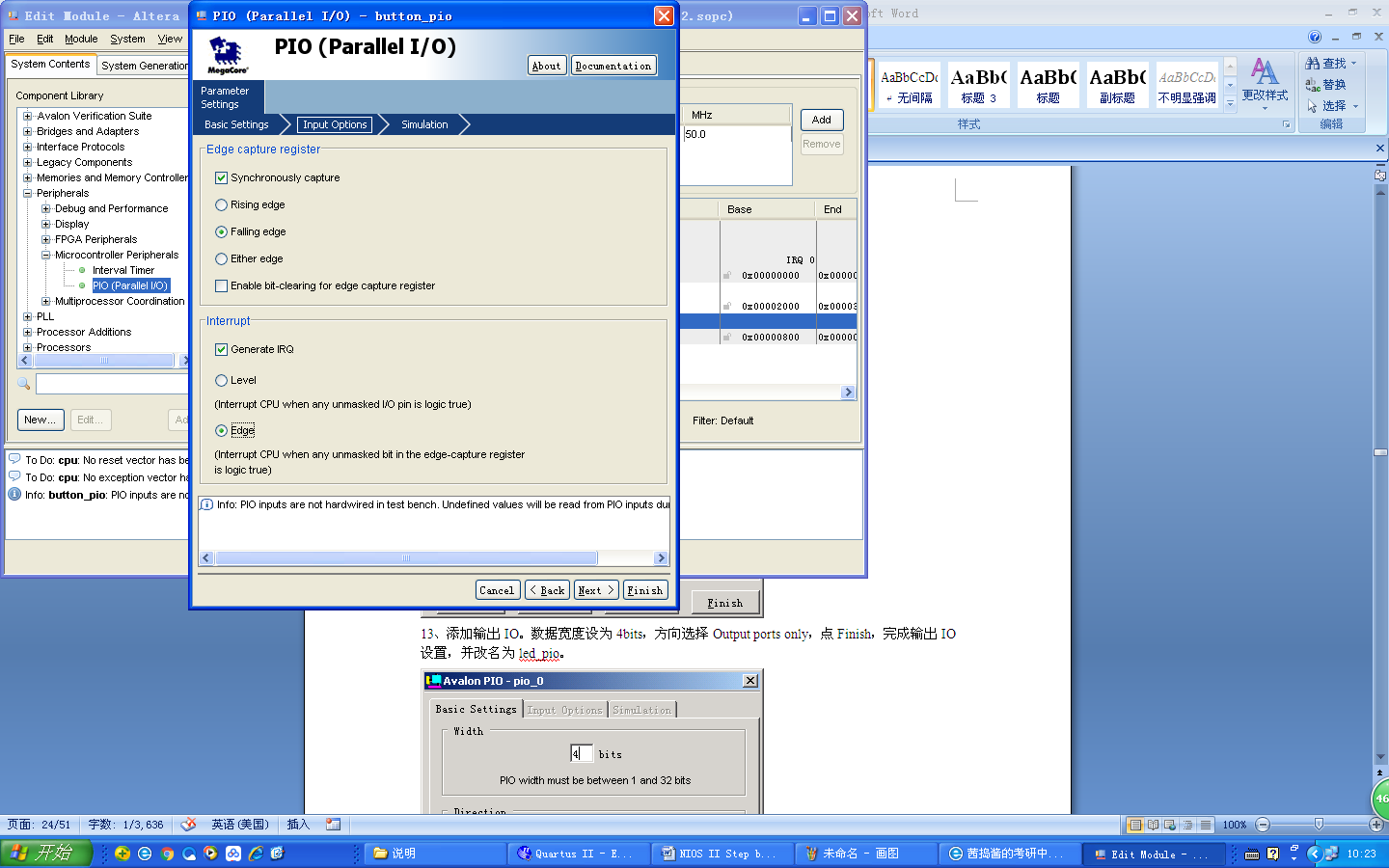

11、添加输入IO,设置数据宽度为4bits,方向选择Input prots only。点Next,下一步设置。

12、设置适当的中断方式,点Finish,完成设置,并改名为button_pio。

13、添加输出IO。数据宽度设为4bits,方向选择Output ports only,点Finish,完成输出IO设置,并改名为led_pio。

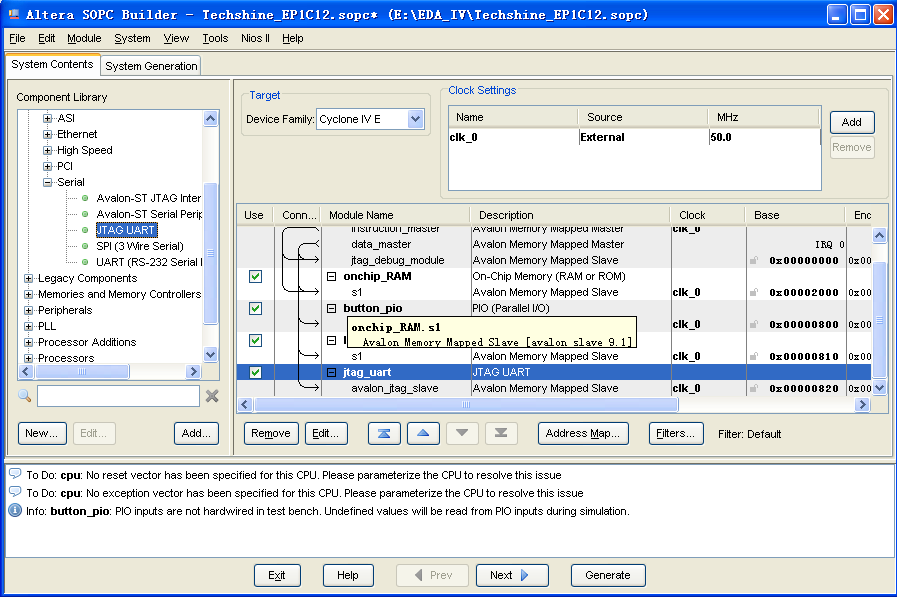

14、在元件池Interface Protocols/Serial下选JTAG UART,添加JTAG通信接口,按默认设置完成器件添加,改名为jtag_uart。

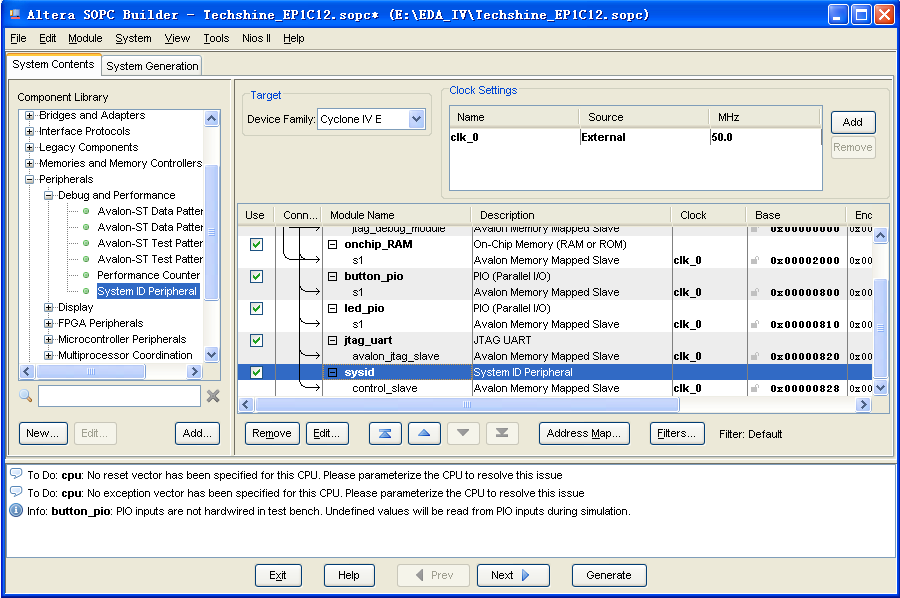

15、在元件池Peripherals/Debug and Performance下选System ID Peripheral,添加sysid。

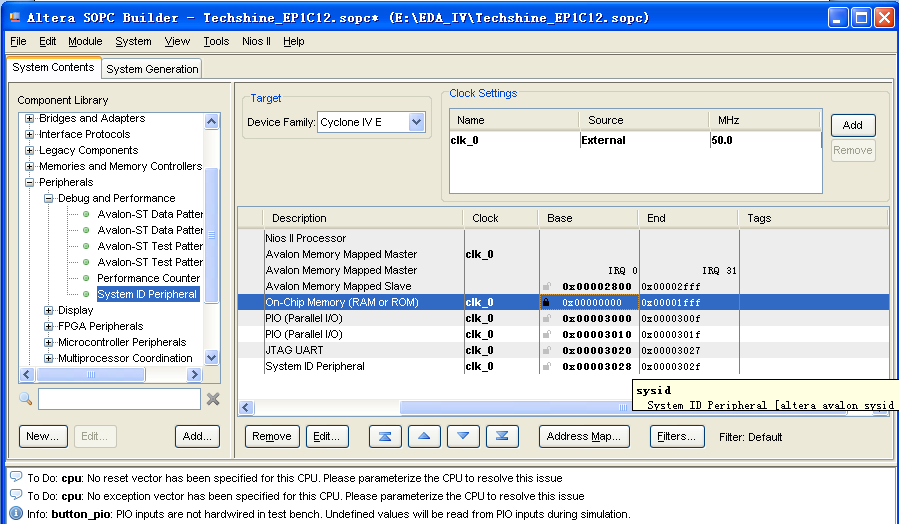

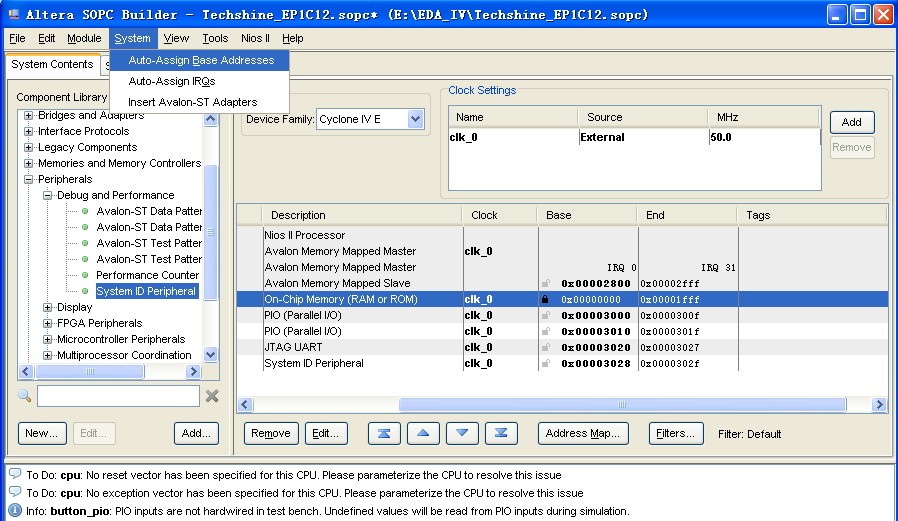

16、鼠标左击选中onchip_RAM对应的基地址,修改值为:0x00000000,在主菜单上选择ModuleàLock Base Address,锁定基地址。

17、主菜单上选择SystemàAuto-Assign Base Addresses,对未锁定地址的器件进行自动分配地址;主菜单上选择SystemàAuto-Assign IRQs,自动分配中断号。点Next,下一步操作。

18、右击CPU,在Edit中找到Core Nios II,在下方设置Reset Address和Exception Address为onchip_RAM。点击Finish。

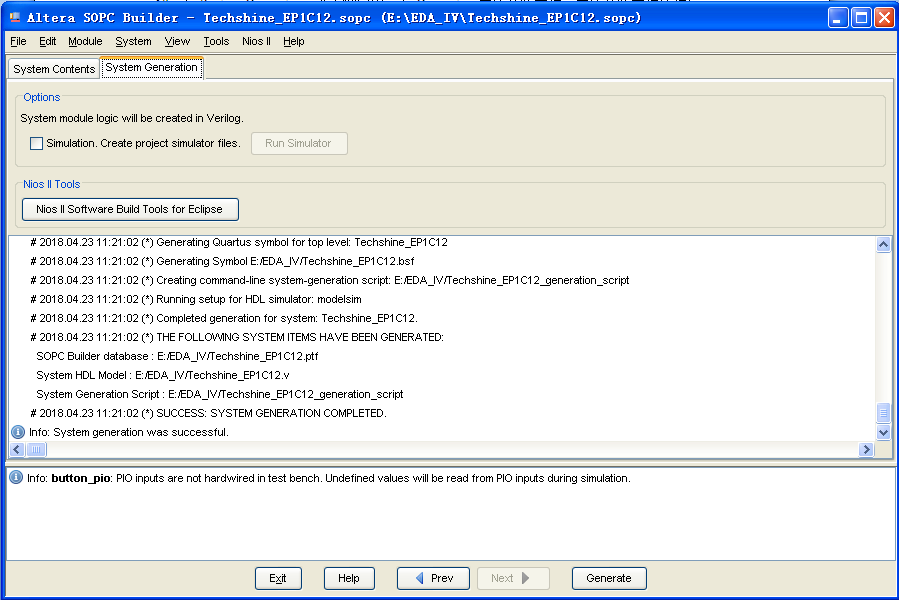

19、在System Generation 设置窗口中,点Generate,生成系统模块。生成系统模块成功后,提示Press ‘Exit’ to exit。点左下角的Exit退出或直接点右上角的 关闭窗口。

关闭窗口。

三、 PLL锁相环生成

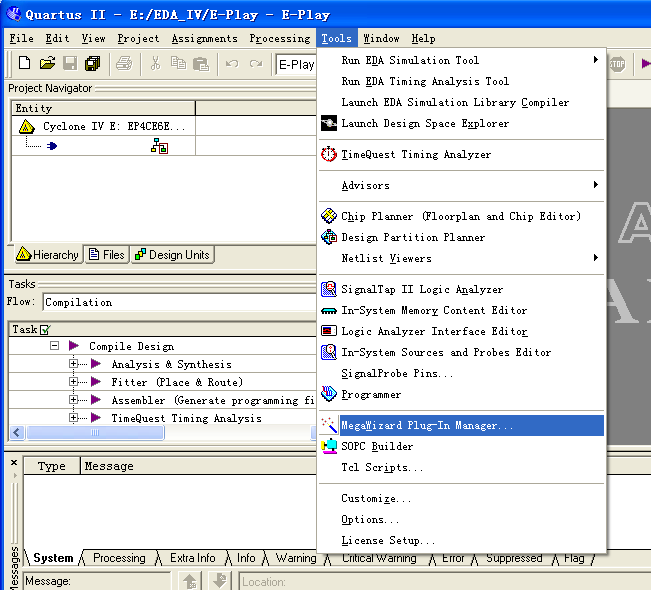

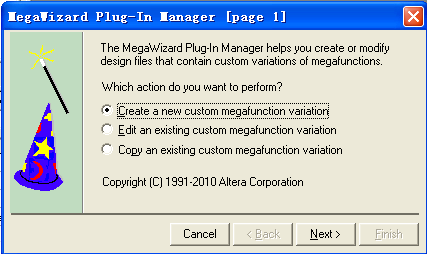

1、在Quartus II环境中,选择例化模块生成向导管理。在主菜单上选择ToolsàMegaWizard Plug-In Manager…,打开向导。

2、选择第一项Create a new custom megafunction variation,新建一个例化模块。点Next,下一步操作。

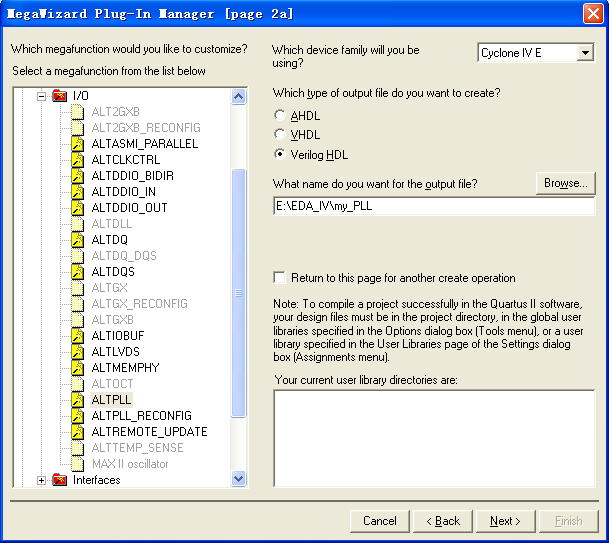

3、点开IO前的加号,选择ALTPLL,并在右边的器件选项中选择正确的器件,选择合适的输出文件硬件描述语言,在定义输出文件名处输入自定义文件名,可参考下图设置。点Next 下一步操作。

4、选择输入时钟,这里我们输入50MHz与硬件电路输入时钟相一致,其它项按默认。点Next,下一步操作。

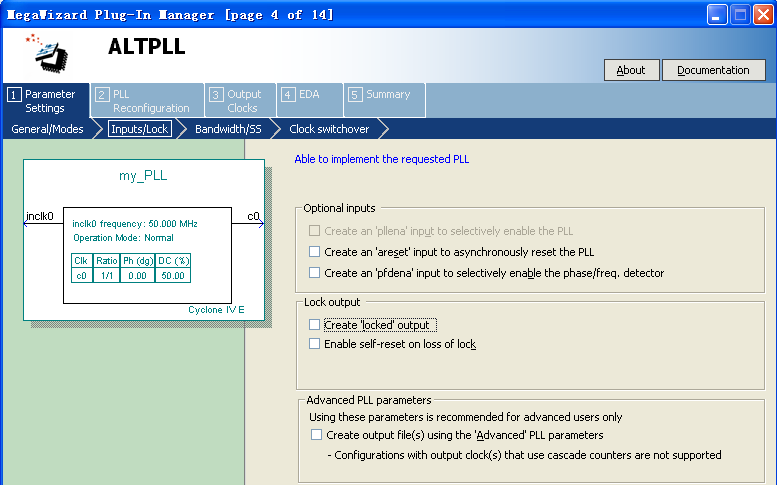

5、去掉Create an ‘areset’ input to asynchronously result the PLL项及Create ‘locked’ output项前面的勾。点Next,下一步操作。

6、其余均为默认,直到output clocks设置。c0设置,设置倍频、分频系数均为1,即c0输出为50MHz。点Next,下一步操作。

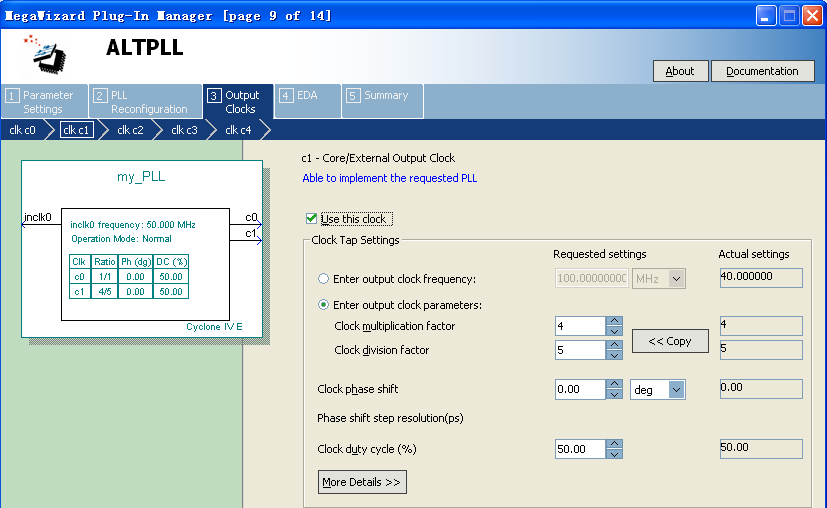

7、设置c1,设置倍频、分频系统为4、5,即c1输出为40MHz。(用作VGA时钟,此例中没用到VGA,可以不设置这一项)。点Next,下一步操作。

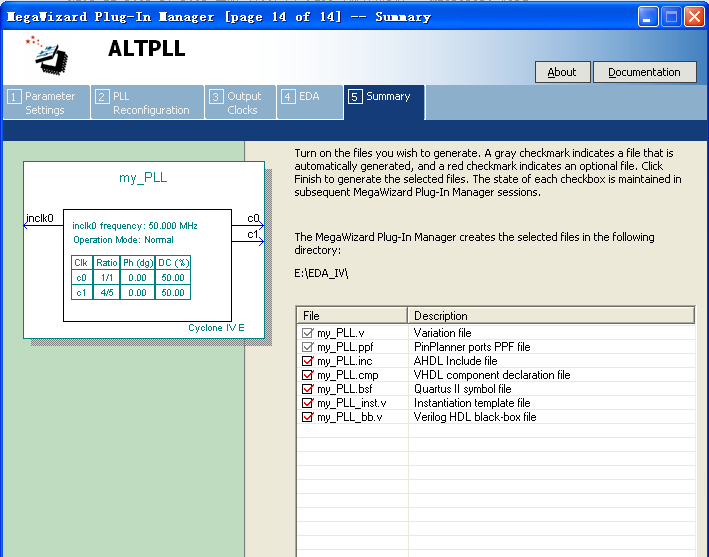

9、在输出文件设置中,把6个输出文件都点上勾。点Finish,PLL生成完成。

四、生成配置文件

1、在Quartus II环境主菜单上,选File->New…。创建新文件。

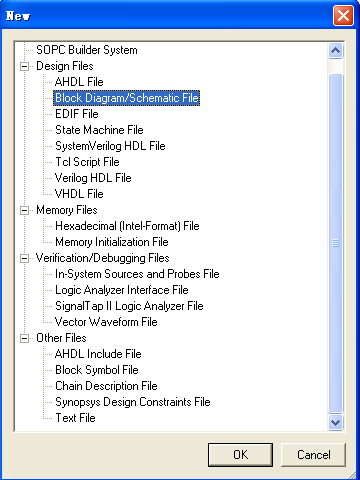

2、 在弹出创建文件类型选择中,选第二项Block Diagram/Schematic File,点OK,创建BDF文件。

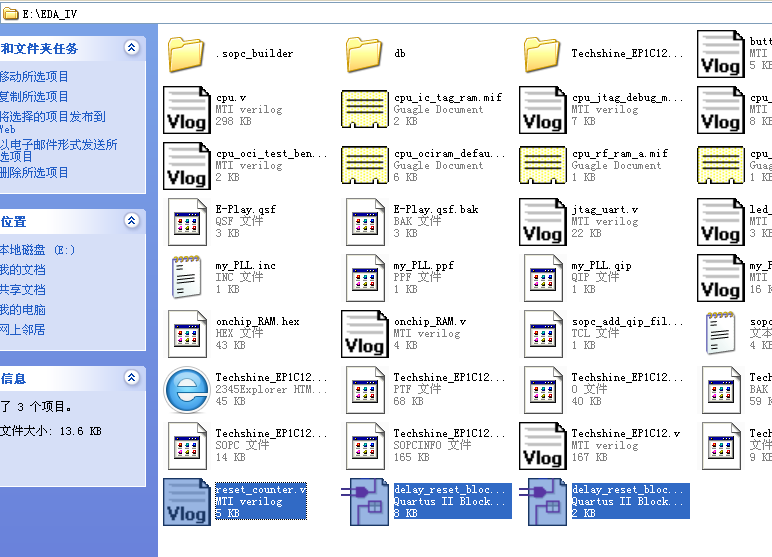

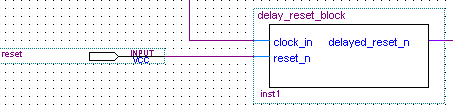

3、将tmp.rar文件解压开,将delay_reset_block.bsf、delay_reset_block.bdf、reset_counter.v三个文件复制到Quartus II工程所在的目录下,E:\EDA_VI。这是一个延时复位模块,用于PLL模块有外部输出时钟到SDRAM的情况,本例可以不用添加。

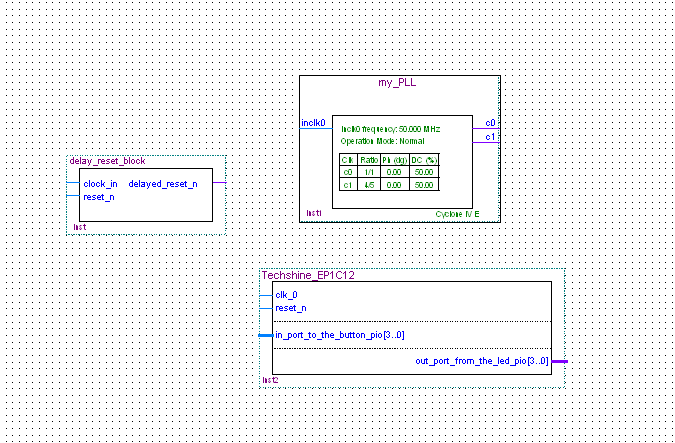

3、 双击空白处,打开模块库,在Project下将会看到三个可用模块。

4、 选中其中一个模块,点“OK”添加模块,将模块拖放到bdf文件内后,左击一次鼠标放置模块,然后右击鼠标选Cancel,一个模块添加完成。依次添加完三个模块。调整模块位置。

5、添加管脚。打开模块库,在如下图路径,找到管脚选项。点“OK”,按步骤4方法放置管脚到bdf文件中。

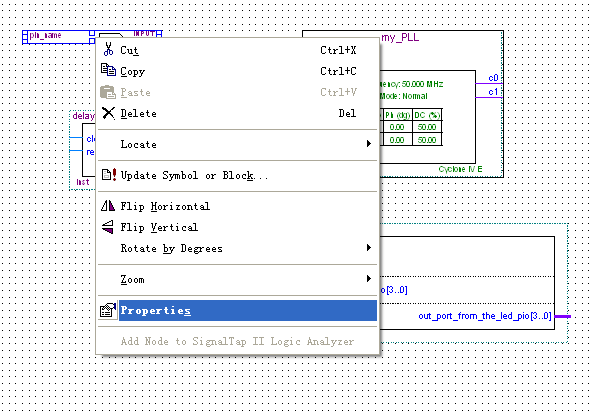

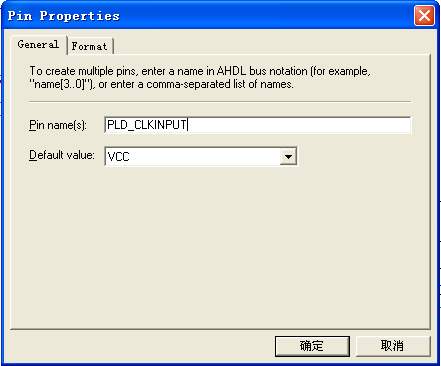

6、鼠标左键单击选中放置好的管脚,鼠标右键单击弹出菜单,选择Properties。

在弹出窗口中设置,重命名管脚名。

7、按步骤5、6依次添加及重命名其它管脚。总线按LED[3..0]的格式命名,表示数据线为从LED0到LED3共4位总线。

8、模块及管脚间连接线。当鼠到靠近管脚或模块信号引出脚时,会出现如下图所示的小十字型热点,此时按下鼠标左键,拖动鼠标即能画出电器连接线。

将鼠标一直拖到目标接点后释放鼠标左键,即完成连接,如下图所示。

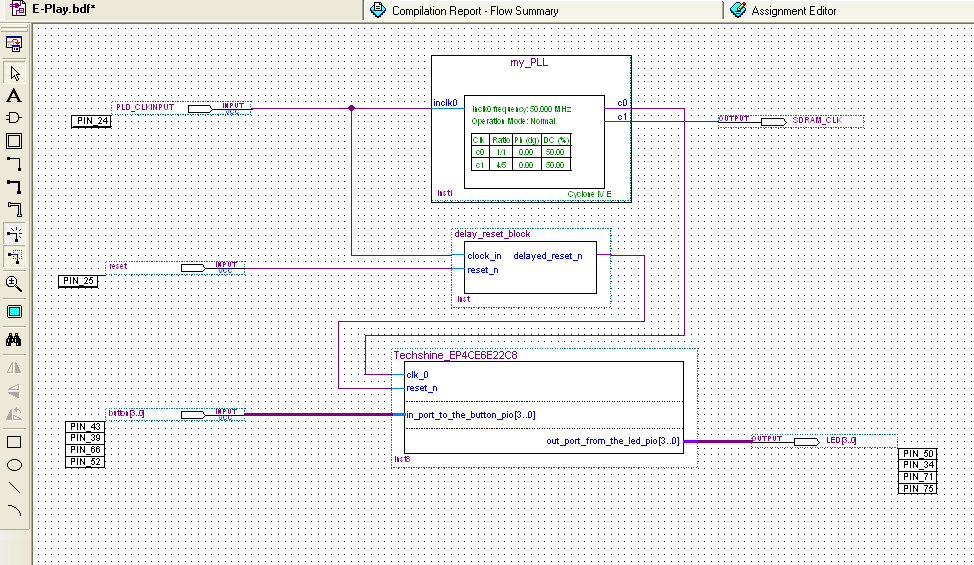

连接完成后,如下图所示。保存bdf文件为:E_Play.bdf,文件名与顶层实体名相同。

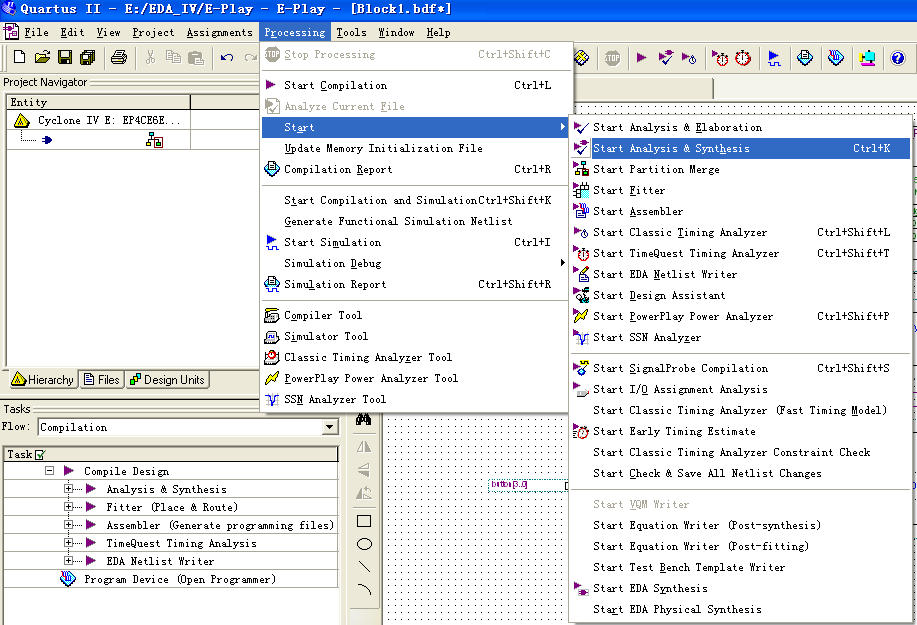

9、点主工具栏上的分析及综合按钮 ,或从主菜单中选择ProcessingàStartàStart Analysis & Synthesis。

,或从主菜单中选择ProcessingàStartàStart Analysis & Synthesis。

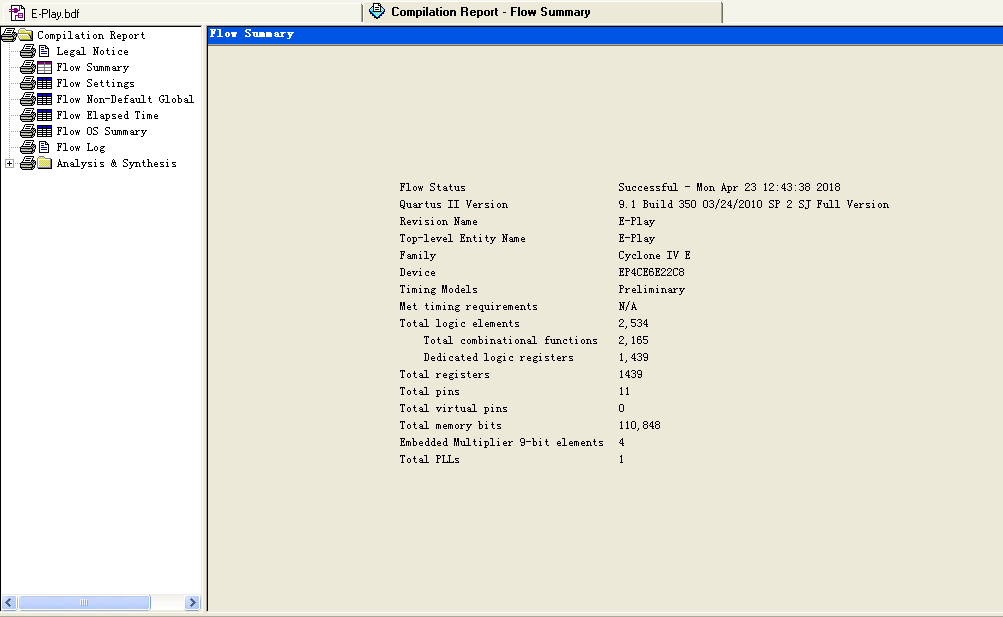

分析及综合完成,窗口显示如下。

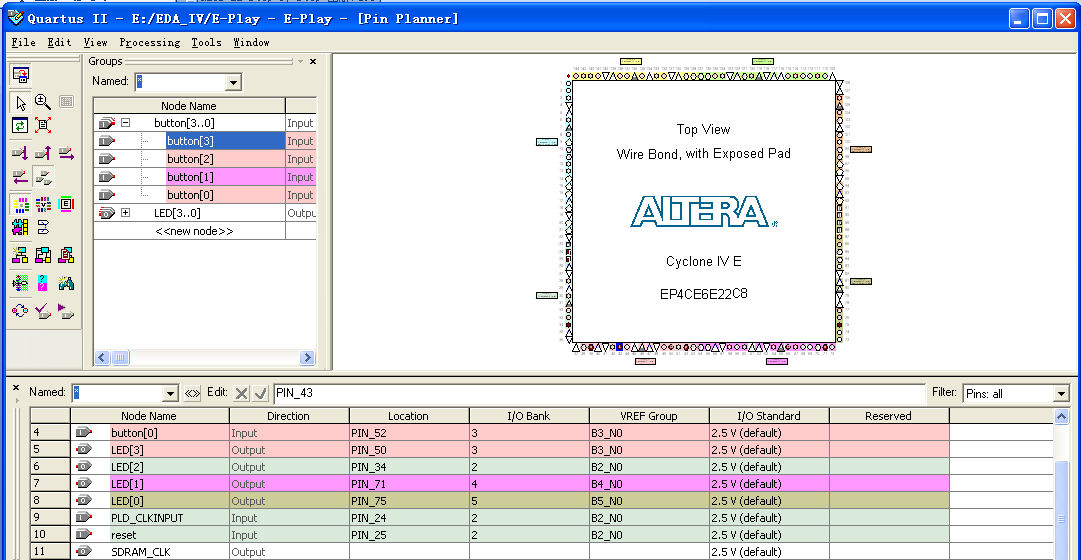

10、管脚分配。选择工具栏中的Assignment/Pins,在location一栏中键入相应数字,之后点击空白处,则会出现PIN_“所键入数字”样式,如图填好分配管脚。

之后关闭该页面,原理图呈现如下状态:

15、完全编译工程。在Quartus II环境主工具栏中选择 图标,或从主菜单下选择PressingàStart

Compilation。完成编译,显示如下图。关闭Quartus

II环境窗口。

图标,或从主菜单下选择PressingàStart

Compilation。完成编译,显示如下图。关闭Quartus

II环境窗口。

四、 NIOS应用工程

1、打开NIOS II IDE环境。开始->程序->Altera->NIOS II 5.1->NIOS II IDE。在工作路径中输入:E:\EDA_VI\software\workspace。点OK,确定。

2、第一次使用此工程路径,将显示如下Welcome窗口,点Welcome窗口左上角的叉,关闭即可。

3、创建NIOS II 应用工程。在NIOS II IDE环境主菜单下选择File->New->Project……

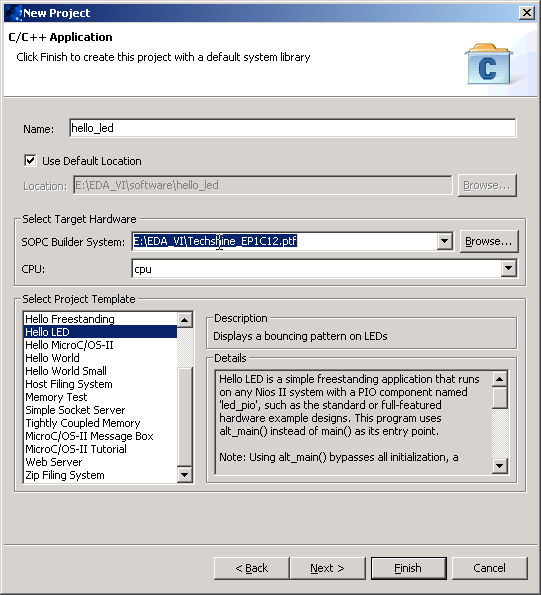

4、在弹出的新建工程向导中,选择第一项C/C++ Application。点Next,下一步操作。

5、在弹出的C/C++ Application工程向导中,在窗口左下的工程模板中选择Hello_LED,默认的工程名为hello_led_0,将工程名改为hello_led,目标硬件选择中浏览找到,Quartus II工程中的Techshine_EP1C12.ptf文件。点Next,下一步操作。

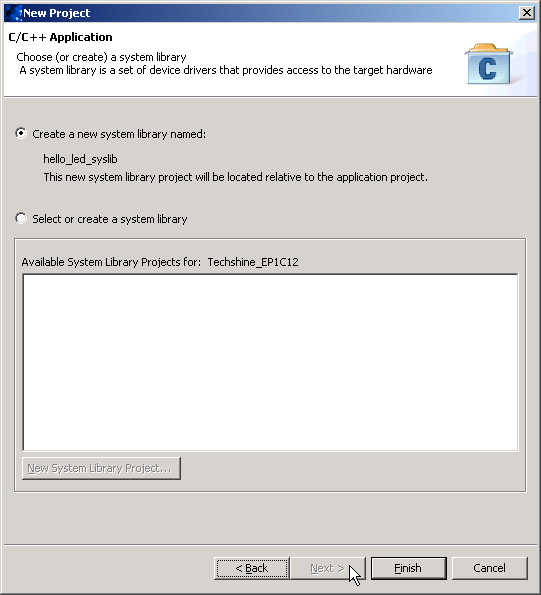

6、在弹出的系统库设置中,按默认选第一项Create a new system library named,新建系统库。点Finish,完成系统库创建。

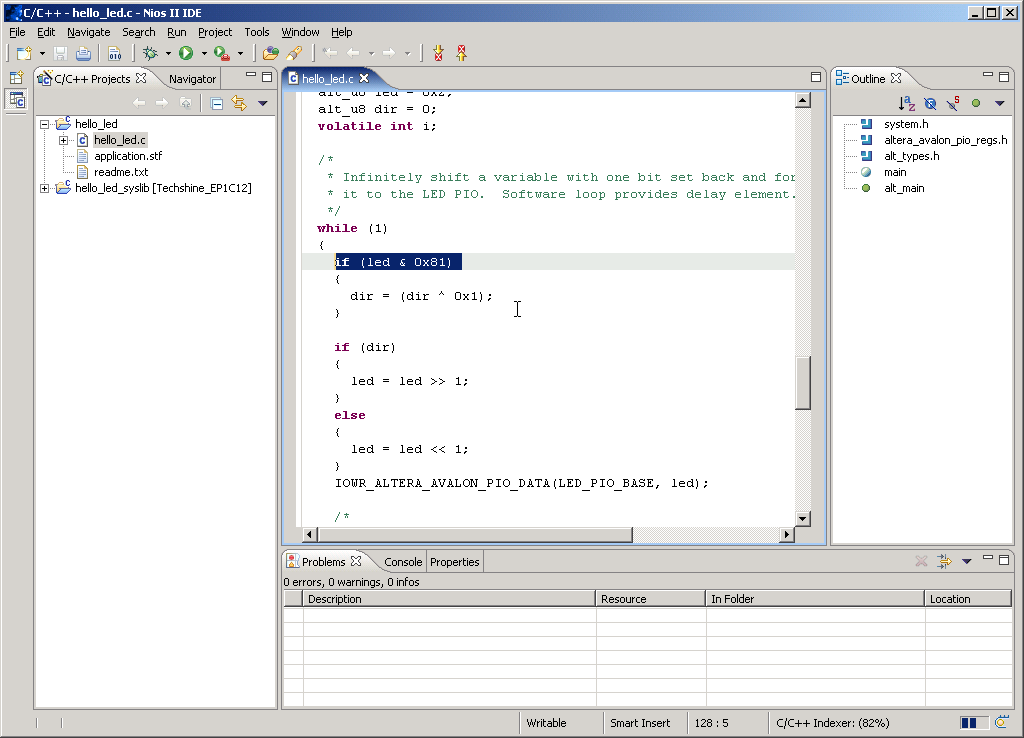

7、如果创建工程成功,则弹出如下窗口。打开hello_led.c文件,将其中“if (led & 0x81)”行程序改为“if(led & 0x09)”,0x09对应为4位LED跑马灯,0x81对应为8位。

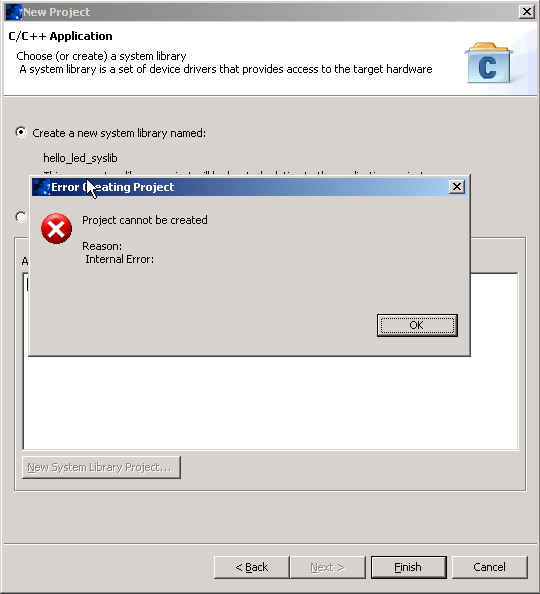

8、如果在第6步后,没有出现第7步窗口,而是弹出如下的创建失败窗口,请选OK,关闭出错窗口,再在底层窗口中点Cancel,取消创建。(这类出错属于IDE的设计漏洞)

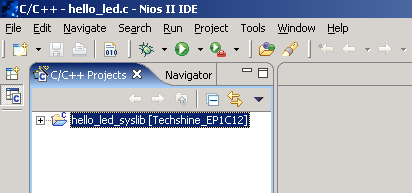

9、虽然创建NIOS II 应用工程失败,但可以在IDE左边的工程管理窗口中看到,hello_led_syslib的工程系统库已经生成。

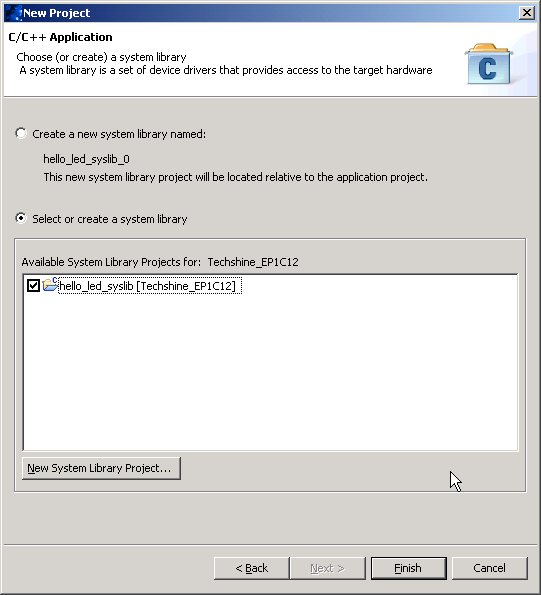

10、重复第步骤3到5,完成后,弹出如下窗口,选择第二项Select or create a system library,将下面的hello_led_syslib系统库前打勾,按Finish,进行步骤7操作。

11、编译应用工程及系统库。在工程管理窗口中选中hello_led应用工程,鼠标右键点击在弹出菜单中选择Builder Project,NIOS II IDE将自动先编译系统库hello_led_syslib,完成后自动编译应用工程hello_led。

12、下载配置文件。在NIOS II IDE主菜单中选择ToolsàQuartus II Programmer,打开Quartus II Programmer窗口。(或通过开始菜单打开Quartus II Programmer)

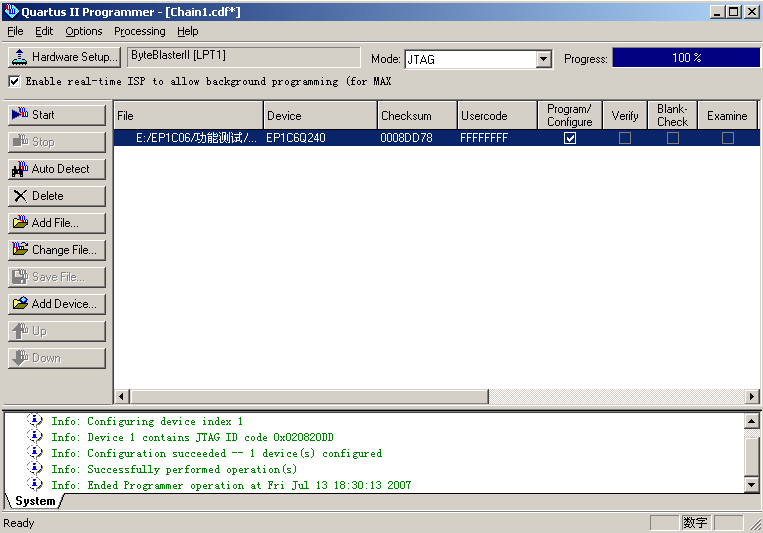

13、默认为JTAG下载方式,点”Add File…”按钮,流览添加Quartus II工程目录下的 “E_Play.sof”文件,在相应的“Programmer/Configure”项上打勾,点“Start”下载程序。在下载配置文件前,先将ByteBlaster II下载线插到JTAG方式下载口,并给目标板接通电源。

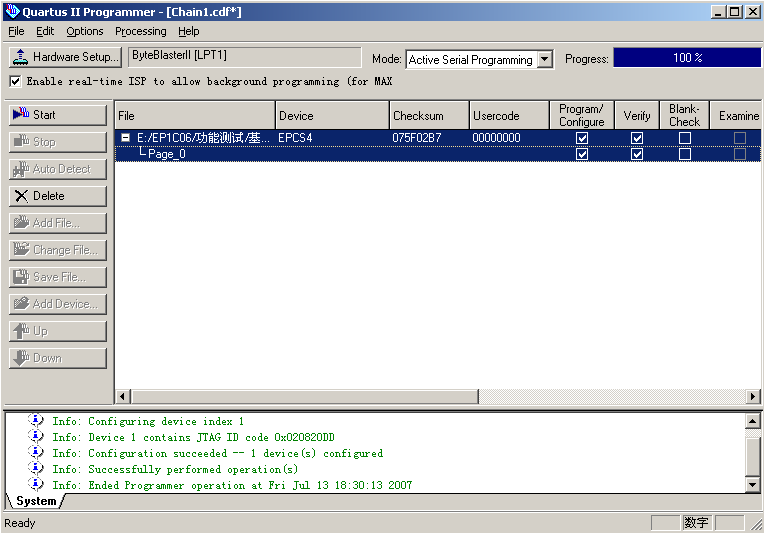

14、如果用AS方式下载,请先在“Mode”模式下拉列表里,选择“Active Serial Programmer”,然后流览添加相应的“.pof”文件,在相应的“Programmer/Configure”项和“Verify”项上打上打勾,点“Start”下载程序。(下载线插到AS方式下载口)

15、如果Hardware选项中显示“No Hardware”, 点击“Hardware setup”按钮进行下载线设置。在 hardware Setup 对话框“ Hardware Settings”设置页上点击“Add Hardware”按钮。在 Add Hardware 对话框上选择恰当的下载线类型,点击“OK”按钮。回到 Hardware Setup 对话框,在“Available Hardware items”中,双击所需要的下载线类型,点击“Close”按钮。

16、运行NIOS II应用程序。在NIOS II IDE工程管理窗口,选中要运行的工程hello_led,鼠标右键弹出菜单中选择Run AsàNIOS II Hardware。运行成功,可以看到目标板上的四个LED灯循环点亮。

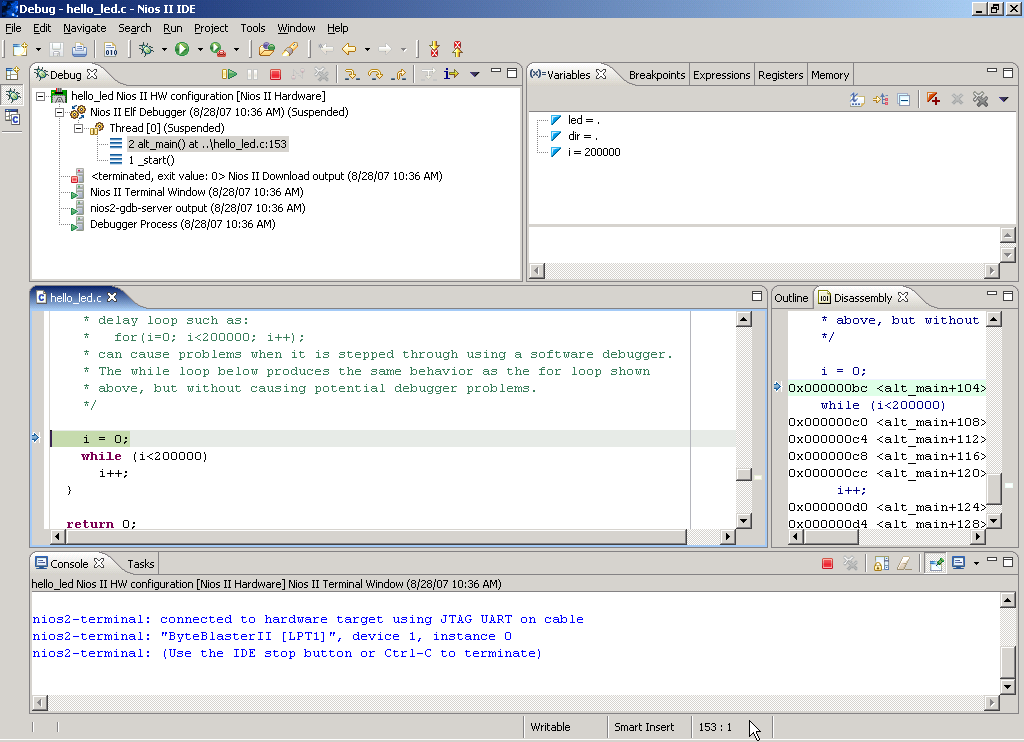

17、如果想做对应用程序做进一步调试,可以用应用工程右键菜单Debug AsàNIOS II Hardware。详细步骤请参考NIOS II IDE软件开发手册。

后记:

这是篇本科时候的自学设计,感谢太原科技大学电子科学与技术学院李斌老师的技术支持!另:由于当时的设备局限,好多时候得进行一些多余的操作,例如修改板上电压等等,本文记录了操作过程的所有主要步骤,当然,也因当时能力有限显得有些冗长。感谢各位拨冗读到这里,欢迎批评斧正~

浙公网安备 33010602011771号

浙公网安备 33010602011771号