摘要:好的,我们来详细、深入地解析 ARM 架构中的缓存一致性机制。这对于理解现代多核处理器(如手机、服务器芯片)如何高效协同工作至关重要。 ARM 的缓存一致性解决方案是其架构的一大特色,它主要通过 “总线监听” 和 “一致性互联协议” 来实现,其中最核心的概念是 ACE 和 CHI。 核心机制:基于监

阅读全文

摘要:好的,我们来详细说明 ARM 架构中的“系统内存映射”(System Memory Map)。 这是一个非常核心的概念,它定义了处理器内核如何看待其整个地址空间,即地址总线上的每个地址对应的是什么物理设备或内存类型。 一、核心概念:什么是系统内存映射? 简单来说,系统内存映射是一张“地址分配表”。它

阅读全文

摘要:以下是 ARM 架构 的详细总结,涵盖其主要架构版本、子架构、指令集兼容性以及它们之间的关系: 一、ARM 架构演进与核心版本 ARM 架构自 1985 年推出以来,经历了多个版本迭代,每个版本引入了新的特性和指令集扩展。以下是主要版本及其关键特性: 版本 发布时间 关键特性 ARMv1 1985

阅读全文

摘要:在ARM架构的SoC设计中,总线仲裁器是共享总线系统的核心组件,负责在多个主设备(如CPU、DMA、GPU等)竞争总线资源时进行高效调度。以下是ARM系统中常用的仲裁方案及其技术特点: ⚙️ 一、轮询仲裁(Round Robin, RR) 工作原理:按固定顺序循环分配总线使用权。仲裁器维护一个主设备

阅读全文

摘要:在计算机体系结构、片上网络(NoC)及多主设备总线系统中,Fair-Among-Equals(平等者间公平仲裁) 是一种基于优先级分组的混合仲裁策略,其核心思想是:在相同优先级的设备间采用公平仲裁(如Round Robin),而不同优先级设备间仍遵循优先级规则。这一方案在保证高优先级设备实时性的同时

阅读全文

摘要:在ARM架构的总线系统中(如AHB/AXI总线),Round Robin(轮询仲裁) 是一种常用的仲裁方案,用于公平地分配多个主设备(Master)对共享总线资源的访问权限。其核心思想是循环分配总线使用权,避免单一主设备长期独占总线,从而保证系统资源的公平性和实时性。 Round Robin仲裁的核

阅读全文

摘要:1.前言 只要提到AXI总线协议,这就是一个绕不过去的话题,虽然这个话题有点老生常谈,但确实非常重要,其实很多面试官特别喜欢问这个知识点。 2. AXI总线上正常的Burst传输 AXI总线的Transaction是Burst-based的,下图是一个正常的Burst传输示意图。 正常情况下的主机M

阅读全文

摘要:1. AHB Lite是AHB协议的简化版本。AHB Lite本质上意味着只有一个Master。这反过来也意味着: 1.1.无仲裁; 1.2.无HBUSREQ信号,无HGRANT信号; 1.4.无拆分或重试响应类型->HRESP只能是1位; 1.5.不得提前终止总线。 2. 如何将完整的AHB主设备

阅读全文

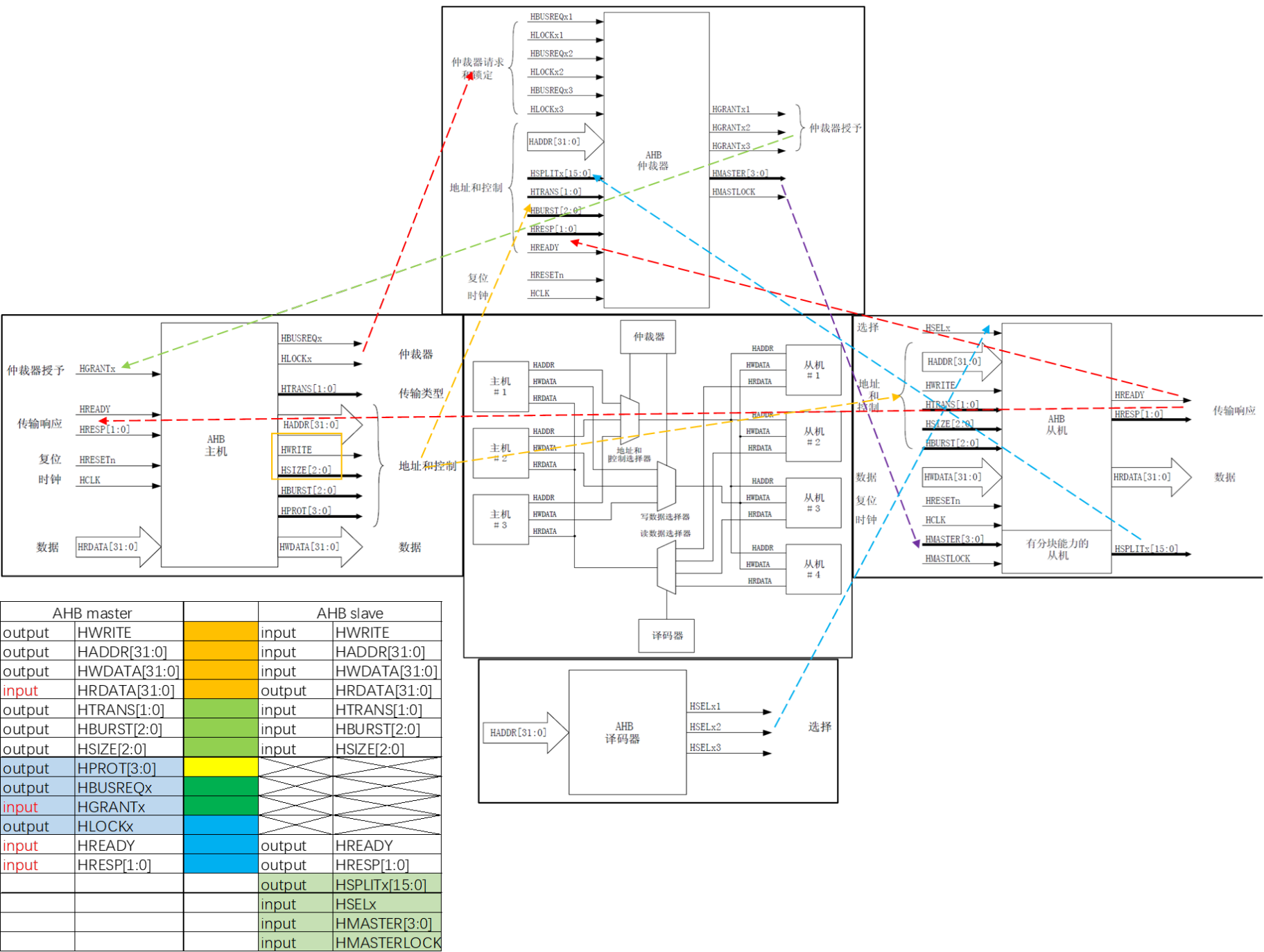

摘要:1.前言 AHB是Advanced High-performance Bus的简称,AHB是 AMBA(Advanced MicrocontrollerBus Architecture高级微控制器总线架构)总线的一部分,AMBA总线最初是ARM公司提出的,如今被市面上大多数SoC芯片所采用。典型的应

阅读全文

摘要:AHB总线有两个阶段:地址阶段和数据阶段。 HREADY是来自每个Slave的输出信号,它被路由到每个Master和每个Slave。这意味着每个Slave将具有2个HREADY信号:HREADY_in和HREADY_out。即HREADY信号既是Slave的输入和同时又是Slave的输出。 AHB

阅读全文

摘要:1.前言 相信很多朋友对AMBA都比较熟悉了,对AHB总线也不陌生,在AHB总线中,hready这个信号是最难理解,最容易搞错,也是系统调试的过程中出问题最多的地方之一,同时也是很多面试官最喜欢问的知识点之一。本文做一个梳理,帮助大家彻底理解这个知识点。 2.理解一下hready和hready_ou

阅读全文

摘要:ahb1结构图  ahb5结构图 |AXI4(13/44)|Description| | | | | |AWID[user]|AWID[user]|| |AWADDR|AWADDR|| |AWLEN[3:0]|AWLEN[7:0]|Note: incr3: 1-16, incr4: 1-256

阅读全文

摘要:A4第A4章 事务属性 本章描述了决定一个事务应该如何被系统组件,如缓存、缓冲区和内存控制器处理的属性。它包括以下部分: 在A4-62页的事务类型和属性 在A4-63页的AXI3内存属性信号 在A4-64页的对AXI4内存属性信号的更改 在A4-69页的内存类型 在A4-73页的内存不匹配属性 在A

阅读全文

摘要:第A3章 接口要求 本章描述了单个master和slave之间的基本AXI协议事务需求。它包含以下部分: 在A3-40页设置时钟和复位 第A3-41页上的基本读写事务 在A3-44页的通道之间的关系 第A3-48页的事务结构 A3.1 时钟和复位 这部分描述AXI全局时钟ACLK和复位信号ARESE

阅读全文

摘要:第A2章 信号描述 本章介绍AXI接口信号。协议的AXI3和AXI4实现需要大多数信号,总结信号的表标识了例外情况。本章包括以下几个部分: 全局信号在A2-32页 在A2-33页上写地址通道信号 在A2-34页写数据通道信号 在A2-35页上写响应通道信号 在A2-36页上的读地址通道 在A2-37

阅读全文

摘要:第A1章 概述 本章介绍了AXI协议的体系结构和本规范中使用的术语: 关于A1-26页的AXI协议 在A1-27页的AXI架构 第A1-30页的术语 A1.1 关于AXI协议 AMBA AXI协议支持高性能、高频的系统设计,用于主从组件之间的通信。 AXI协议的特性有: 它适用于高带宽和低延迟的设计

阅读全文

摘要:前言 本序言介绍AMBA AXI和ACE协议规范。它包含以下部分: 关于此规范,请参阅第xiv页 关于此规范的使用,请参阅xv页 约定在第xix页 额外阅读在第xxi页 反馈在第xxii页 关于这个规范 这个规范描述了AXI和ACE的AMBA协议。几个发行版本级别和变体描述如下: AMBA 3 AX

阅读全文

摘要:目录 AMBA AXI and ACE Protocol Specification 前言 关于这个规范 ...................................................................................... xiv 使用这个规范

阅读全文

摘要:附录D 实例波形 本附录提供了一些从一些示例流量通道中生成的波形。这些波形可用于验证流量通道生成器的实现是否与本规范中预期的周期行为相匹配。 所给出的每个示例旨在说明流量配置通道行为的一个或两个特定方面。 本节中的所有示例都基于128位的数据总线,这意味着DataSize为16B。 D.1 FIFO

阅读全文