verilog中==/!=和===/!==的区别

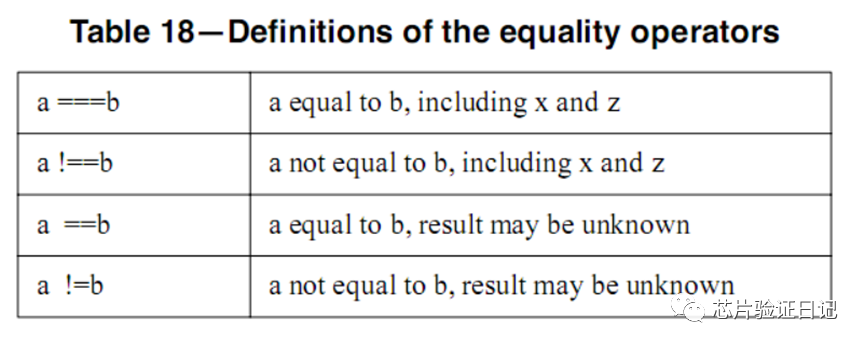

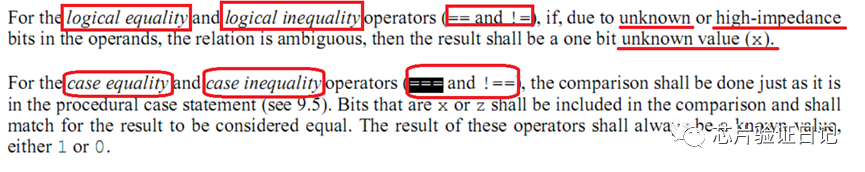

下面两幅截图来自《Verilog_IEEE1364_2001》:

翻译一下上面截图中的IEEE的说明:

对于逻辑相等(logical equality “”)和逻辑不等(logical inequality “!=”)运算符,如果操作数中出现x态位或z态位(高阻),那么比较结果将会是1位的x值。

对于case相等(case equality “=”)和case不等(case inequality “!=”)运算符,不管操作数中有没有x态位或z态(高阻)位,比较结果都会是1位确定的值,要么是1要么是0。

换一种好理解的说法:

和!=称为逻辑等式/不等式运算符,其结果由两个操作数的值决定。当操作数中某些值是不定值x和高阻值z时,比对的结果都是X(不定值),这也好理解,因为从逻辑上无法判断这两个操作数是否相等。

而=和!运算符则不同,它在对操作数进行比较时,对某些位的不定值x和高阻值z也进行比较,两个操作数必须完全一致,其结果才是1,否则为0。

=和!运算符常用于case表达式(或者if表达式)判别,所以又称为case等式/不等式运算符。

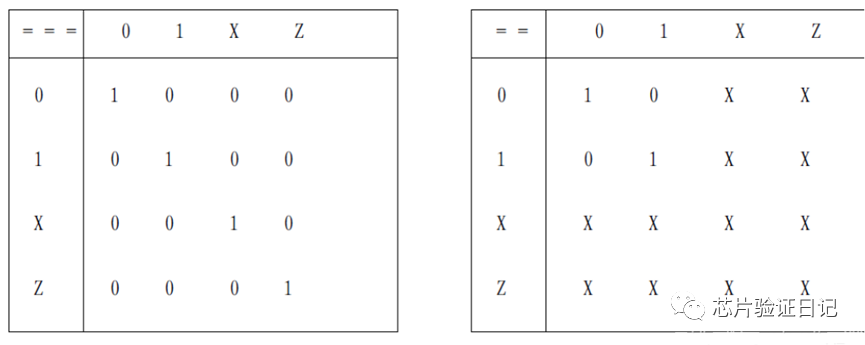

下面的截图就是二者的真值表(True Table),大家看一下就一目了然了。

注意在if语句中的条件判断时,如果用逻辑等式来判断x态,结果是不执行的,例如:

if (a == 1'bx)

$display("test =="); //不管a的值是什么,a == 1'bx的结果都是x态,并且不会执行display语句

if (a === 1'bx)

$display("test ==="); //如果a的值是x,a == 1'bx的结果是1,会执行display语句,打印输出

如果等式运算符中的操作数有X/Z态的,建议使用“===”和“!==”,如果不确定等式运算符的操作数是否有X/Z态,也建议使用“===”和“!==”。总之,使用“===”和“!==”是最安全的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号