硬复位、软复位和上电复位

-

软复位与硬复位

软复位信号名称中通常包含soft,硬复位信号名称中通常包含hard。

软复位:常用于复位逻辑模块。

硬复位:常用于配置寄存器模块,配置信号同步模块。

硬复位有效会驱动软复位有效。

一个模块出现问题时,可以使其软复位有效,进行逻辑复位操作,但是由于配置寄存器是由硬复位驱动的,所以不会发现改变,因此无需浪费时间重新配置。 -

复位的产生

NOTE:硬复位有效会导致软复位有效,而通过soc总线配置软复位有效时硬复位不受影响。

硬复位如何产生:芯片复位时(chip_poweron_rst_n=0)

如下图所示,复位信号_n表示低电平有效,其他信号高电平有效

chip_poweron_rst_n由芯片复位管脚驱动,此信号有效(值为0)则芯片中所有子系统软复位和硬复位都有效,即芯片重启。hard_rst_en_csr,硬复位总使能信号,sub_sys_hard_rst_cfg_csr为硬复位配置寄存器,控制着芯片中子系统的软复位和硬复位,sub_sys_hard_rst_cfg_csr[0]为子系统硬复位总开关,当sub_sys_hard_rst_cfg_csr和hard_rst_en_csr同时有效时,所有硬复位全部有效。

当sub_sys_hard_rst_cfg_csr[1]而sub_sys_hard_rst_cfg_csr[0]无效(前提,chip_poweron_rst_n和hard_rst_en_csr均为1),则仅仅ppu_hard_rst_n有效。

硬复位会驱动软复位有效,当ppu_hard_rst_n有效时,ppu_soft_rst_n同样有效。

assign ppu_hard_rst_n = chip_poweron_rst_n&(~(hard_rst_en_csr&(sub_sys_hard_rst_cfg_csr[0]|sub_sys_hard_rst_cfg_csr[1])));

assign hbm_hard_rst_n = chip_poweron_rst_n&(~(hard_rst_en_csr&(sub_sys_hard_rst_cfg_csr[0]|sub_sys_hard_rst_cfg_csr[2])));

assign cfg_hard_rst_n = chip_poweron_rst_n&(~(hard_rst_en_csr&(sub_sys_hard_rst_cfg_csr[0]|sub_sys_hard_rst_cfg_csr[3])));

assign se_hard_rst_n = chip_poweron_rst_n&(~(hard_rst_en_csr&(sub_sys_hard_rst_cfg_csr[0]|sub_sys_hard_rst_cfg_csr[4])));

assign ppu_soft_rst_n = ppu_hard_rst_n&(~(soft_rst_en_csr&(sub_sys_soft_rst_cfg_csr[0]|sub_sys_soft_rst_cfg_csr[1])));

assign hbm_soft_rst_n = hbm_hard_rst_n&(~(soft_rst_en_csr&(sub_sys_soft_rst_cfg_csr[0]|sub_sys_soft_rst_cfg_csr[2])));

assign cfg_soft_rst_n = cfg_hard_rst_n&(~(soft_rst_en_csr&(sub_sys_soft_rst_cfg_csr[0]|sub_sys_soft_rst_cfg_csr[3])));

assign se_soft_rst_n = se_hard_rst_n &(~(soft_rst_en_csr&(sub_sys_soft_rst_cfg_csr[0]|sub_sys_soft_rst_cfg_csr[4])));

-

中断模块用什么软复位OR硬复位?

中断用于记录逻辑电路中发生的各类正常和异常情况。软复位控制主数据路径逻辑,硬复位控制配置寄存器等。

正常情况:如发生一次DMA数据传输,链表初始化完成

异常情况:如RAM读写数据错误,afifo溢出和空读,链路中断等

那么中断模块适合用软复位还是硬复位呢?

通常情况下,大部分中断源是由逻辑电路产生的情况下,逻辑电路有软复位直接控制,此时中断模块用软复位,记录此次软复位释放后电路中发生的各类状态,一旦发生软复位,中断状态会被软复位清零。

如果中断使用的硬复位,多次软复位的情况下,无法区别记录的是哪一次的软复位释放后的状态,只能每次软复位一次,软件读清零中断。

在特殊的设计中,如果模块会存在自动复位的情况,此时需要中断记录曾经发生过的自复位,那么此时中断需要使用硬复位。 -

IC设计数据流复位顺序、解复位顺序?

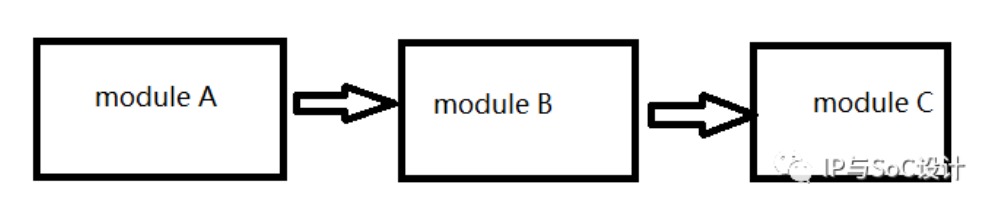

如图所示:模块A、B、C为芯片逻辑模块,数据流从模块A流向模块B、模块C。

1、复位顺序是怎样的?

如果需要对模块A、B、C进复位操作,复位操作顺序是什么样的呢?先复位哪个模块,后复位哪个模块?

复位顺序:A--->B--->C 按数据流方向复位

先复位A模块,最后复位C模块。复位的原则是保证复位完成后,数据通路中没有不稳定状态。

如果先复位模块C,最后复位模块A,则在模块A完成复位后的短暂时间内,模块A中之前的不稳定状态会依次传递到模块B和模块C。

2、如果芯片上电完成后,模块A、B、C都处于复位状态,解复位的顺序是怎样的呢?

解复位:就是将复位信号置为无效状态,若上电后rst_n=0,解复位就是将rst_n=1。

解复位顺序:C--->B--->A 按数据流逆向解复位

先解复位模块C,最后解复位模块A,解复位后需要保证数据能够正常通路。

如果解复位顺序为A--->B--->C,在模块A解复位后,会导致A模块有数据输入而B、C无法进行数据传输,会产生一些异常状态,比如说模块A的中FIFO溢出会上报中断等,任何异常都可能会对芯片的正常运行造成影响,因此在解复位的过程中,我们需要避免一些异常情况。所以按数据流逆向解复位更加合理。

硬件复位

顾名思义通过硬件给系统一个复位,比如在电路板上设计一复位电路,通过按下按键就可以给系统实现一个复位,而无论系统在执行什么样的程序复位启动以后需要重新加载FPGA、DSP等,也有可能在这个操作之前初始化CPU,加载系统文件等操作,具体视需要而定,然后初始化一些配置芯片。硬件复位的作用区域一般是全局的。

软件复位

是通过软件给系统一个复位信号,如低电平或许是高电平(具体看系统设置)来实现复位操作。复位启动不需要进行FPGA、DSP等的加载,只是一些配置芯片的初始化。软件复位一般是一些块结构。

上电复位

系统在上电的瞬间就执行复位操作, 上电复位里面包括硬件复位和软复位的操作,硬件复位和软复位是从上电复位里面的某点开始的启动操作。复位需要初始化CPU系统,包括CPU和内存等,并加载系统,加载初始化操作系统以及FPGA、配置芯片的初始化,是一个完整的过程。

浙公网安备 33010602011771号

浙公网安备 33010602011771号