电容、电阻的应用场景

电容

电容(Capacitance)是电子学中的一个基本物理量,表示电容器存储电荷的能力。电容器由两块导体(通常是金属)和介于它们之间的绝缘材料(电介质)组成。当电容器两端施加电压时,一个导体上积累正电荷,而另一个导体上积累等量的负电荷,电介质阻止电荷直接通过,从而存储了电能。

电容在PCB设计中的常见作用

| 作用 | 描述 |

|---|---|

| 电源去耦 | 电容器用于滤除电源线上的高频噪声,为电路提供稳定的电源。 |

| 旁路电容 | 用于旁路交流信号,允许交流信号通过而阻止直流信号通过,从而隔离不同电路部分。 |

| 滤波 | 在信号处理中,电容器可以用来滤波,去除不需要的频率成分。 |

| 能量存储 | 在某些电路中,电容器用于存储和释放能量。 |

| 定时和振荡 | 电容器与电阻或晶体管一起使用,可以形成RC(电阻-电容)定时电路或振荡器。 |

电容的换算单位和公式

单位:

- 法拉(Farad, F):电容的基本单位。

- 微法(微法拉,微法,符号:μF):1微法 = 1/1,000,000法拉。

- 纳法(纳法拉,纳法,符号:nF):1纳法 = 1/1,000,000,000法拉。

- 皮法(皮法拉,皮法,符号:pF):1皮法 = 1/1,000,000,000,000法拉。

换算关系:

- 1法拉 = 1,000,000微法 = 1,000,000,000纳法 = 1,000,000,000,000皮法。

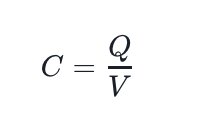

公式

其中:

- CC 是电容(法拉)。

- QQ 是存储的电荷(库仑)。

- VV 是电容器两端的电压(伏特)。

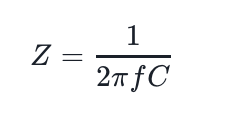

另外,对于理想的电容器,其阻抗 ZZ 与频率 ff 的关系可以表示为:

这表明电容器的阻抗随频率的升高而降低。

电容选型建议

| 频率范围/HZ | 电容取值 |

|---|---|

| DC-100K | 10uF以上的钽电容或铝电解 |

| 100K-10M | 100nF(0.1uF)陶瓷电容 |

| 10M-100M | 10nF(0.01uF)陶瓷电容解 |

| 100M以上 | 1nF(0.001uF) 陶瓷电容和PCB的地平面与电源平面的电容解 |

所以,以后不要见到什么都放0.1uF的电容,有些高速系统中这些0.1uF的电容根本就起不了作用。

为什么需要在电源附近增加滤波电容

电源中的纹波会干扰芯片的正常工作,所以需要在VCC引脚接滤波电容,空气中有手机信号,收音机信号,WIFI信号各种信号,会在电源线上产生感应电动势,干扰芯片俄正常工作,滤波电容越靠近VCC引脚越好,多个不同容量的滤波电容可以滤除不同频段的高频干扰信号,容量最小的最靠近VCC引脚。最好是πRC低通滤波器,πLC低通滤波器。

芯片附近为什么都会增加0.1微法和0.01微法的电容

回答这个问题前需要先了解一些电容的基本知识。

旁路电容和去耦电容

旁路电容(Bypass Capacitor)和去耦电容(Decoupling Capacitor)这两个概念在电路中是常见的,但是真正理解起来并不容易。要理解这两个词汇,还得回到英文语境中去。

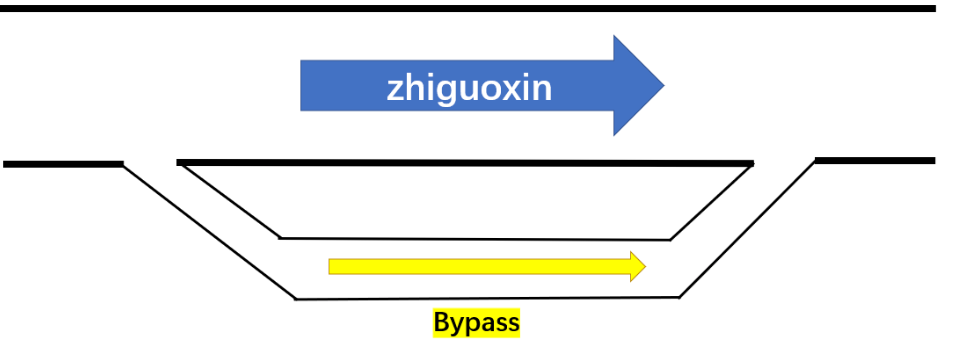

旁路电容(Bypass)

Bypass在英语中有抄小路的意思,在电路中也是这个意思,如下图所示。

去耦电容(Decoupling)

couple在英语中是一对的意思,引申为配对、耦合的意思。如果系统A中的信号引起了系统B中的信号,那么就说A与B系统出现了耦合现象(Coupling),而Decoupling就是减弱这种耦合的意思。

Couple 一对,一双。动词引申为配对,连接的意思。如果系统A中出现的事物(信号)引起了系统B中一事物(信号)的出现,或者反过来,那么我们就说系统A与系统B出现了耦合(Coupling)。Decoupling退耦即减弱这种耦合。

电路中的旁路和去耦

如下图中,直流电源Power给芯片IC供电,在电路中并入了两个电容。

旁路

旁路

如果Power受到了干扰,一般是频率比较高的干扰信号,可能使IC不能正常工作。在靠近Power处并联一个电容C1,因为电容对直流开路,对交流呈低阻态。频率较高的干扰信号通过C1回流到地,本来会经过IC的干扰信号通过电容抄近路流到了GND。这里的C1就是旁路电容的作用。

去耦

由于集成电路的工作频率一般比较高,IC启动瞬间或者切换工作频率时,会在供电导线上产生较大的电流波动,这种干扰信号直接反馈到Power会使其产生波动。在靠近IC的VCC供电端口并联一个电容C2,因为电容有储能作用,可以给IC提供瞬时电流,减弱IC电流波动干扰对Power的影响。这里的C2起到了去耦电容的作用。

为什么需要两个电容

为什么要用2个电容

回到本文最开始提到的问题,为什么要用0.1uF和0.01uF的两个电容?

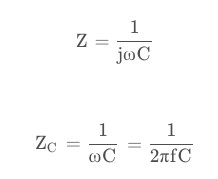

电容阻抗和容抗计算公式分别如下:

容抗与频率和电容值成反比,电容越大、频率越高则容抗越小。可以简单理解为电容越大,滤波效果越好。那么有了0.1uF的电容旁路,再加一个0.01uF的电容不是浪费吗?

实际上,对一个特定电容,当信号频率低于其自谐振频率时呈容性,当信号频率高于其自谐振频率时呈感性。当用0.1uF和0.01uF的两个电容并联时,相当于拓宽了滤波频率范围。

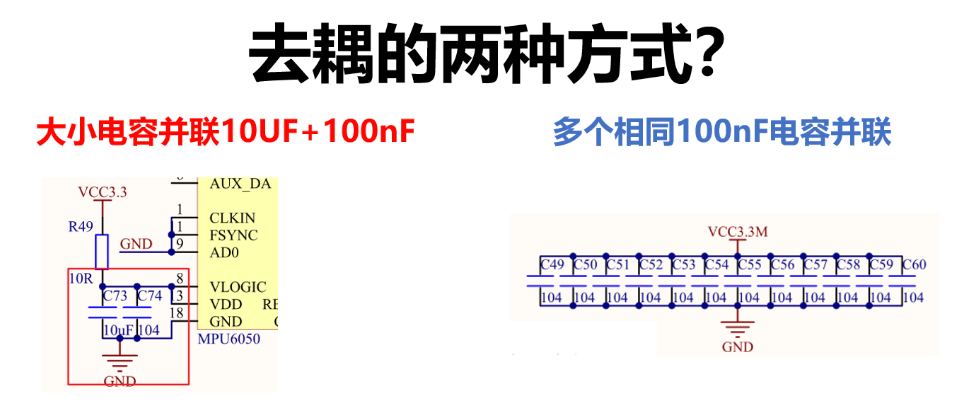

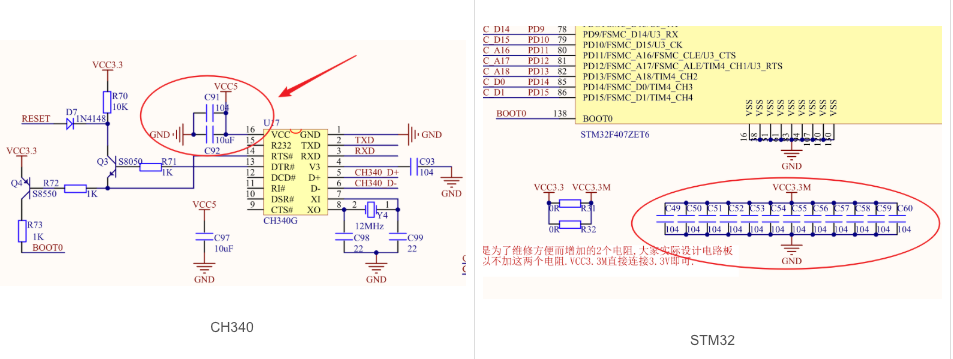

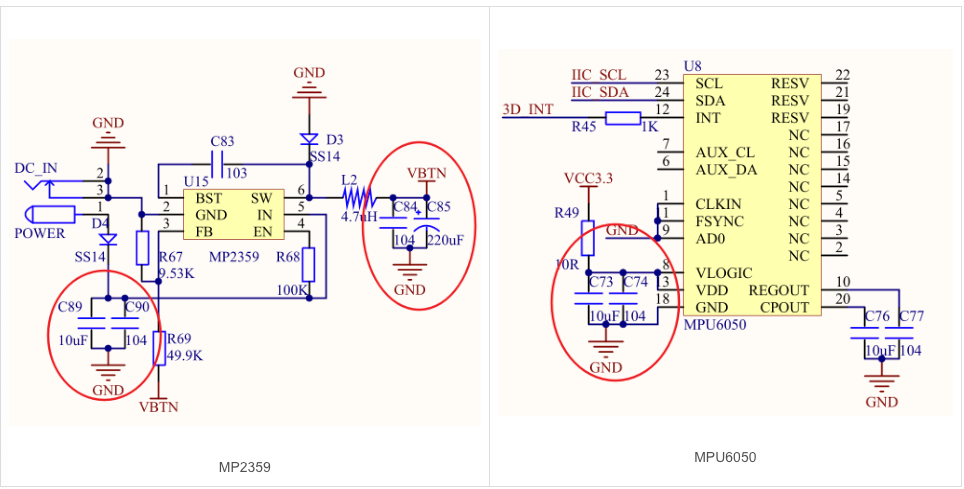

两种方式组合滤波

实际电路中我们需要去耦的频率范围会比较宽,因此呢一个电容搞不定,那怎么办呢?我们经常有两种方法来解决,一种是使用一个大电容和一个小电容并联,还有一种是使用多个相同的电容并联。那么这两种方法达到的效果分别是怎样的呢?

以下是正点原子开发板上面的一些模块芯片的电路,可供参考。

浙公网安备 33010602011771号

浙公网安备 33010602011771号