Launch off capture & launch off shift

ref link: https://www.edn.com/launch-off-shift-at-speed-test/

- LOC & LOS

2. pros & cons

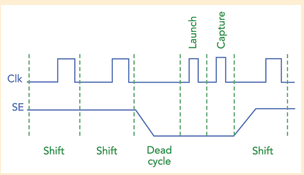

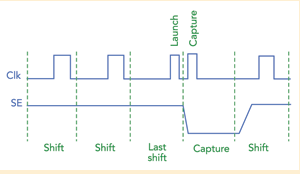

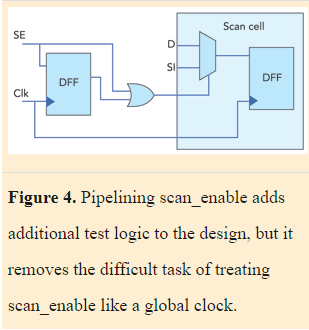

LOS更有利于工具产生pattern,因为最后一个lauch的值只需要shift到相应的scan cell,而使用LOC时,SE已经切换到capture mode,scan cell Q从D端来,因此需要耗费很多资源计算如何使D pin设为想要的值。一般来说使用LOC比LOS要低~10%的 coverage。但是实际应用中LOC是使用更广泛的技术,有两个方面的考虑。一是在最后一个shift cycle和capture cycle之间使SE变化对电路来说有难度,如果使用标准的SE架构,那么SE就必须作为一个global clock来绕线,SE一般会连接到所有的时序单元,这就给后端带来比较大的压力,一种常见的解决方法是增加pipelining logic,但是这会插入额外的电路。第二个考虑是使用LOS的时候可能会测试那些在functional mode下不工作的circuit path,这些nonfuctional logic带来的additionnal coverage可以用false path和multicyle path setting来抵销一些。

3. Synopsys Design Constraints

在design阶段,许多path被定义为false path或者multicyle path。sdc file会列出这些path从而告诉后端不用按照标准做timing closure。false path包含两种类型,一种是在functional mode下不会被sensitized,但是可能在scan mode下工作;另一种是designer不想要工作在system frequencies的path。muticycle path是需要大于一个functional clock cycle来propagate的path。ATPG tool可以直接读取sdc并提取timing-excetion path的信息,当一个信号通过这些path propagate, capture scan cell 会 capture X。SDC降低了ATPG over-testing的风险。

4. conclusion

结合pipelined SE和SDC, LOS可以达到与LOC相当的coverage,还可以有效降低pattern count和pattern generation time。

5. 其他技术

timing-aware ATPG:测试低延迟defect

Burst ATPG: 在lauch cycle前插入at-speed shifts。 It lessens the drooping of the voltage supply caused by the sudden pulsing of at-speed clocks for launch and capture during normal transition tests.

浙公网安备 33010602011771号

浙公网安备 33010602011771号