20145202 《信息安全系统设计基础》第6周学习总结(2)

教学内容总结

4.1 Y86指令集体系结构:

- 一个处理器支持的指令和指令字节级编码称为他的指令集体系结构。

- Y86的寄存器类似IA32,有8个程序寄存器:%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp。

- 存储器从概念上来说是一个很大的字节数组,保存着程序和数据。

- 程序部分最后一个部分时状态吗stat,表明程序总体执行状态。

- IA32的movl指令分成饿了4个不同的指令。

irmovl:源立即数,目的寄存器。

rrmovl:源寄存器,目的寄存器。

mrmovl:源存储器,目的寄存器。

rmmovl:源寄存器,目的存储器。

- 4个整数操作指令:addl,subl,andl,xorl。

- 7个跳转指令:jmp,jle,jl,je,jne,jge,jg。

- call指令将返回地址入栈,然后跳转到目的地址。

- pushl和popl和IA32中一样。

- halt指令停止指令的执行。

- 处理器使用pc相对寻址方式,分支指令的编码会更加简洁。

指令集的一个特点就是字节编码必须有唯一的解释。

- stat:1,aok:正常操作。

2,hlt:处理器执行halt指令。

3,adr:遇到非法地址

4,ins:遇到非法指令。

- 大多数y86指令是一种以直接的方式修改程序状态的。

4.2 逻辑设计和硬件控制语言HCL

- 逻辑门只对单个位的数进行操作。

- 很多逻辑门组合成一个网,就能够见计算块。成为组合电路。

- 多个逻辑门的输出不能同时作为另一个逻辑门的输入。

- 逻辑门必须是无环的也就是说他不能进入死循环。

- C的逻辑表达式允许参数时任意的整数,0便是错误,其他任何值都表示正确。而且逻辑门只对0和1进行操作。

- 执行子级的组合电路根据输入字的各个位,用逻辑门来计算输出字的各个位。

- HCL中,我们将所有子级的信号豆生命int,不指定字的大小。

- 允许不互斥的选择表达式使得HCL代码的可读性更好。

- 选择达式可以使任意的布尔表达式可以有任意多的情况。

- 组合逻辑电路可以设计成再子级数据上执行许多不同类型的操作。

- 时钟寄存器:存储单个的位或者字,时钟信号控制寄存器加载输入值。

- 随机访问存储器:存储多个字,用地址来选择该读哪个字或者该写哪个字。

- 向寄存器文件写入时由时钟信号控制的,控制方式类似于将值加载到时钟寄存器。

4.3 Y86顺序实现

- 六个阶段:

取址:从存储器读取指令字节地址为程序计数器的值。

译码:从寄存器文件读入最多两个操作数,得到值为valA或valB。

执行:算术逻辑单元执行指令执行的操作。

访存:将数据写入存储器,或者从存储器读出数据,读出的值为valM。

写会:最多可以写回两个结果到寄存器文件。

更新PC:将pc设置成下一个指令的地址。

- seq的实现包括组合逻辑和两种存储设备:始终存储器和随机访问存储器。

- 出其里从来不需要为了完成一条指令的执行而去读取由该指令更新了的状态。

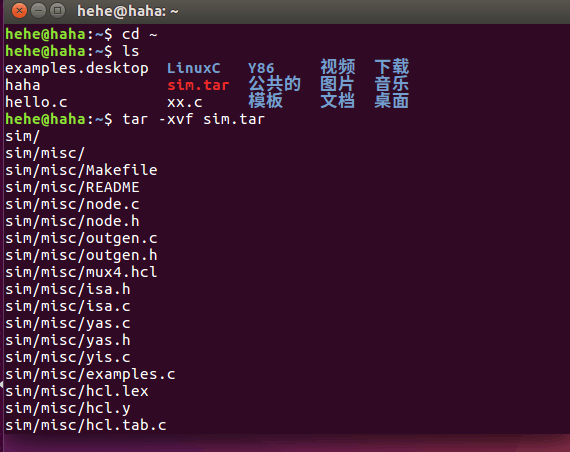

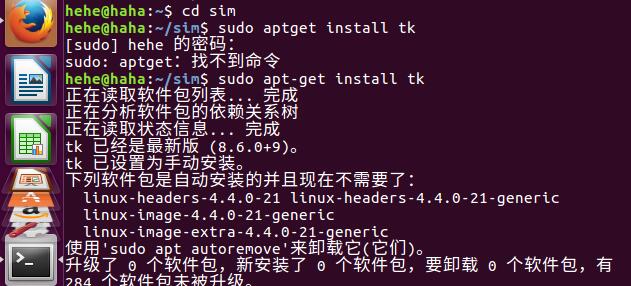

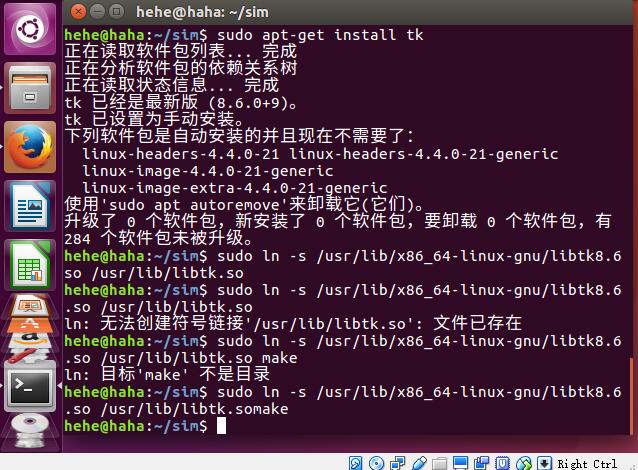

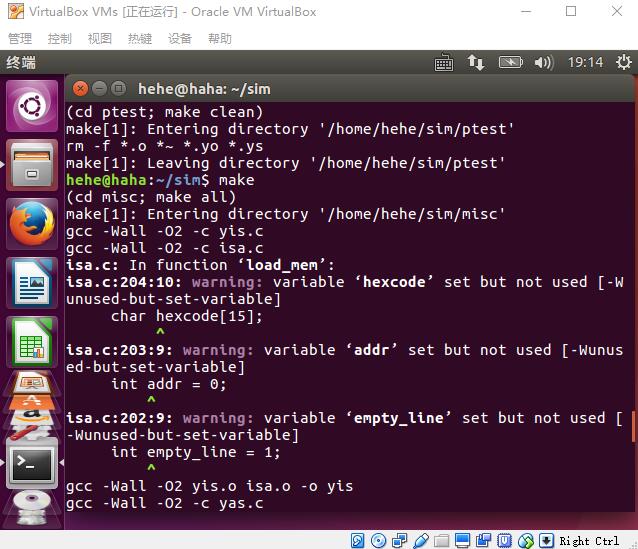

实验楼中的学习

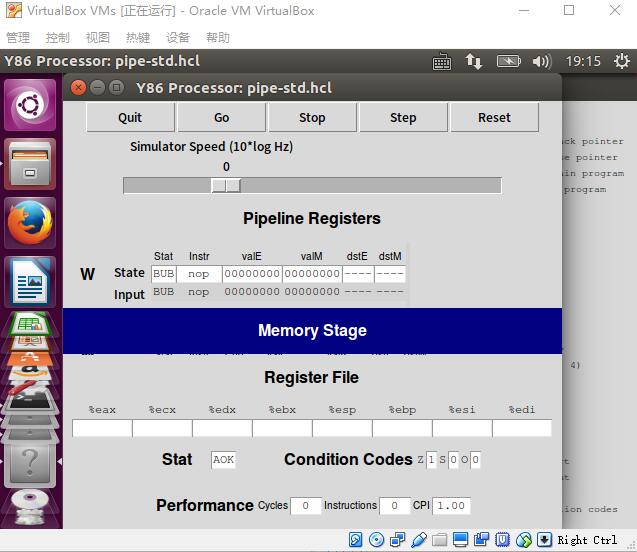

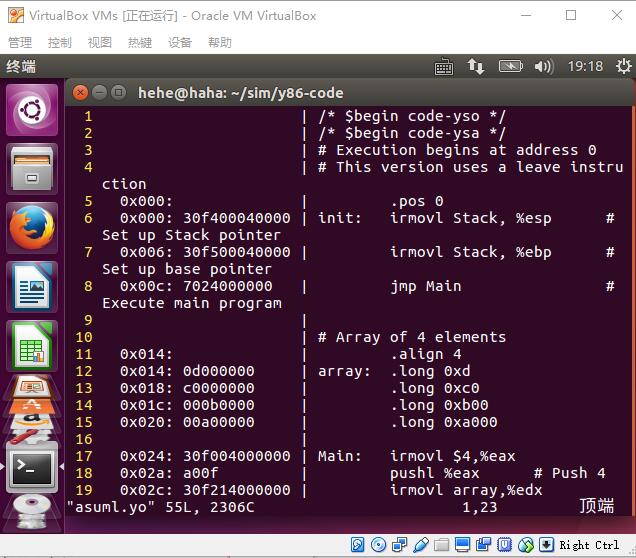

![]()

![]()

![]()

![]()

![]()

![]()

![]()

代码托管

http://git.oschina.net/tuolemi/haha

浙公网安备 33010602011771号

浙公网安备 33010602011771号