Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core。通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core的源码,这也是Xilinx为了保护作者知识产权,对IP Core进行加密。对我们开发者而言,我们也可以自定义封装自己的IP Core,需要用的这部分功能的时候,只需要直接添加IP Core进来就行了,来一起搭起你的数字积木吧!

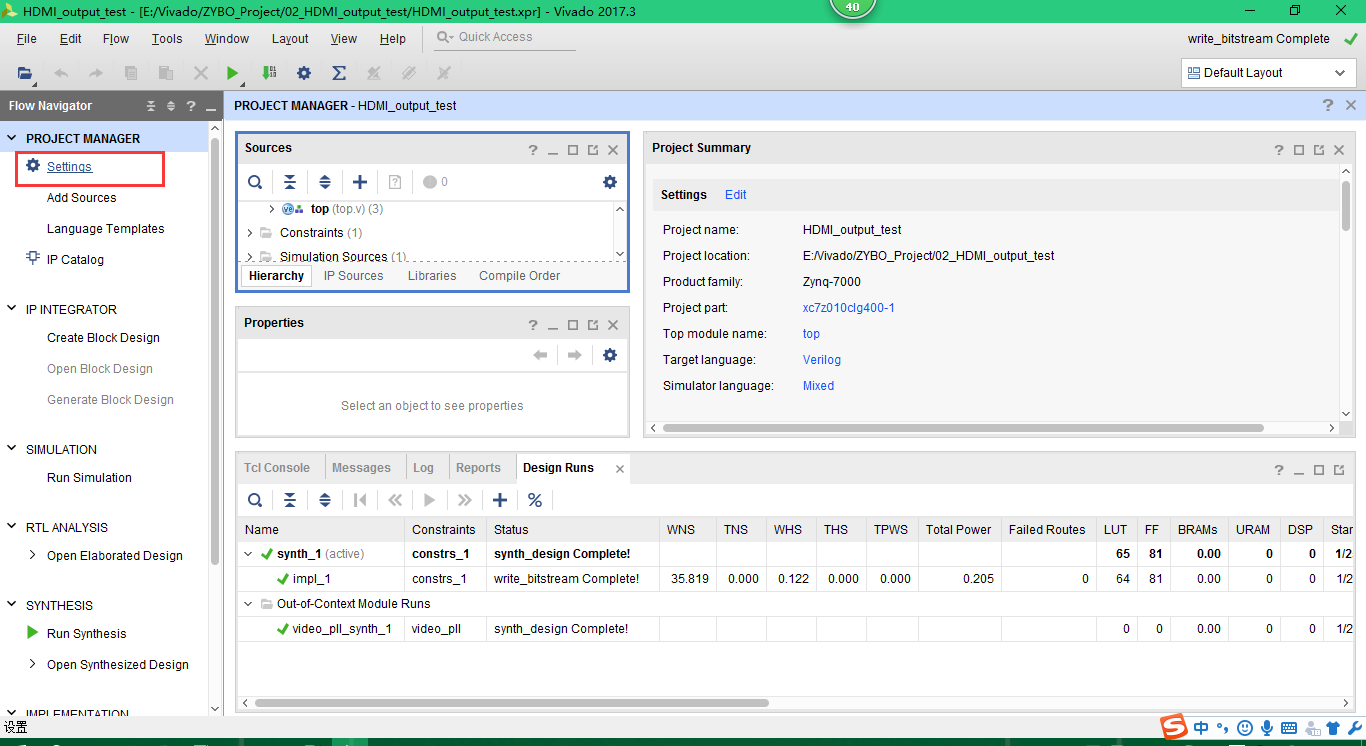

将你要封装的代码建立成一个工程,然后点击如图所示setting。

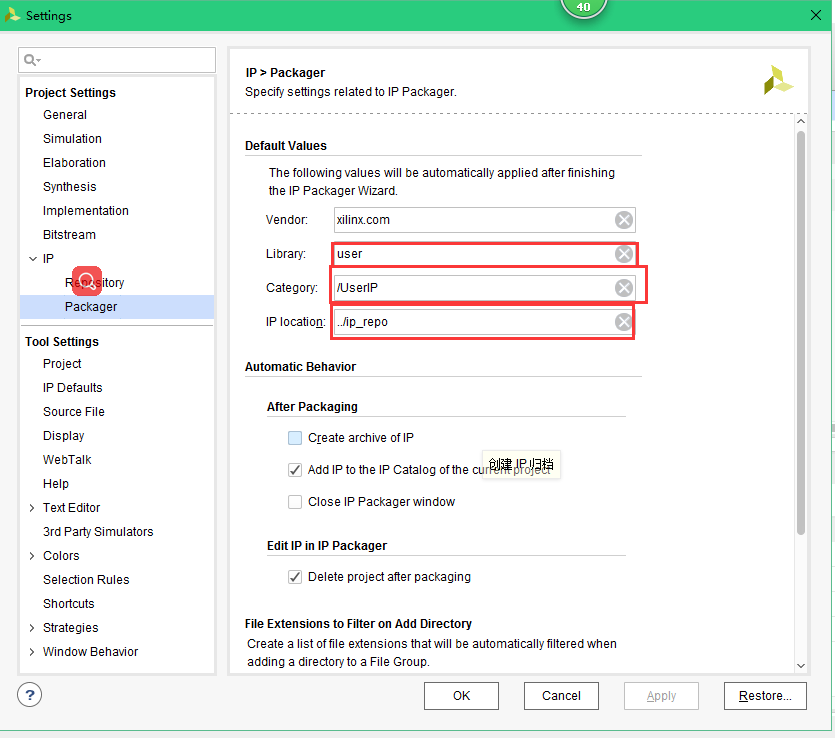

点击IP——Package,图中所标注的都是可以编辑的,这里可以自定义库名等,默认也可。

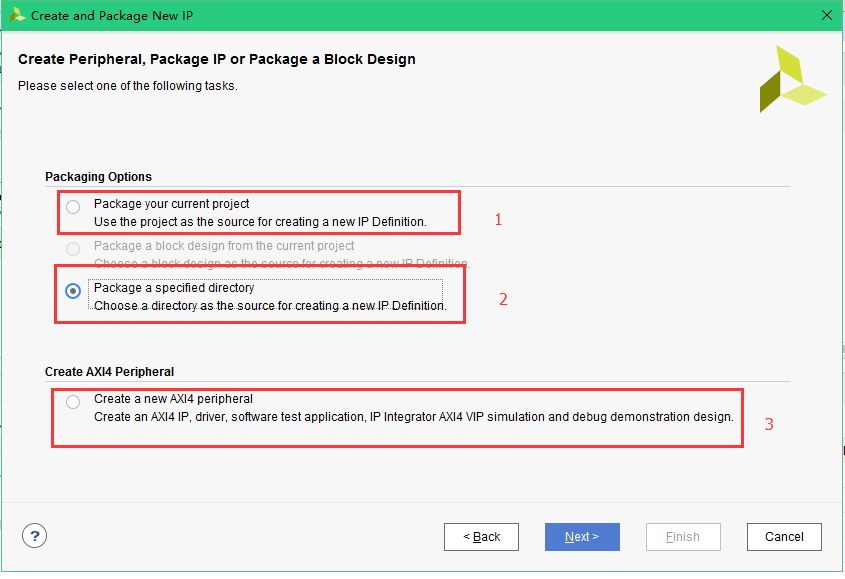

设置完成后,回到主界面,在主菜单上方点击tools——Create and Package New IP

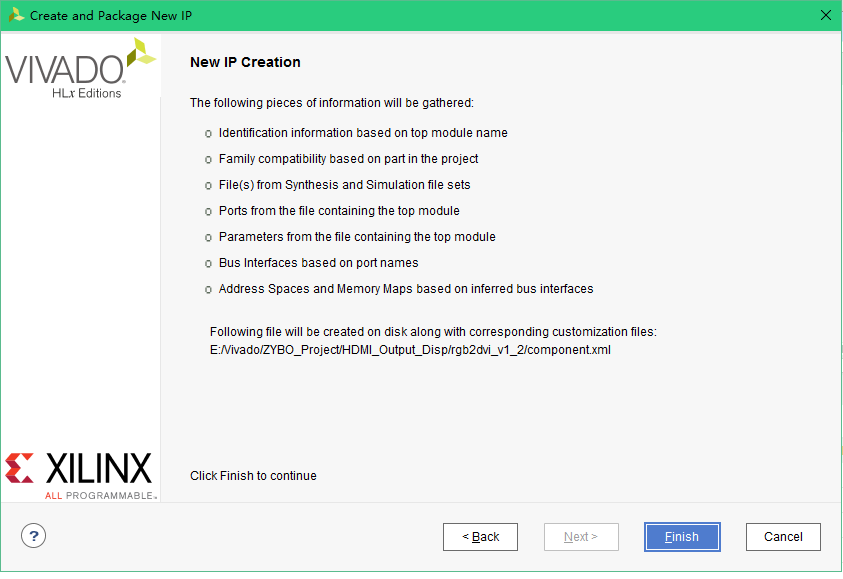

根据提示一步步走下去。

第一个是将当前工程创建成IP

第二个是将指定目录下的工程创建成IP

第三个是封装成SOC部分的IP

这里因为我选择的是第二个,因为的我是封装其他工程中的代码,一般情况下选择第一个。按照流程走就可以了。

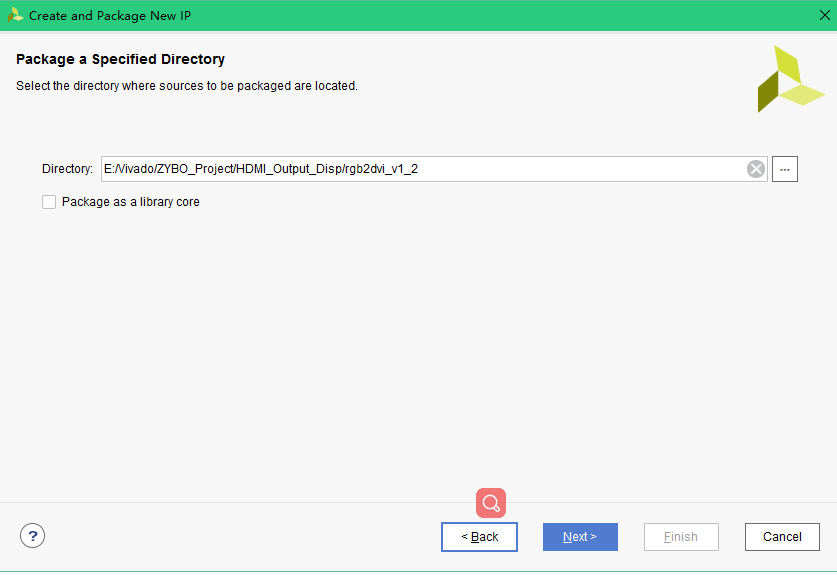

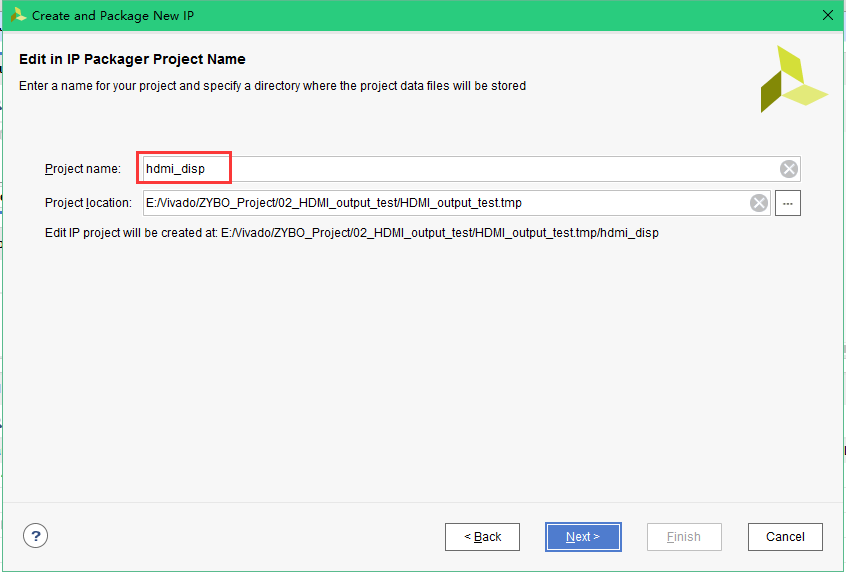

设置路径,工程名,

最后点击finish,创建工程。

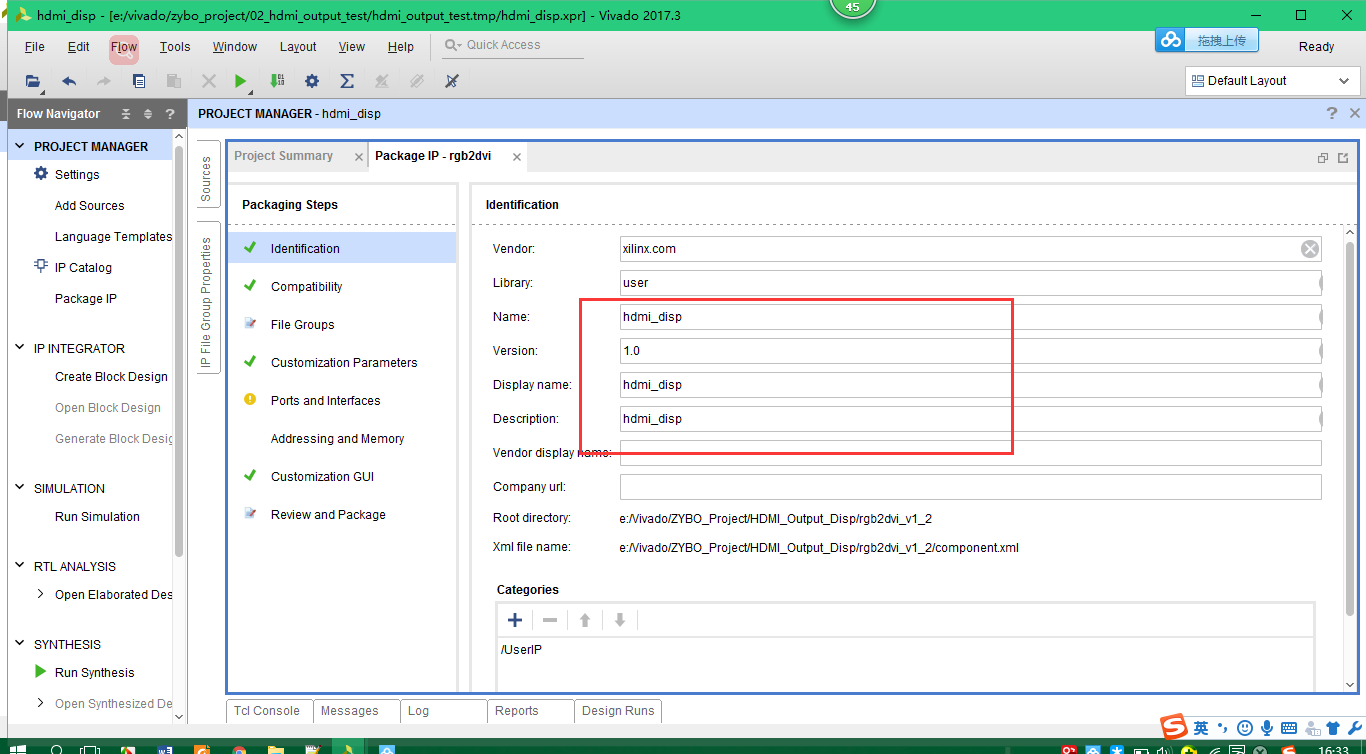

在工程主界面,点击Identification中可以设计IP Core名称和版本描述。

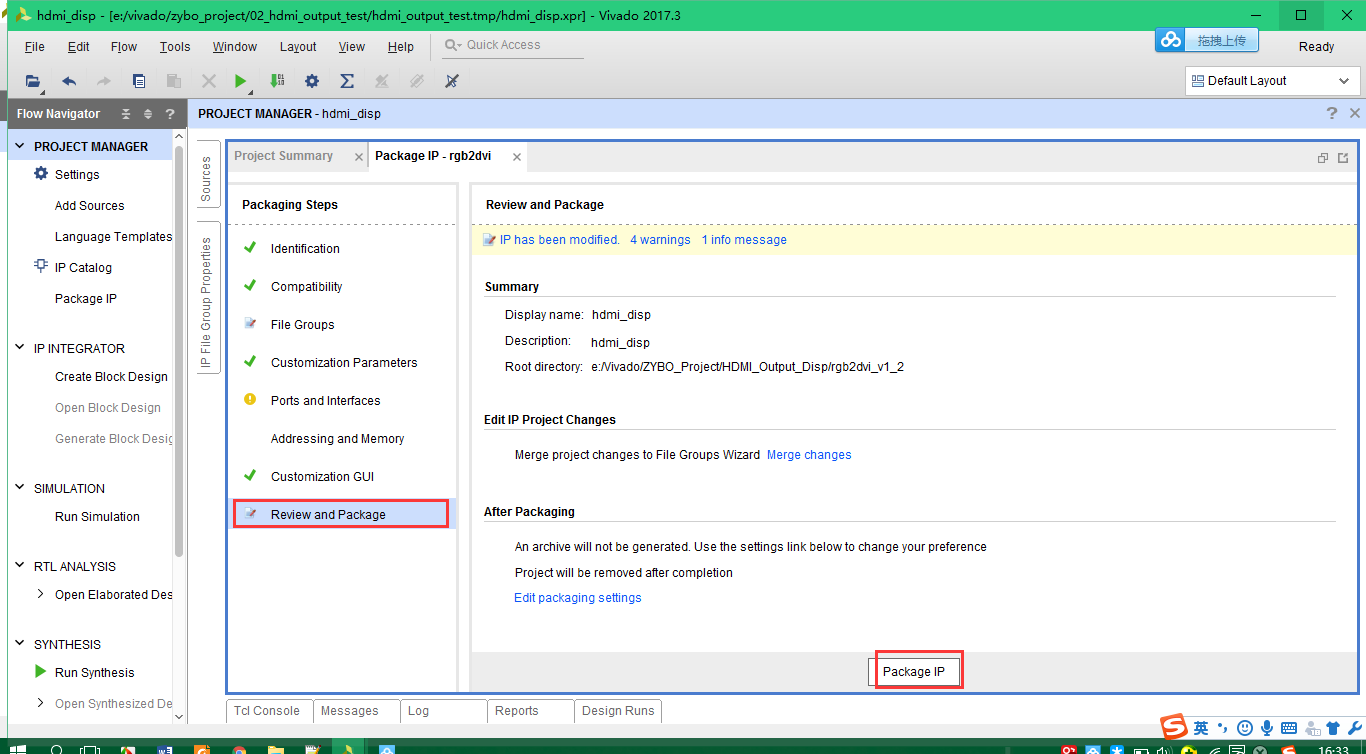

这里直接跳到最后一步,点击Package IP,然后就封装成功了。

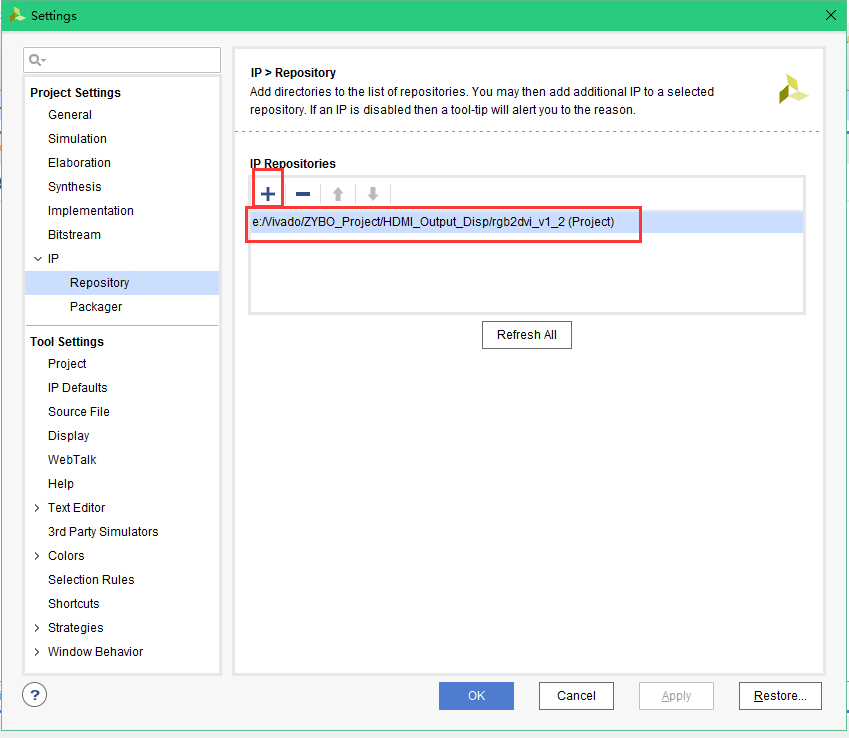

需要你封装的IP时,主界面setting——IP——Repository中添加你封装好的文件夹路径。

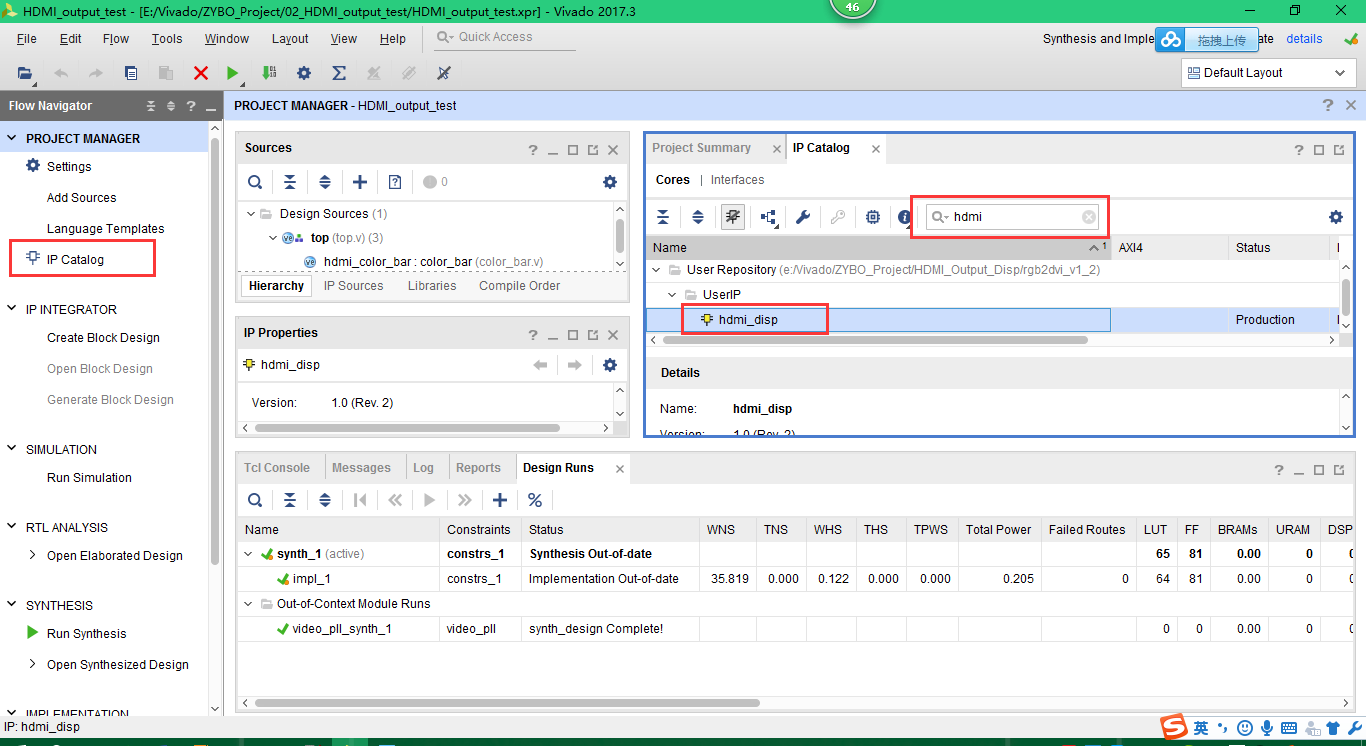

添加完成后,点击IP Catalog,搜索你的IP Core,双击就可以直接调用了。

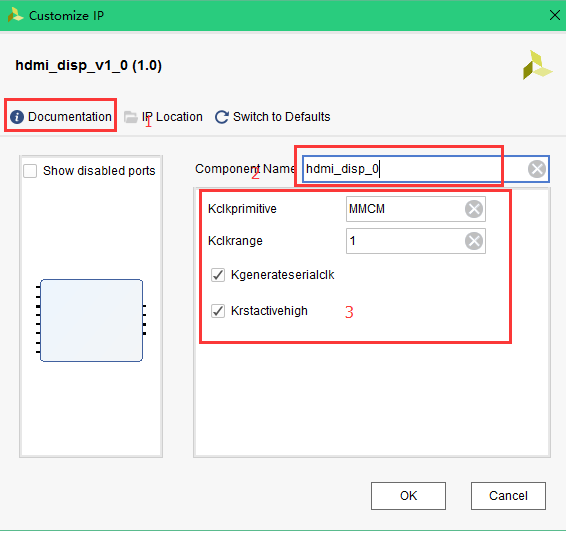

接下来的流程就和调用其他IP时候使用的相似的。我这里封装的是一个HDMI的代码,因为代码比较多,而且使用VHDL语言写的,但是在Verilog HDL的工程中也可以调用,所以为了便捷,把它封装成一个IP Core。

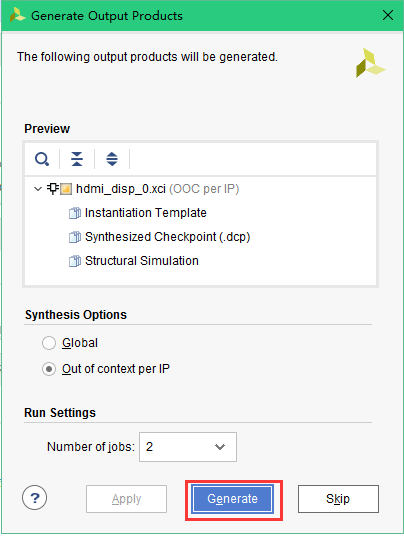

点击Generate就生成,可以直接使用了。

最后欢迎关注一亿人都想要关注的微信订阅号【开源FPGA】,总结、记录自己的学习过程,一个FPGA工程师的养成之路。欢迎加入开源FPGA-交流群-I进行讨论,群号码:677163633。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

浙公网安备 33010602011771号

浙公网安备 33010602011771号