VIVADO FIR滤波器设计与仿真(一)

VIVADO FIR滤波器设计与仿真(一)

最近在学习FPGA DSP相关设计,从滤波器开始学习,最开始先生成两个正弦信号,产生混频信号,通过modelsim仿真来验证设计。

本案例用Block Design方法进行设计(也可以选择编写.v文件的形式进行设计)。

信号源产生

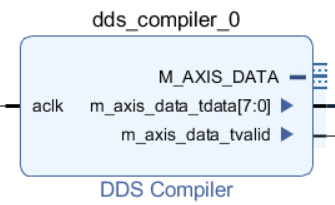

本次案例用DDS IP核产生两个简单的正弦信号,为了方便后面观察,这里分别产生一个4M和一个5M的正弦信号。

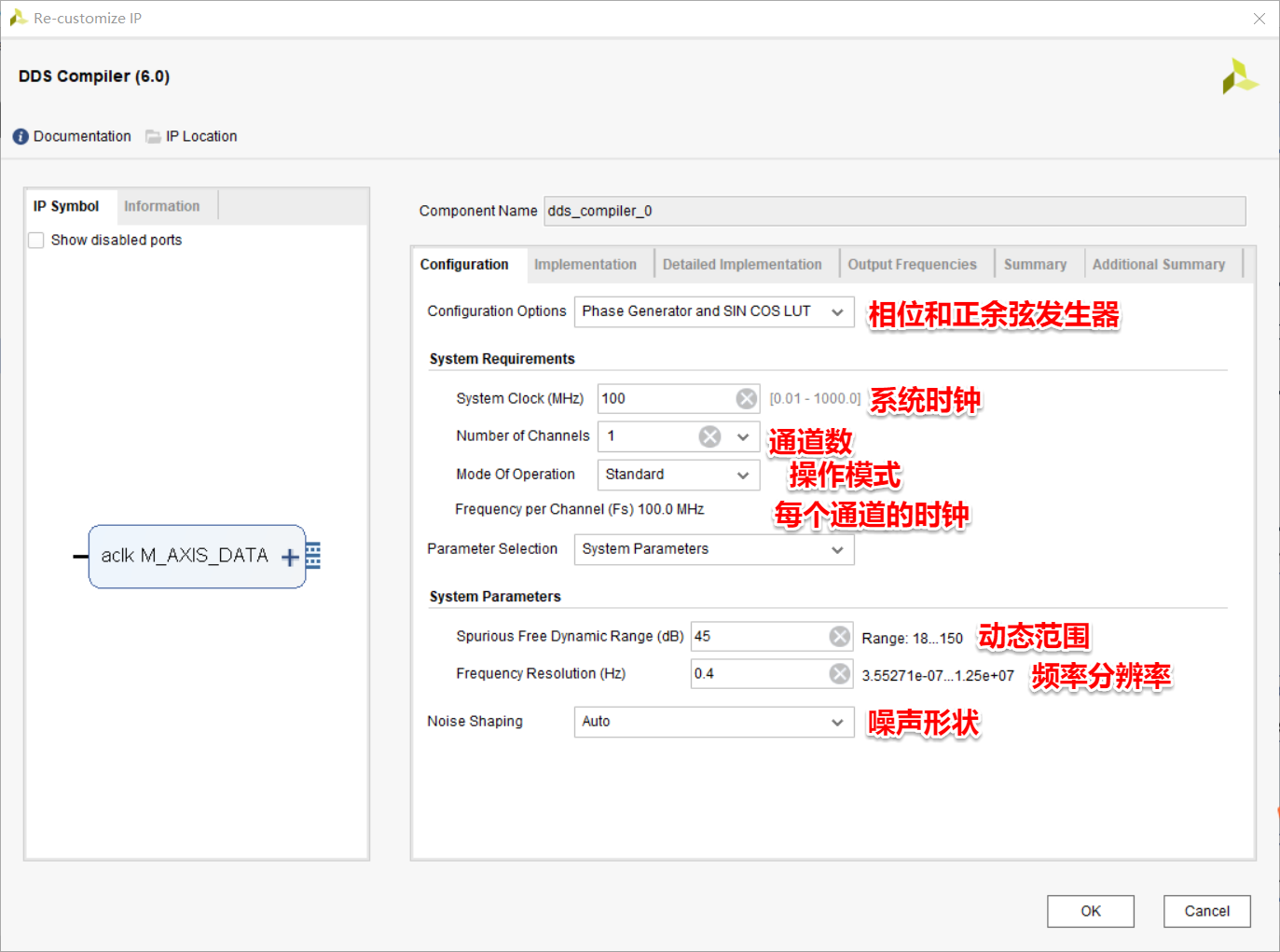

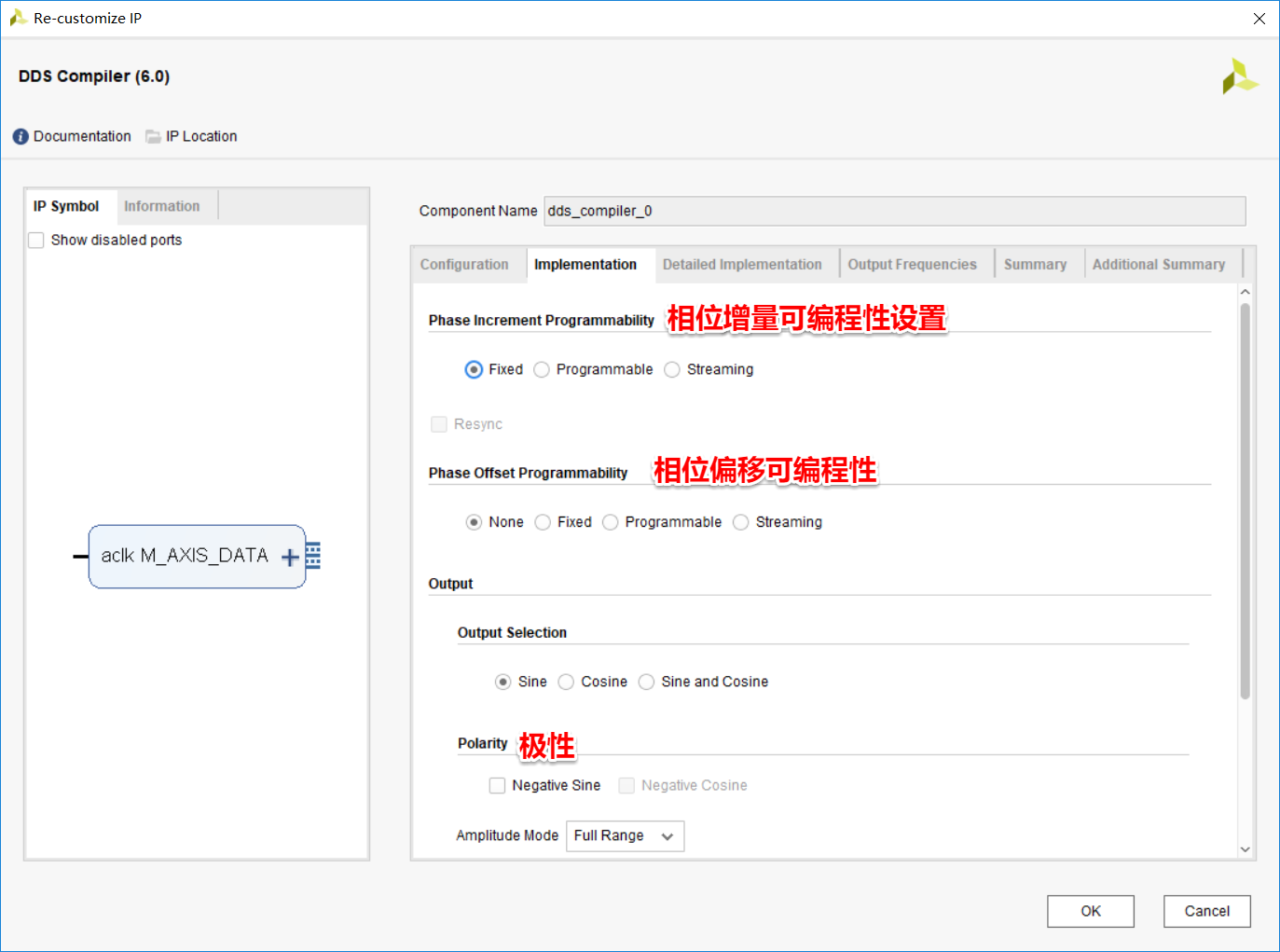

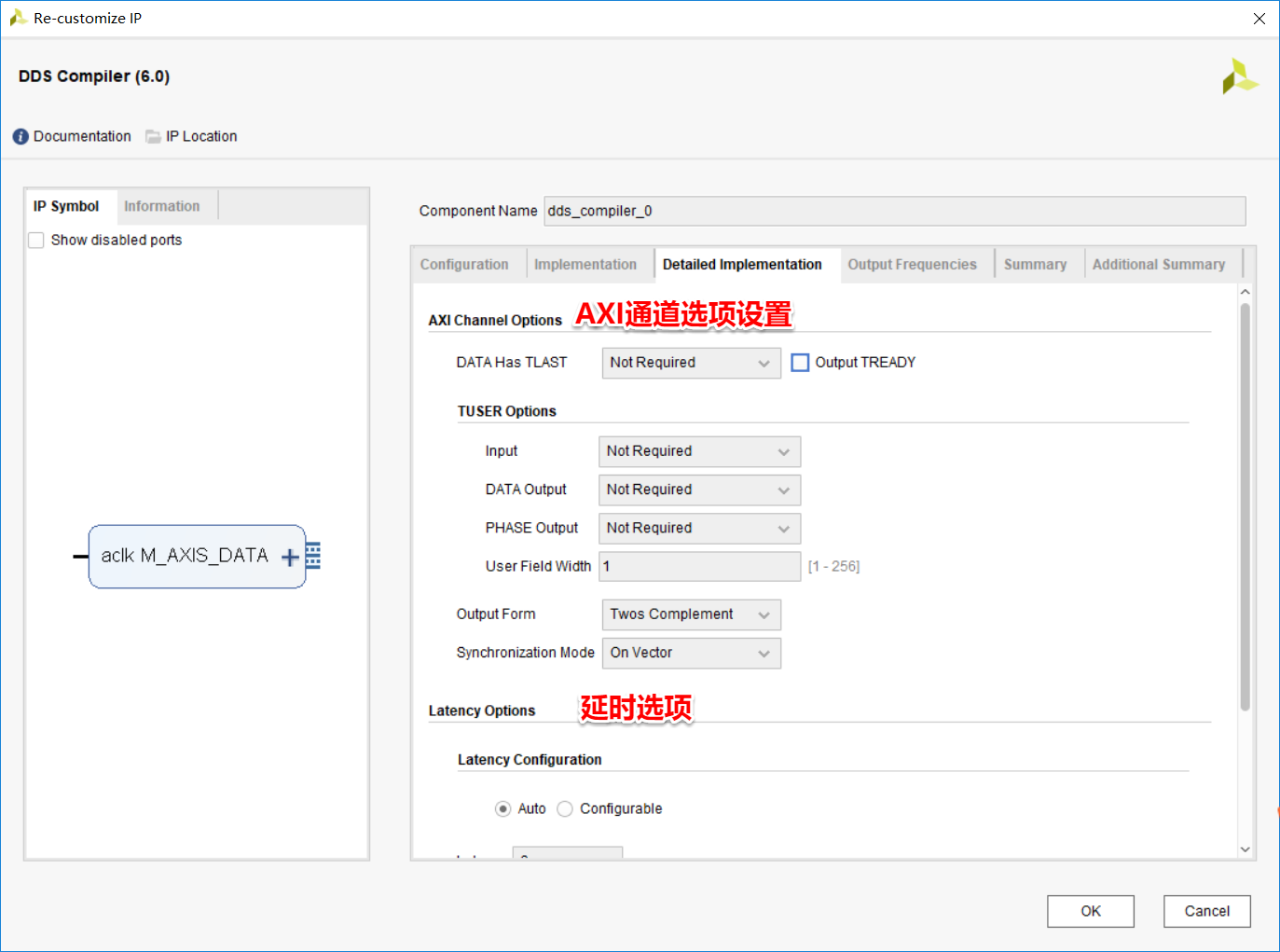

双击打开DDS IP核进入设置,对相关参数进行设置

本案例相关设置如下所示:

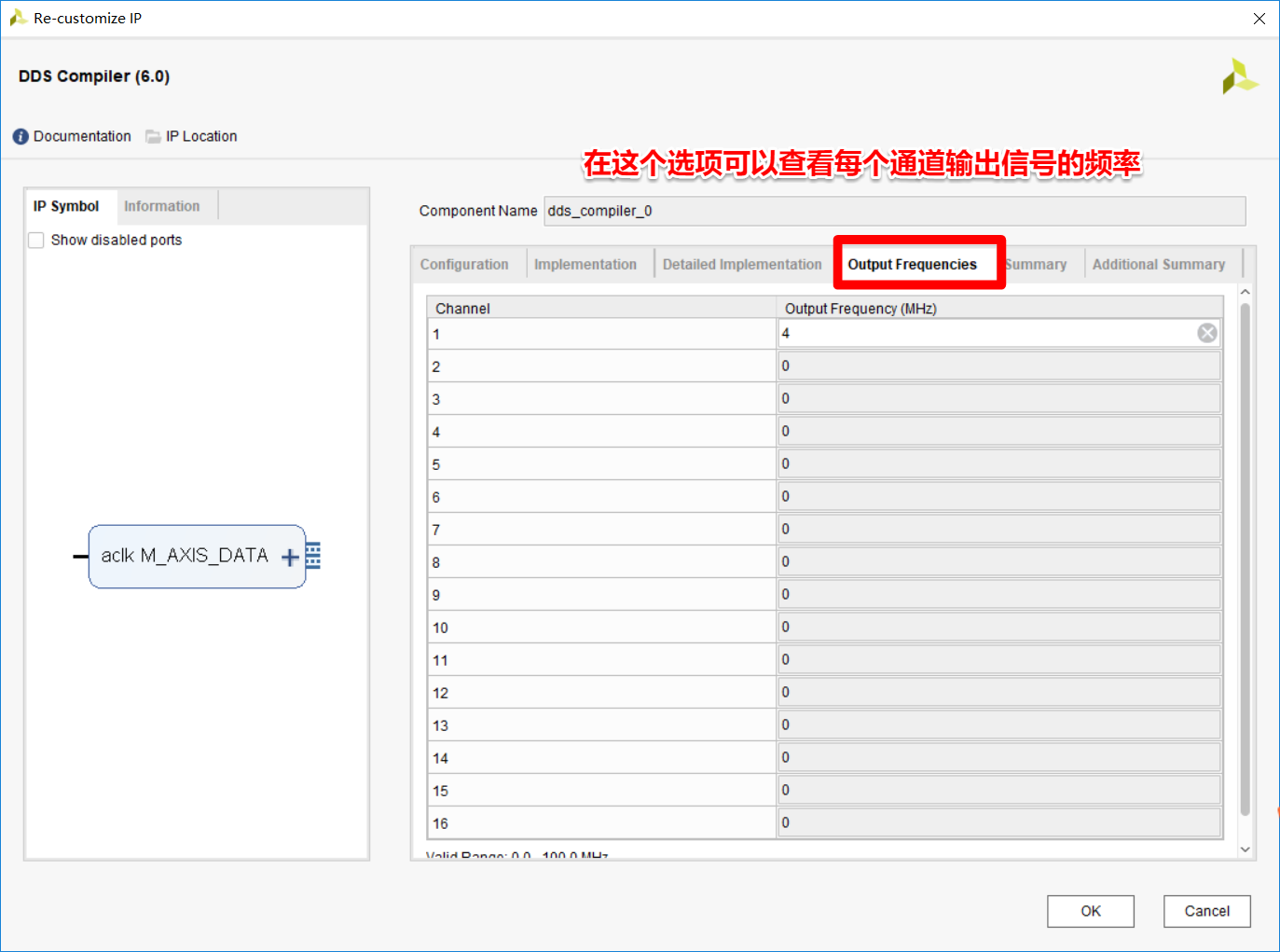

设置完相关参数之后,可以在Output Frequencies中查看频率信息。

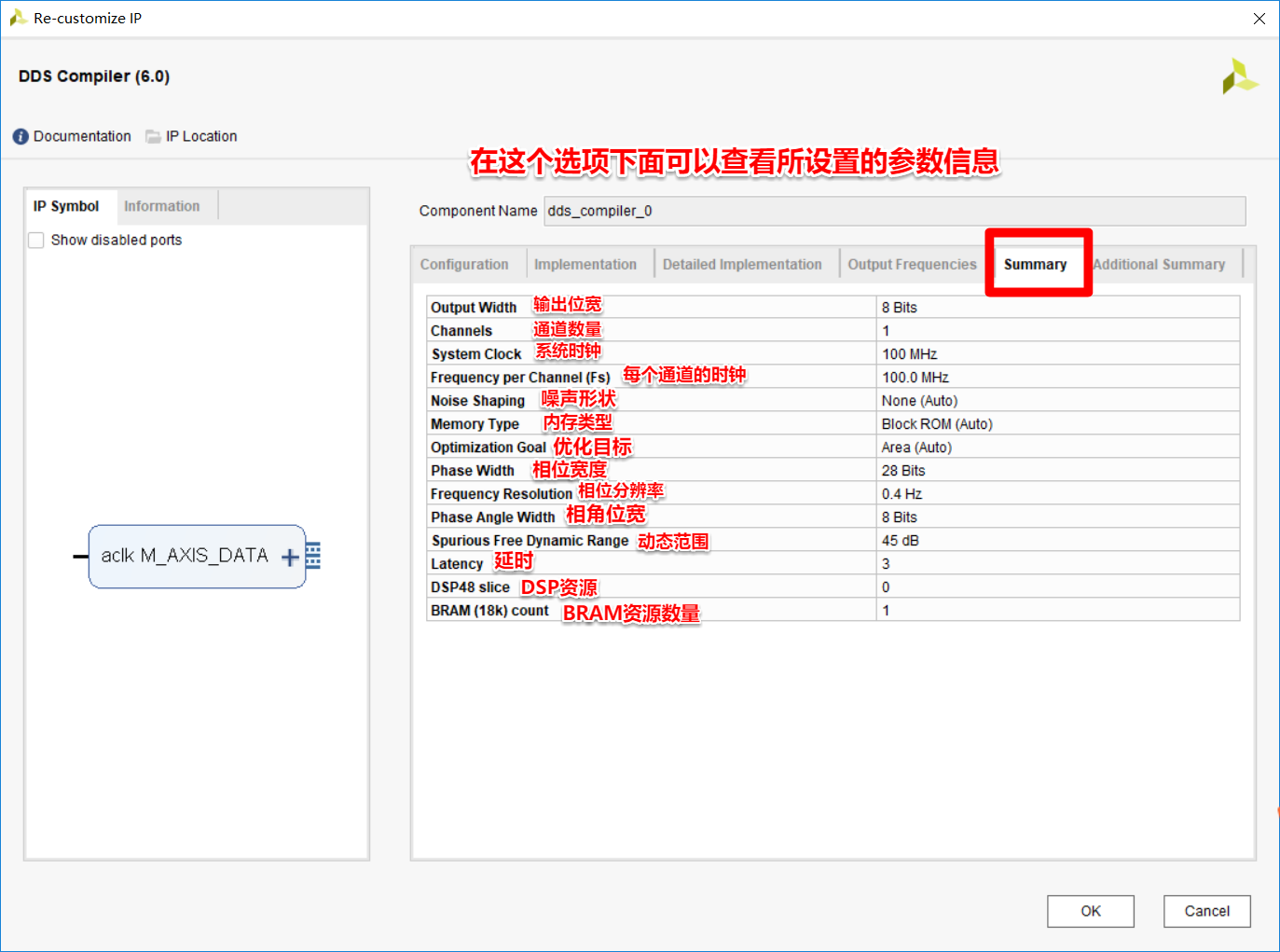

同样的,在Summary选项中查看设置的参数信息

混频

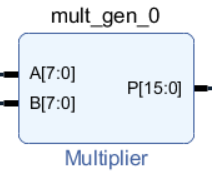

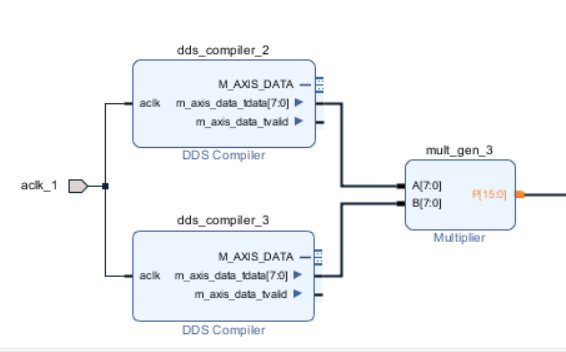

调用一个乘法器,将两路正弦信号进行混频,观察混频之后的信号。

连线

IP模块选择完成以后,就可以进行连线了,首先选中DDS IP的aclk管脚

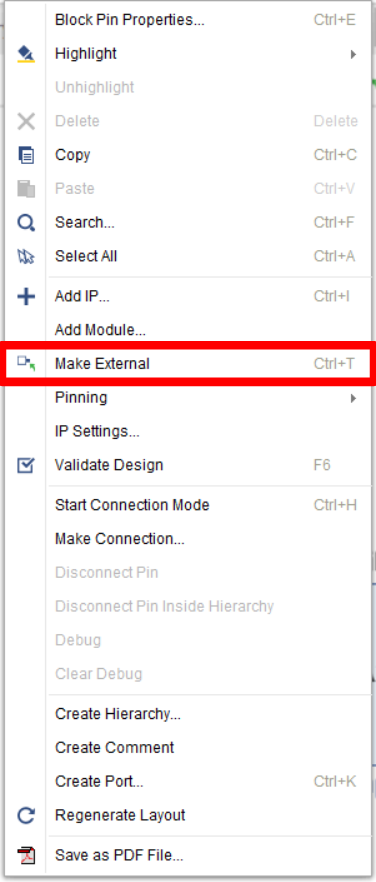

右键点击ackl引脚,点击make external

会产生一个aclk的输入管脚,然后把另外一个DDS IP核的aclk引脚连接到aclk输入管脚上。

然后把两个DDS的M_ASIS_DATA输出管脚分别连接到mult_gen IP核的A和B上,之后,右键点击P管脚,选择make external自动生成输出的管脚即可。

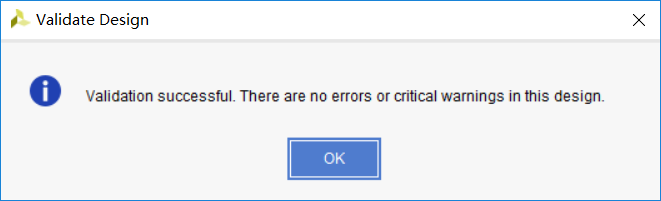

右键点击空白处,选择valid design,出现如下窗口,说明连接没有错误。

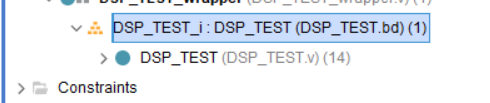

连线完成之后,ctrl+s保存一下工程,然后在source窗口里面,有一个类似于金字塔形状的选项

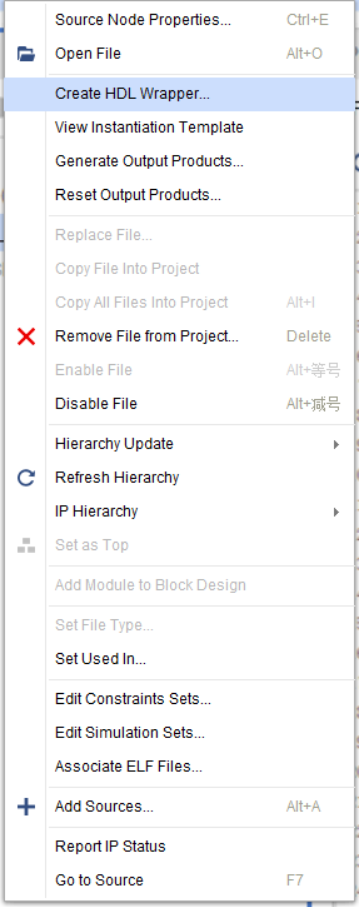

这个就是工程的BD文件,右键点击,选择create a HDL wapper,生成一个顶层文件。

仿真

工程建立完成以后,我们写个TB文件对其进行仿真,测试代码如下:

module tb_top(

);

reg aclk_0 ;

wire [31:0]S_0;

initial

aclk_0 = 1;

always #5 aclk_0 = ~aclk_0 ;

DSP_TEST_wrapper DSP_TEST_wrapper_i

(.aclk_0(aclk_0),

.S_0(S_0));

endmodule

将测试文件添加进工程,点击左侧run simulation即可用modelsim进行仿真(需要将VIVADO和modelsim进行关联,在SIMULATION选项进行设置)

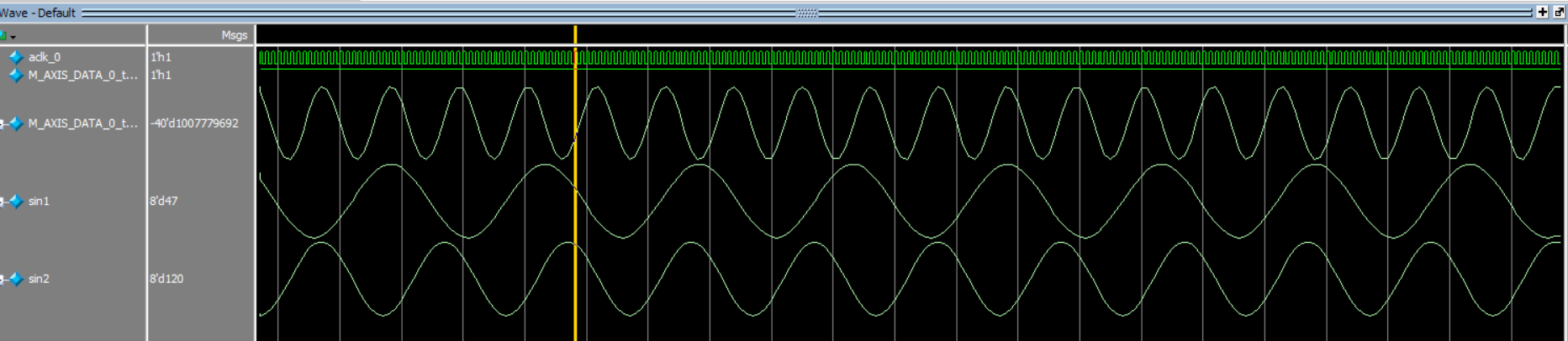

仿真结果如下图所示(我将两路正弦信号也连了管脚出来,便于仿真观察,也可以在modelsim中把DDS IP的信号添加进来观察,效果一样)

浙公网安备 33010602011771号

浙公网安备 33010602011771号