20135327郭皓——信息安全系统设计基础第六周学习总结

|

学习计时:共4小时 读书: 代码: 作业: 博客: |

|

一、学习目标 |

|

1. 了解ISA抽象的作用

2. 掌握ISA,并能举一反三学习其他体系结构

3. 了解流水线和实现方式

|

第四章 处理器体系结构

4.1 Y86指令集体系结构

4.1.1 程序员可见的状态

·程序员可见的状态:Y86程序中的每条指令都会读取或修改处理器状态的某些部分。

·“程序员”:即可是汇编代码写程序的人,又可是产生机器级代码的编码器。

·Y86的处理器状态类似IA32,有8个程序寄存器:%eax %ecx %edx %ebx %esi %edi %esp %ebp

·处理器的每个程序寄存器存储一个字。寄存器%esp被入栈,出栈,调用和返回指令作为栈指针。

·3个一位条件码:ZF SF OF

·Y86程序用虚拟地址来引用存储器位置。

·硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地址。

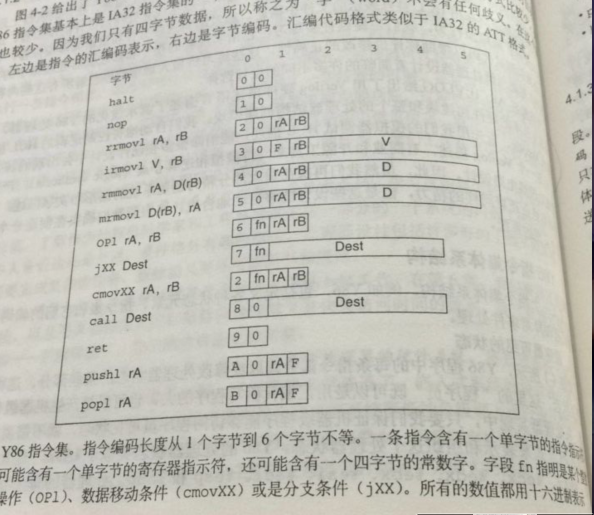

4.1.2 Y86指令

·Y86 ISA中各指令

·IA32的movl指令分为4个不同的指令:irmovl,rrmovl,mrmovl和rmmovl

·有4个整数操作指令:addl,subl,andl和xorl

·7个跳转码:jmp,jle,ji,je,jne,jge和jg

·6个条件传送码:cmovle,cmovl,cmove,cmovne,cmovge和cmovg

·call:将返回地址入栈,然后跳到目的地址。 ret:从这样的过程调用中返回。

·pushl和popl:入栈和出栈

·halt:停止指令的执行

4.1.3 指令编码

·字节分为两个部分,每部分4位,高4位是代码部分,低部分是功能部分

4.1.4

·状态码Stat:

值1 AOK 正常操作

值2 HLT 处理器执行halt指令

值3 ADR 遇到非法地址

值4 INS 遇到非法指令

4.2 逻辑设计和硬件控制语言HCL

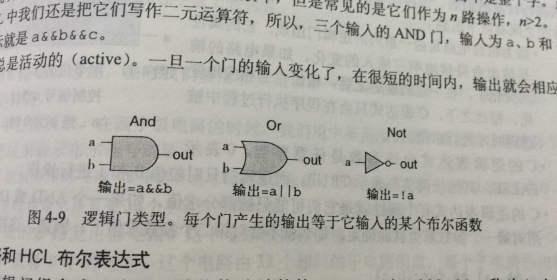

4.2.1 逻辑门

4.2.2 组合电路和HCL布尔表达式

·组合电路:将很多逻辑门组成一个网

·两条限制:

两个或多个逻辑门的输出不能连接在一起。

这个网必须是无环的

4.2.3 字级的组合电路和HCL整数表达式

p245

4.2.4 集合关系

iexpr in {iexpr1,iexpr2,······,iexprk}

被测试的值:iexpr 待匹配的值:iexpr1~iexprk

4.2.5 存储器和时钟

·时钟寄存器:存储单个位或字,时钟信号控制寄存器加载输入值。

·随机访问存储器:存储多个字,用地址来选择该读或该写哪个字。

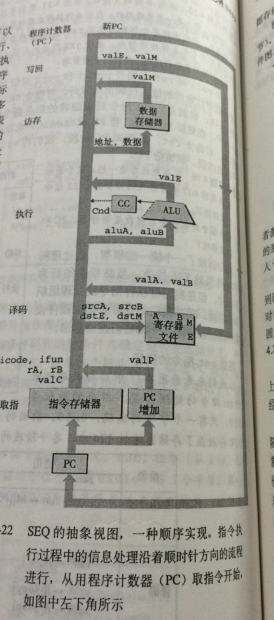

4.3 Y86的顺序实现

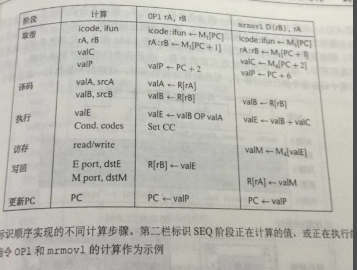

4.3.1 将处理组织成阶段

·取指(fetch):从存储器读取指令字节

·译码(decode):从寄存器文件读入最多两个操作数

·执行(execute)

·访存(memory):将数据写入存储器或者从存储器读出数据

·写回(write back):最多可以写两个结果到寄存器文件

·更新PC(PC update):将PC设置成下一条指令地址

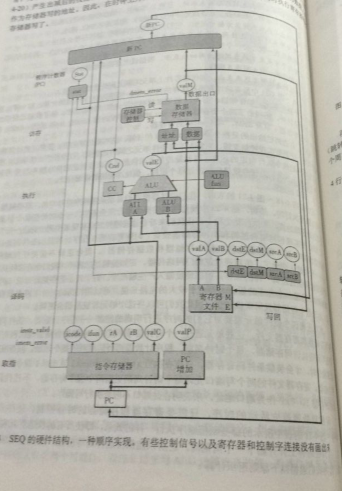

4.3.2 SEQ硬件结构

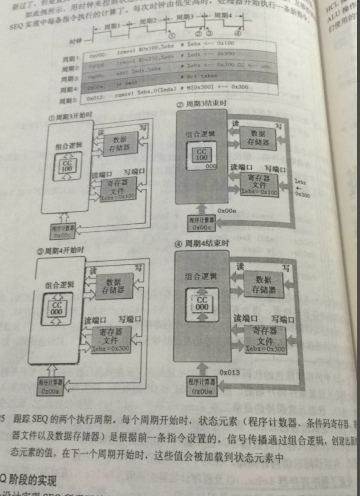

4.3.3 SEQ的时序

4.3.4 SEQ阶段的实现

1.取指阶段

2.译码和写回阶段

3.执行阶段

4.访存阶段

5.更新PC阶段

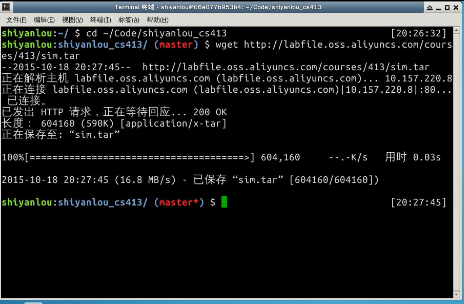

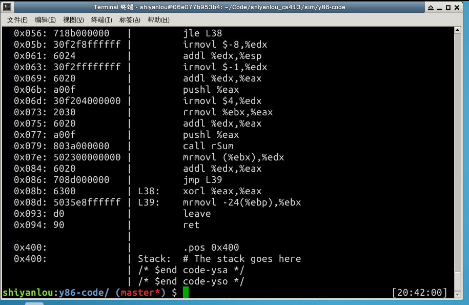

实验五:

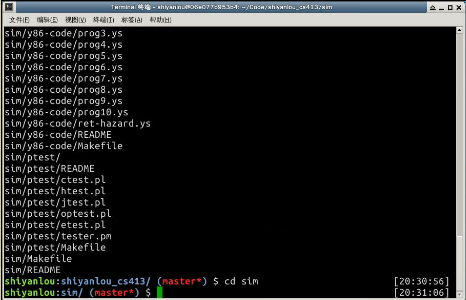

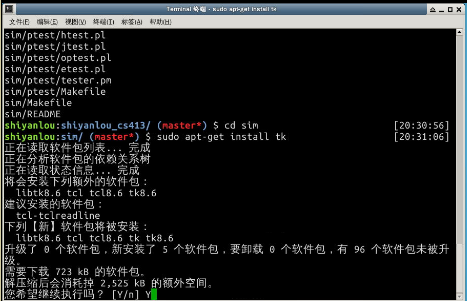

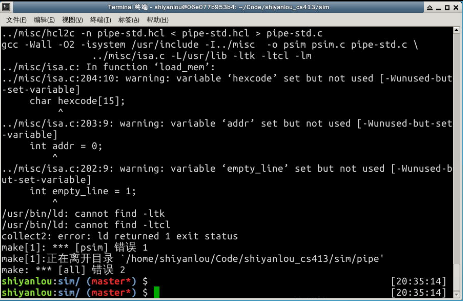

构建YIS环境:

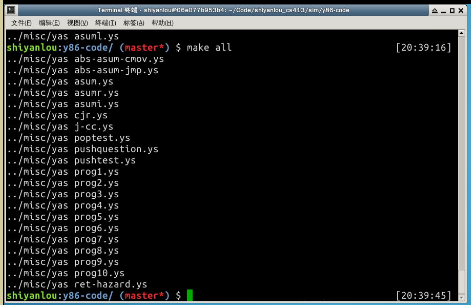

YIS测试:

汇编代码

浙公网安备 33010602011771号

浙公网安备 33010602011771号