2017-2018-1 20155306 《信息安全系统设计基础》第9周学习总结

2017-2018-1 20155306 《信息安全系统设计基础》第9周学习总结

教材学习内容总结

第6章 存储器层次结构

在简单模型中,存储器系统是一个线性的字节数组,而CPU能够在一个常数时间内访问每个存储器位置。实际上,存储器系统是一个具有不同容量、成本和访问时间的存储设备的层次结构。CPU寄存器保存着最常用的数据。靠近CPU的小的、快速的高度缓存存储器作为一部分存储在相对慢速的主存储器中的数据和指令的缓冲区域。 存储器层次结构是可行的。

6.1 存储结构

6.1.1随机访问存储器

随机访问存储器分为两类:静态的(SRAM)和动态的(DRAM)。

1)静态RAM

SRAM将每个位存储在一个双稳态的存储单元里。只要有电,他就会永远保持他的值。即使有干扰来扰乱电压,当干扰消除时,电路就会恢复稳定值。

2)动态RAM

DRAM将每个位存储为对一个电容的充电。与SRAM不同,DRAM存储单元易受干扰。当电容的电压被扰乱后,他就永远不会恢复了。

SRAM和DRAM的特性:

1.只要供电SRAM就会保持不变。

2.SRAM的存取比DRAM快。

3.SRAM对干扰不敏感。

4.SRAM单元比DRAM单元使用更多晶体管,密度较低,更贵,功耗更大。

3)传统的DRAM

- 行地址i:RAS

- 列地址j:CAS

4)存储器模块

- DRAM芯片包装在存储器模块中,他是插到主板的扩展槽位上的。常见的包括168个引脚的双列直插存储器模块,以64位为块传送数据到存储控制器和从存储控制器传出数据,还包括72个引脚的单列直插存储器模块,以32位为块传送数据。

- 通过将多个存储器模块连接到存储控制器,能够聚合主存,当控制器收到一个地址A时,控制器选择包含A的模块k,将A转换为它的(i, j)的模式,并将(i, j)发送到模块k。

5)增强的DRAM

-

快页模式DRAM(FPM DRAM):异步控制信号,允许对同一行连续的访问可以直接从行缓冲区得到服务。

-

同步DRAM(SDRAM):同步的控制信号,比异步的快。

6)非易失性存储器

- 如果断电,DRAM和SRAM会丢失他们的信息,所以他们是易失的。

- 非易失性存储器,即使是在关电以后,也仍然保存着他们的信息。他们整体上都称为只读存储器(ROM)。

- ROM以他们能够被重新编程的次数和对他们进行重编程所用的机制来区分的。

7)访问主存

- 数据流通过称为总线(bus)的共享电子电路在处理器和DRAM主存之间来来回回。每次CPU和主存之间的数据传送都是通过一系列步骤来完成的,这些步骤称为总线事务。

- 读事务:从主存传送数据到CPU

- 写事务:从CPU传送数据到主存

- 总线:一组并行的导线,能携带地址、数据和控制信号。

- 每个网络应用都是基于客户端-服务器模型的。

- 一个应用是由一个服务器户端提供某种服务。服务器管理某种资源,并且通过操作这种资源来为它的客户端提供某种服务。

- 客户端-服务器模型中的基本操作是事务。

事务由四步组成:

- 当一个客户端需要服务时,它向服务器发送一个请求,发起一个事务。

- 服务器收到请求后,解释它,并以适当的方式操作它的资源。

- 服务器给客户端发送一响应,并等待下一个请求。

- 客户端收到响应并处理它。

6.1.2磁盘存储

磁盘是保存大量数据的存储设备。

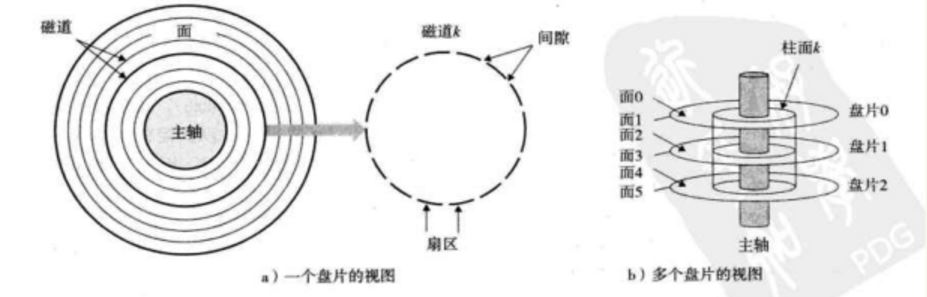

1)磁盘构造

磁盘是由盘片构成的。每个盘片有两个盘面,表面覆盖着磁性记录材料。盘片中央有个可以旋转的主轴,使得盘片以固定的旋转速率旋转。

2)磁盘容量

计算磁盘容量的公式:

磁盘容量 = 字节数/扇区 X 平均磁盘数/磁道 X 磁道数/表面 X 表面数/盘片 X 盘片数/磁盘

3)磁盘操作

访问时间的分类:

(1)寻道时间:

——移动传动臂所用的时间。

依赖于读/写头以前的位置和传动臂在盘面上移动的速度。

通常为3-9ms,最大可达20ms。

(2)旋转时间

——驱动器等待目标扇区的第一个位旋转到读/写头下

依赖于盘面位置和旋转速度。

最大旋转延迟=1/RPM X 60secs/1min (s)

平均旋转时间是最大值的一半。

(3)传送时间

依赖于旋转速度和每条磁道的扇区数目

平均传送时间= 1/RPM x 1/(平均扇区数/磁道) x 60s/1min

访问一个磁盘扇区内容的平均时间为平均寻道时间,平均旋转延迟和平均传送时间之和。

3)逻辑磁盘块

4)连接到I/O设备

- 像图形卡、监视器、鼠标键盘和磁盘这样的输入/输出(I/O)设备,都是通过I/O总线连接到CPU和主存的。

- 虽然I/O总线比系统总线和存储器总线慢,但它可以容纳种类繁多的第三方I/O设备。

5)访问磁盘

- DMA:直接存储器访问

——设备可以自己执行读或者写总线事务,而不需要CPU干涉的过程。

6.1.3固态硬盘(SSD)

- 一个SSD包由一个或多个闪存芯片和闪存翻译层组成,闪存芯片代替传统旋转磁盘中的机械驱动器,而闪存翻译层是一个硬件/固件设备,扮演与磁盘控制器相同的角色,将对逻辑块的请求翻译成对底层物理设备的访问。

- 随机读和写的性能差别是由底层闪存基本属性决定的。

6.2局部性

一个编写良好的计算机程序通常具有良好的局部性。他们倾向于引用邻近于其他最近引用过的数据项的数据项,或者最近引用过的数据项本身。这种倾向称为局部性原理。局部性有两种不同形式:时间局部性和空间局部性。有良好局部性的程序比局部性差的程序运行的更快。

6.2.1 对程序数据引用的局部性

6.2.2 取指令的局部性

循环体里的指令是按照连续的存储器顺序执行的,因此循环有良好的空间局部性,因为循环体会被执行多次,所以它也有良好的时间局部性。

代码区别于程序数据的一个重要属性时在运行时是不能被修改的。

6.2.3 局部性小结

量化评价一个程序中局部性的简单原则:

- 重复引用同一个变量的程序有良好的时间局部性

- 对于具有步长为k的引用模式的程序,步长越小,空间局部性越好

- 对于取指令来说,循环有好的时间和空间局部性。循环体越小,循环迭代次数越多,局部性越好。

6.3 存储器层次结构

6.3.1 存储器层次结构中的缓存

高速缓存:是一个小而快速地存储设备,它作为存储在更大、也更慢的设备中的数据对象的缓冲区域。 缓存:使用高速缓存的过程。

1)缓存命中

但程序需要第k+1层的某个数据对象d时,它首先在当前存储在第k层的一个块中查找d,如果d刚好缓存在第k层中,那么就是我们说的缓存命中。

2)缓存不命中

- 若第k层中没有缓存数据对象d,那么就是我们所说的缓存不命中。

- 替换或驱逐:覆盖一个现存的块的过程。

- 牺牲块:被驱逐的这个块。

- 替换策略:决定应该替换哪个块。

4)缓存管理

- 编译器管理寄存器文件,缓存层次结构的最高层。

- L1、L2、L3层的缓存完全是由内置在缓存中的硬件逻辑来管理的。

- DRAM主存是有操作系统软件和CPU上的地址翻译硬件共同管理的。

- 每个以太网适配器都有—个全球唯一的48位地址,它存储在这个适配器的非易失性存储器上。一台主机可以发送一段位,称为帧。每个主机适配器都能看到这个帧,但是只有目的主机实际读取它。

6.4 高速缓存存储器

早期计算机系统的存储器层次结构只有三层:CPU寄存器、DRAM主存储器和磁盘存储。

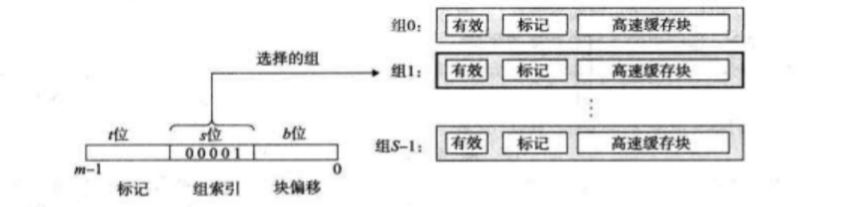

6.4.1 通用的高速缓存存储器组织结构

- 每个存储器地址有m位,形成M=2^m个不同的地址。

- 高速缓存组:S = 2^m个高速缓存组的数组

- 高速缓存行:B = 2^m字节的数据块组成

- 有效位:指明这个行是否包含有意义的信息

- 标记位:唯一地标识存储在这个高速缓存行中的块,t = m -(b+s)

一般而言,高速缓存的结构可以用元组(S,E,B,m)来描述。高速缓存的大小(或容量)C指的是所有块的大小的和。标记位和有效位不包括在内。因此,C=SEB。

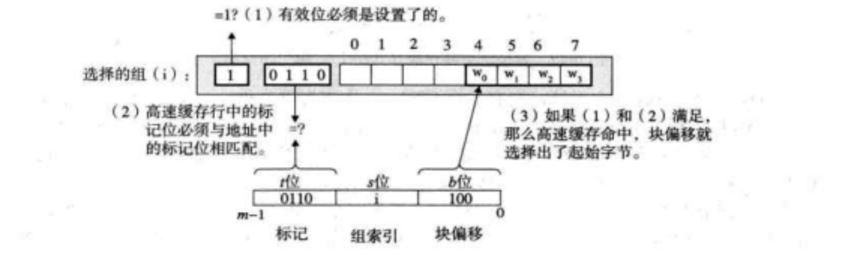

6.4.2 直接映射高速缓存

直接映射高速缓存:每个组只有一行的高速缓存。

高速缓存确定一个请求是否命中,然后抽取出被请求的字的过程,分为三步:组选择、行匹配、字抽取。

根据E(每个组的高速缓存行数)高速缓存被分为不同的类。每个组只有一行的高速缓存被称为直接映射高速缓存。

1)直接映射高速缓存中的组选择

直接映射高速缓存中的组选择

2)直接映射高速缓存中的行匹配

3)直接映射高速缓存中的字选择

直接映射高速缓存中的行匹配和字选择。在高速缓存块中,w0表示字w的低位字节,w1是下一字节,以此类推

4)直接映射高速缓存中不命中时的行替换

5)综合:运行中的直接映射高速缓存

6)直接映射高速缓存中的冲突不命中

当程序访问大小为2的幂的数组时,直接映射高速缓存中通常会发生冲突不命中。

6.4.3 组相联高速缓存

组相联高速缓存(I<E<C/B)。在一个组相联高速缓存中,每个组包含多于一个行。这里的特例就是一个2路组相联高速缓存。

1)组相联高速缓存中的组选择

2)组相联高速缓存中的行匹配和字选择

基本思路:组中的任何一行都可以包含任何映射到这个组的内存块。

3)组相联高速缓存中不命中时的行替换

6.4.4 全相联高速缓存

全相联高速缓存是由一个包含所有高速缓存行的组(即E=C/B)组成的。

1)全相联高速缓存中的组选择

只有一个组,默认组0,没有索引位,地址只被划分成了一个标记和一个块偏移。

2)全相联高速缓存中的行匹配和字选择

6.4.5 有关写的问题

直写,立即将w的高速缓存块协会到紧接着的低一层中

缺点:每次写都会引起总线流量。

写回,只有当替换算法要驱逐更新过的块时,才写到紧接着的低一层中

优点:符合局部性原理,显著的减少总线流量

缺点:增加了复杂性,必须为每个高速缓存行维护一个额外的修改位

写分配---通常写回对应

加载相应的低一层中的块到高速缓存中,然后更新这个高速缓存块。

非写分配---通常直写对应

避开高速缓存,直接把这个字写在低一层中。

6.4.6 一个真实的高速缓存层次结构的解剖

- 高速缓存既保存数据,也保存指令。

- 只保存指令的:i-cache

- 只保存程序数据的:d-cache

- 既保存指令又保存数据的:统一的高速缓存

6.4.7 高速缓存参数的性能影响

不命中率:不命中数量/引用数量

命中率:1-不命中率

命中时间:组选择、行确认和字选择的时间

不命中处罚:不命中需要的额外的时间

代码托管

(statistics.sh脚本的运行结果截图)

上周考试错题总结

其他(感悟、思考等,可选)

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 5000行 | 30篇 | 400小时 | |

| 第一周 | 20/20 | 1/2 | 10/15 | 第一章 |

| 第三周 | 130/210 | 1/2 | 21/36 | 第二章 |

| 第四周 | 70/ 280 | 1/4 | 10/46 | 第十章 |

| 第五周 | 91 / 371 | 1/6 | 23/69 | 第三章 |

| 第六周 | 308 / 648 | 1/8 | 31/100 | 第八、十章 |

| 第七周 | 2200 / 2848 | 1/10 | 25/125 | 第四章 |

| 第八周 | 1072 / 3492 | 1/12 | 41/166 | 第十一,十二章 |

| 第九周 | 1072 / 3492 | 1/15 | 30/196 | 第六章 |

| 尝试一下记录「计划学习时间」和「实际学习时间」,到期末看看能不能改进自己的计划能力。这个工作学习中很重要,也很有用。 | ||||

| 耗时估计的公式 | ||||

| :Y=X+X/N ,Y=X-X/N,训练次数多了,X、Y就接近了。 |

-

计划学习时间:30小时

-

实际学习时间:30小时

-

改进情况:

(有空多看看现代软件工程 课件

软件工程师能力自我评价表)

浙公网安备 33010602011771号

浙公网安备 33010602011771号