[HDL]4/8/16/32/64位乘法器的设计(转)

原文链接:http://www.cnblogs.com/craftor/archive/2010/09/03/1817251.html

Craftor原创,转载请保留此处。

4/8/16/32/64位乘法器的设计,单个时钟周期运算出结果。思路如下:

4位乘法器

a,b输入,y输出。使用case语句,对于输入a,y输出是b输入的16种可能。单个周期内可以输出结果。

8位乘法器

a,b输入,y输出。将a、b分成高4位和低4位,使用4位乘法器进行分别运算,然后进行相加。单个周期内可以输出结果。

16位乘法器

a,b输入,y输出。将a、b分成高8位和低8位,使用8位乘法器进行分别运算,然后进行相加。单个周期内可以输出结果。

32位乘法器

a,b输入,y输出。将a、b分成高16位和低16位,使用16位乘法器进行分别运算,然后进行相加。单个周期内可以输出结果。

64位乘法器

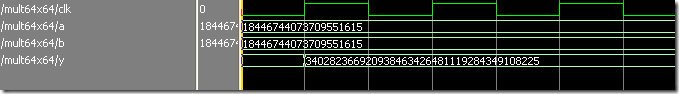

a,b输入,y输出。将a、b分成高32位和低32位,使用32位乘法器进行分别运算,然后进行相加。单个周期内可以输出结果。

以此类推,128位、256位乘法器也可以在单个周期内输出结果。

64位最大值相乘的仿真图如下:

VHDL版源代码:

http://myfpga.googlecode.com/files/mult4x4.vhd

http://myfpga.googlecode.com/files/mult8x8.vhd

http://myfpga.googlecode.com/files/mult16x16.vhd

http://myfpga.googlecode.com/files/mult32x32.vhd

http://myfpga.googlecode.com/files/mult64x64.vhd