ZYNQ笔记(4):PL触发中断

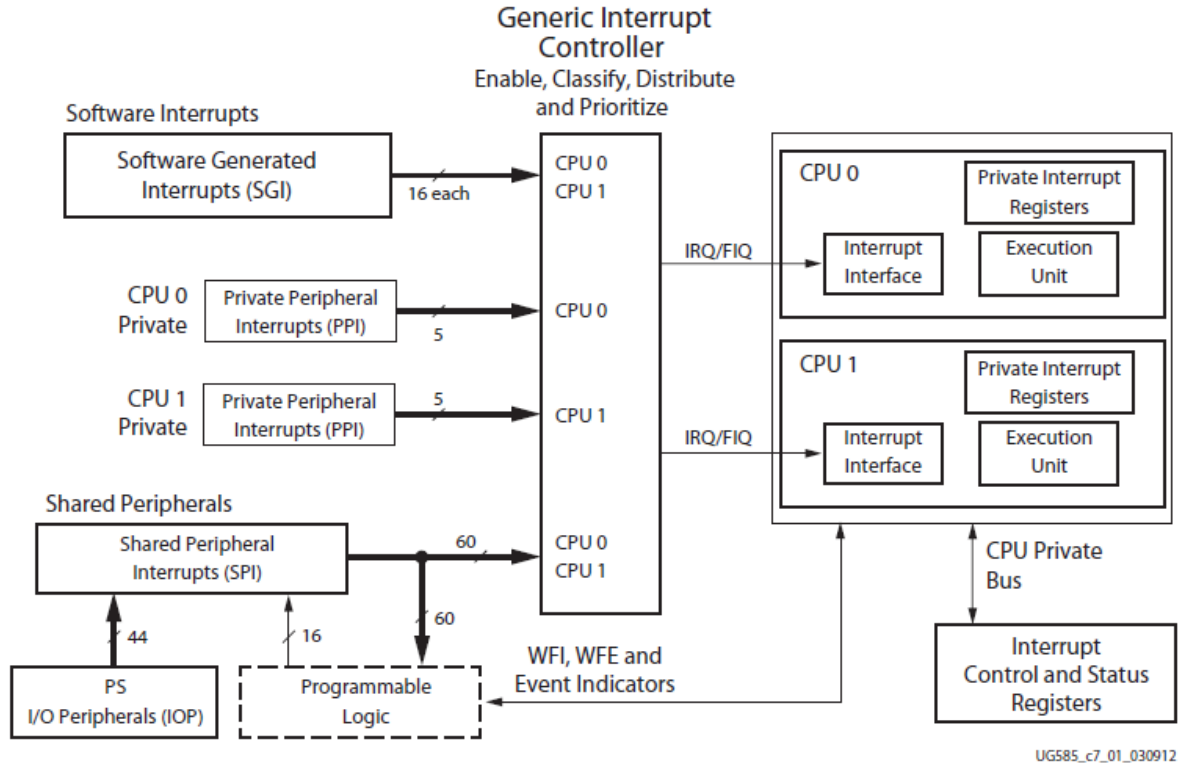

一、ZYNQ中断框图

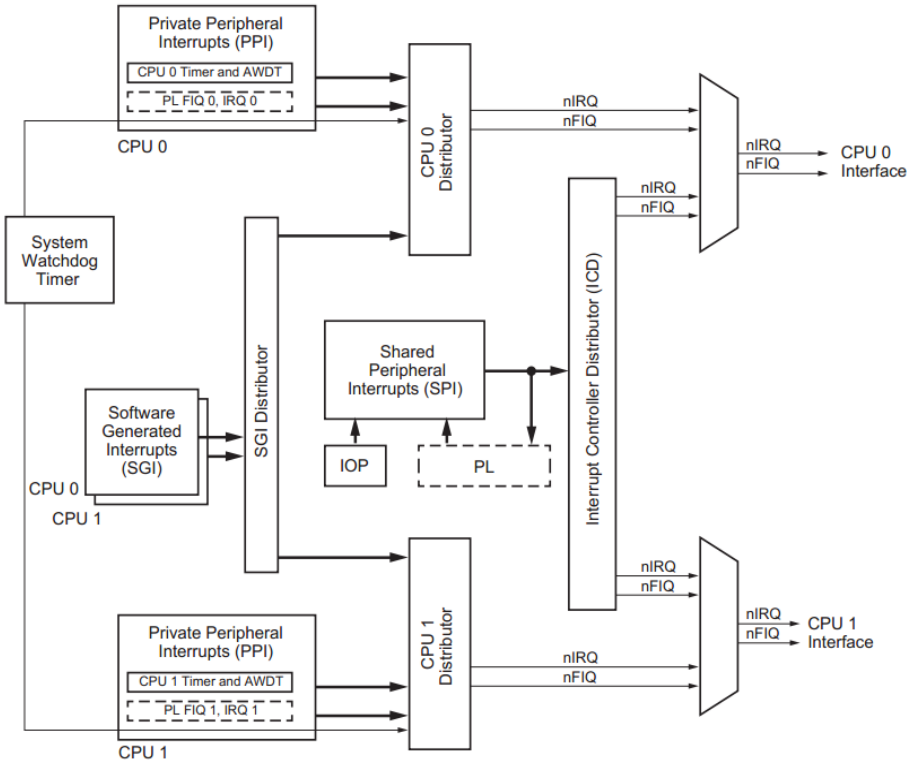

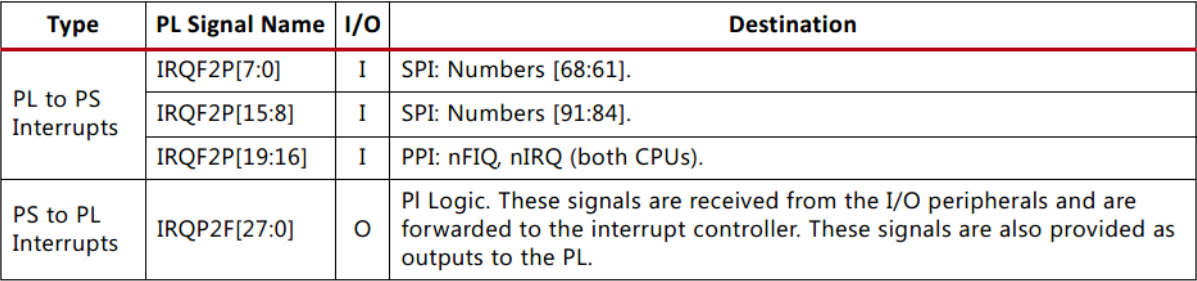

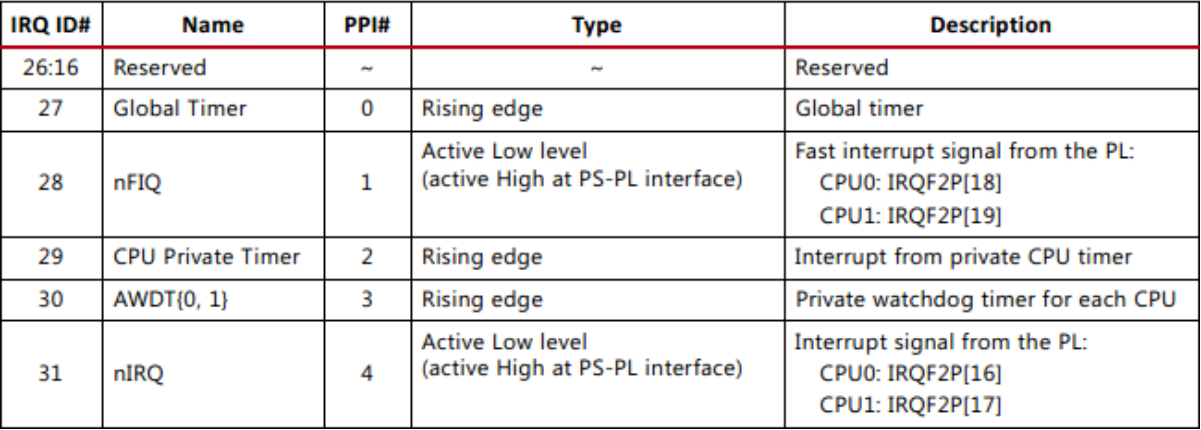

PL到PS部分的中断经过ICD控制器分发器后同时进入CPU1 和CPU0。从下面的表格中可以看到中断向量的具体值。PL到PS部分一共有20个中断可以使用。其中4个是快速中断。剩余的16个是本章中涉及了,可以任意定义。如下表所示。

二、ZYNQ中断分类

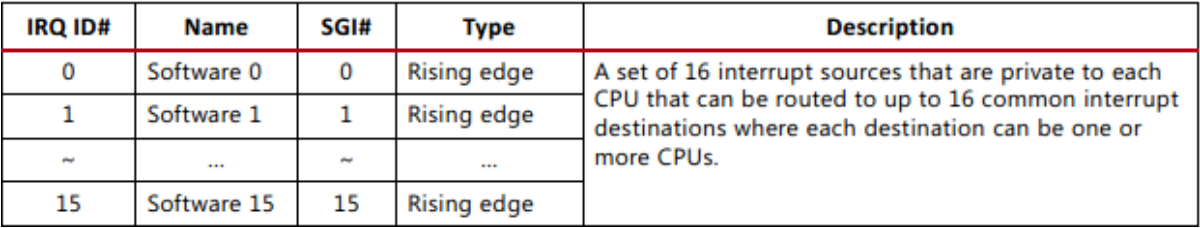

1.软件中断(SGI)

ZYNQ 2 个 CPU 都具备各自 16 个软件中断。通过 ICDSGIR 寄存器写入 SGI 中断号,以及指定目标 CPU 来产生一个软件中断。通过 CPU 私有总线实现写操作。CPU 能中断自己或者其他 CPU,或者所有的 CPU。通过读 ICCIAR(Interrupt Clear Pending)寄存器相应的比特位写1,可以清楚中断。所有的 SGI 为边沿触发,用于 SGI 的敏感性是固定的,不能修改。 ICDICFR0 寄存器是只读寄存器。

2.私有外设中断(PPI)

每个 CPU 连接一个私有的5个共享的外设中断,所有的中断敏感类型是固定的,不能修改。这里有 2 个 PL 到 CPU 的快速中断 nFIQ,私有中断包括 global timer、private timer 、watch dog 等。将来自 PL 的快速中断信号 FIQ 和中断信号 IRQ 翻转,然后送到中断控制器中。因此尽管在 ICDICFRI 寄存器内反映他们是活动低敏感信号,但是在 PS-PL接口为高电平活动。

3.共享外设中断(SPI)

共享中断就是 PL 的中断可以发送给 PS 处理。有 16 个 PL 的中断,它们可以设置为高电平或者低电平触发。中断控制器用于管理中断的优先级和接收用于 CPU 的这些中断。默认情况下,所有共享外设中断的复位是一个活动高电平。然而软件使用 ICDICFR2 和 ICDICFR5 寄存器将中断32、33和92编程为上升沿敏感。

PS:私有外设中断和共享外设中断都含有PL侧引入的中断,而软件中断是没有的。

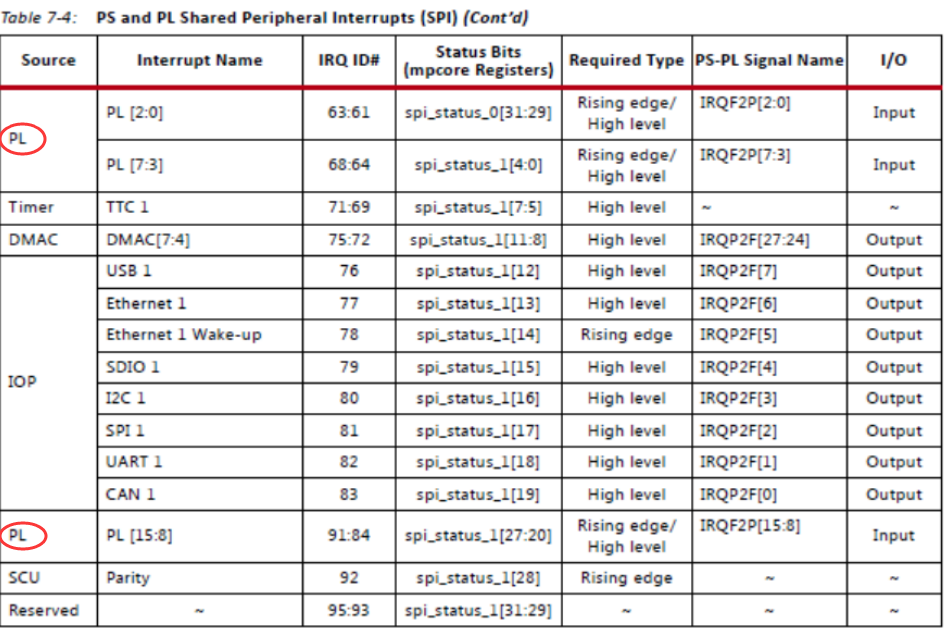

三、ZYNQ中断步骤

1.文字描述

第一步:初始化 cpu 的异常处理功能

第二步:初始化中断控制器

第三步:向 CPU 注册异常处理回调函数;

第四步:将中断控制器中的对应中断 ID 的中断与中断控制器相连接

第五步:设置 GPIO 的中断类型,比如高电平中断、低电平中断、上升沿中断、下降沿中断等。

第六步:设置 GPIO 中断回调函数,这里设置的回调函数是用于用户使用的。

第七步:使能 GPIO 的对应 PIN 的中断

第八步:使能中断控制器

第九步:使能异常处理功能

2.框图描述

四、操作注意事项

1.配置ZYNQ内核时需要将 Interrupts --- Fabric Interrupts 勾选上

2.因为是 PL 端,往往涉及引脚,所以需要添加约束文件,并且生成 bit 流文件,以此加载 SDK 开发环境

3.可以在 system.mss --- gpiops --- Important Examples --- xgpiops intr_example 中得到典型的 GPIO 中断的代码。

五、补充

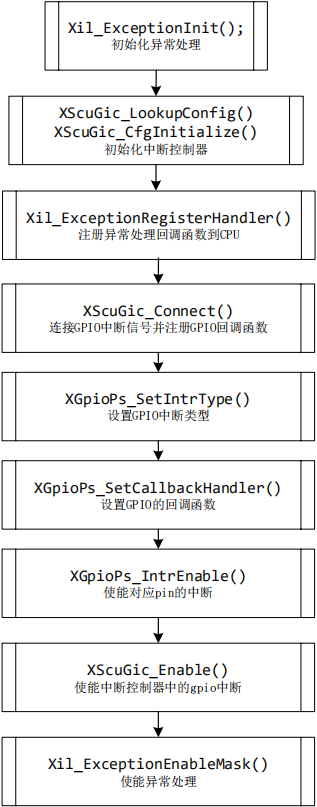

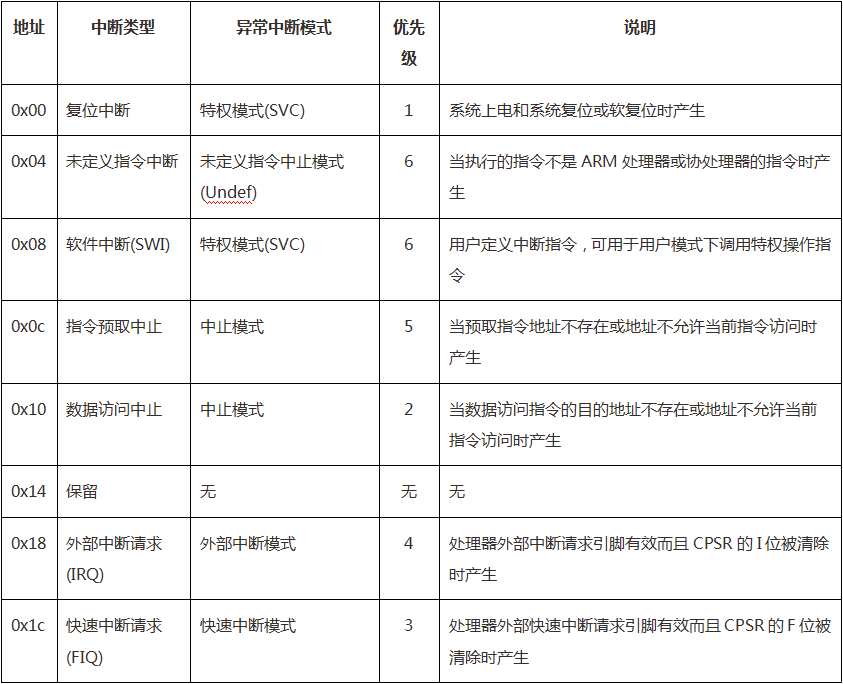

ARM体系架构的处理器中通常将低地址32字节作为中断向量表,当中断产生时会执行以下操作:

- 保存处理器当前状态,设置中断屏蔽位和各条件标志位

- 设置当前程序状态寄存器CPSR中相应位

- 将lr_mode寄存器设置成返回地址

- 跳转到中断向量地址执行,从而跳转到相应的中断程序中执行

- 执行中断处理函数内容

- 恢复被屏蔽的中断屏蔽位

- 返回到被中断指令的下一条指令处继续执行

zynq中低32字节作为中断向量表,每个中断占据4字节,这4字节通常存储一个跳转指令,从而跳转到中断解析程序中。这低32字节中断向量表如:

参考资料:

[1]V3学院FPGA教程

[2]何宾, 张艳辉. Xilinx Zynq-7000嵌入式系统设计与实现[M]. 电子工业出版社, 2016.

浙公网安备 33010602011771号

浙公网安备 33010602011771号