6、深入理解计算机系统笔记:存储器层次结构,存储技术(1)

1、如果你的程序需要的数据是存储在CPU寄存器中的,那么在执行期间,在零个周期内就能访问到它们。如果存储在高速缓冲中,需要1~10个周期。如果存储在主存中,需要50~100个周期。如果存储在磁盘上,需要约20000000个周期。

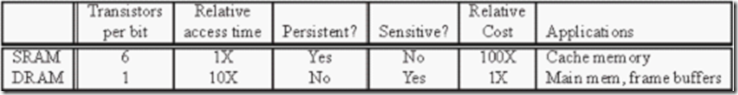

2、随机访问存储器(RAM,Random-access memory)分为两类-静态和动态的。静态RAM(SRAM)比动态RAM(DRAM)更快,但也贵很多。SRAM用来作为高速缓存存储器,即可以在CPU芯片上,也可以不在CPU芯片上。DRAM用来作为主存以及图形系统的帧缓冲区。

3、静态RAM

SRAM将每个位存储在一个双稳态(bistable)存储器单元(cell)中。每个单元是用一个六晶体管电路来实现的。这个电路的一个属性是:它可以无限制地保持在两个不同的电压配置(configuration)或状态(state)之一。其他任何状态都是不稳定的。

由于SRAM的双稳态特性,只要有电,它就会永远地保持它的值,即使有干扰,如电子噪音,当干扰消除,电路也能恢复到稳定值。

4、动态RAM

DRAM将每个位存储为对电容的充电。电容约为30×10-15F。

泄露电流的各种因素会导致DRAM单元在10~100毫秒内失去电荷。计算机运行的时钟周期是以纳秒来衡量的。

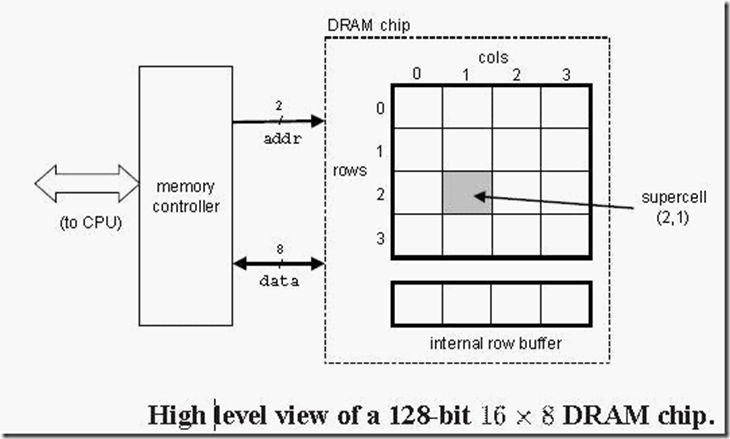

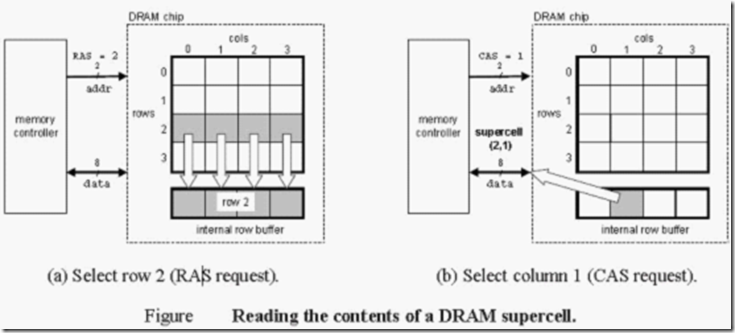

计算机界,倾向于把DRAM的阵列单元称为单元(cell),电路设计者倾向于称之为字(word)。这里称为supercell。

从图中可以看出,二维阵列组织的缺点就是必须分两步发送地址,这增加了访问时间。

5、168个管脚的双列直插存储器模块(Dual Inline Memory Module,DIMM),它以64位为块传送数据到存储控制器和从存储控制器传出数据;72个管脚的单列直插存储器模块(Single Inline Memory Module,SIMM),它以32位为块传送数据。

6、SDRAM(synchronous DARM,同步DRAM),SDRAM用与驱动存储器相同的外部时钟信号的上升沿来代替许多这样的控制信号。

DDR SDRAM(double data-rate synchronous DRAM,双倍数据数率同步DRAM)。DDR SDARM是对SDRAM的一种增加,它通过使用时钟的两个边沿作为控制信号,从而使DRAM的速度翻倍。

7、EEPROM(electrically erasable programmable ROM,电子可擦除PROM),类似于DPROM,但是它不需要一个物理上独立的编程设备,因此可以直接在印制电路卡上编程。EEPROM能够编程的次数量级可达10e5次。闪存(flash memory)是一个类小的非易失性存储器,基于EEPROM,支持插拨。

8、存储在ROM设备中的程序通常称为固件(firmware)。

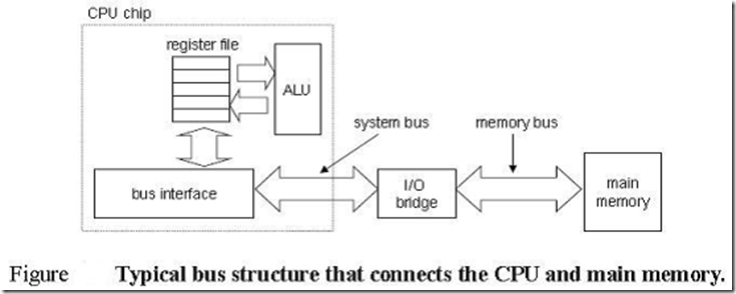

9、访问主存

读事务(read transaction)从主存传送数据到CPU;写事务(write transcation)从CPU传送数据到主存。

总线是一组并行的导线,能携带地址,数据,的控制信号。

1)读事务语句

movl A,%eax;

CPU将地址A放到存储器总线->主存从总线读出A,接收字x,然后将x放到总线上->CPU从总线读出字x,并将它copy到寄存器eax中。

2)写事务语句

movl %eax,A

CPU将地址A放到存储器总线,主存读出这个地址,等待接收数据字->CPU将数据字y放到总路上->主存从总线读数据字y,并将它存储在地址A。

<Computer Systems:A Programmer's Perspective>

浙公网安备 33010602011771号

浙公网安备 33010602011771号