【Xilinx-VDMA模块学习】-01- VDMA IP的GUI配置介绍

使用的是Vivado 2015.4,XC7Z020, AXI Video Direct Memory Acess(6.2)。

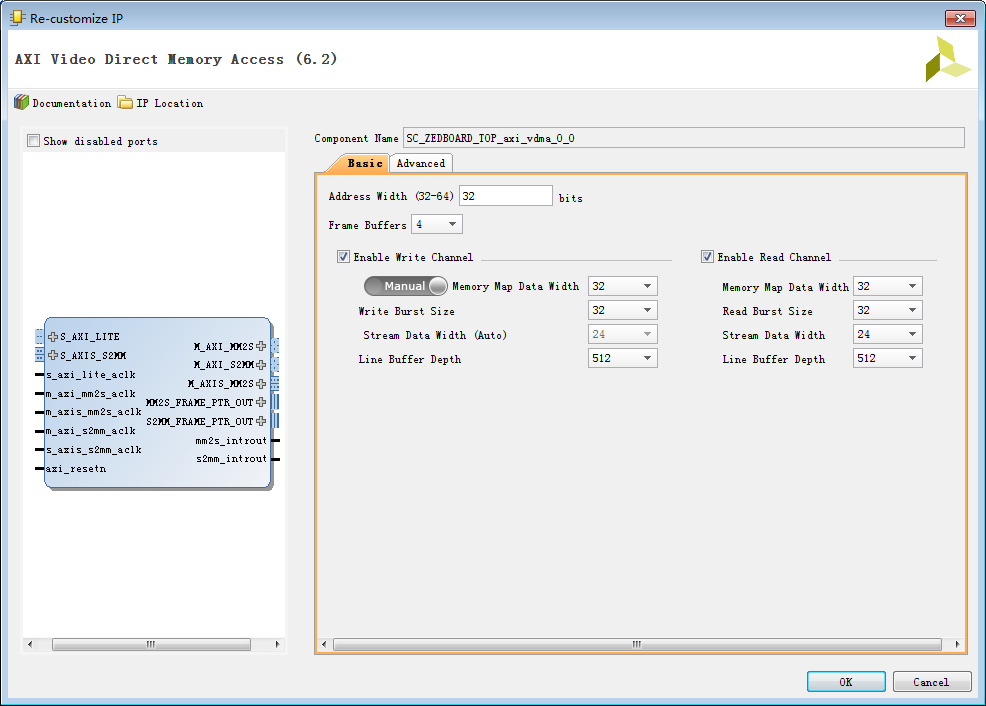

在我的系统中,GUI配置图片如下:(其实和默认配置没有太大区别)

下面介绍VDMA IP内各个参数的配置说明。

1.Basic标签页

Address Width:数据线位宽

除非内存地址空间大约32位,一般就配置成32位了,因为所做的板子DDR只有512MB

Frame Buffers:帧缓冲数

用来缓冲输入图像的帧缓存数量,最大可以选择32帧,在这里选择4就可以了。

据我所了解这个值一般最小设置为3,因为VDMA有一个读通道,一个写通道,在实际使用时一般都是写完了一帧数据,然后再去读这一帧的数据(VDMA内有一种机制,保证读出的帧总是上一次写完的帧)。这样能够防止读取到的图像被撕裂或者别的情况发生。

正常情况下的读写速率一般相同或有可能是写入速度略高于读取速率,在图像写入和读出稳定后,为了保证写入的帧不重叠到读取帧上,Frame Buffers设置为3即可解决。

设置为3时,同一时刻的读写帧组合如下:

FRAME0/FRAME2

FRAME1/FRAME0

FRAME2/FRAME1

读写通道:

Memory Map Data Width: 根据图像的像素数据位宽设置即可,我这里用的RGB三色 共24位数据,选32就可以了

Write/Read Burst Size: 存储空间AXI读写的突发读写数量大小

Stream Data Width:数据流AXIS位宽,RGB 24位,

Line Buffer Depth:数据流AXIS的缓存深度,用来缓存图像数据每一行数据的buffer深度。在xapp1205文档中第6页提到read and write side line buffers inside the AXI Video DMA core are

set to accommodate about one fourth of a line.我这里图像是640*480,这里设置的512,总之在读写速率相同的情况下这个值可以设置的稍微小一些,但最小也要超过行长度的1/4为好。

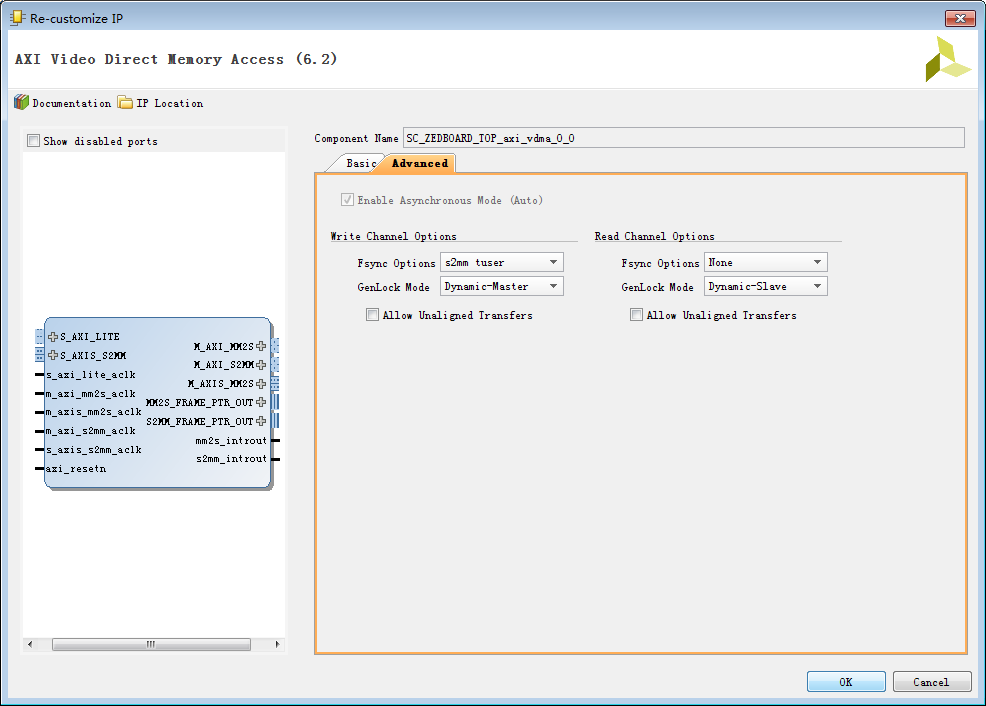

2.Advanced标签页,

因为VDMA里面的同步机制有些复杂,pg020文档里也说建议专业的选手再来配置这些东西,所以所有配置都按默认配置。当然我也想专业一点,尝试了许多次,但是感觉还是这个默认配置是最方便可靠的。

Write/Read Channel Options:

Fsyn Options(Write): 选择了s2mm_tuser,这样每一帧写图像的同步操作是根据前一级IP的AXIS输出总线内的tuser来触发的。这是很好的方法,帧同步起来方便快捷,不会出太大问题。

还可以配置成s2mm_fsync,选择这个后IP的GUI会多出一根信号输入线,这样就可以用诸如VTC的模块来进行全局的帧同步功能。选择这个功能后,VDMA写通道将会忽略AXIS总线中的tuser帧同步信号。

总之,我暂时还是用了第一种默认配置,第二种配置尝试过,但同步起来稍微要考虑的多了一些。也正是因为如此,Frame Buffers我选择了4,防止读写不同步时可能带来的问题。

Fsync Options(Read): 选择了None,Free Running,我的理解就是不需要单独外部同步触发信号,VDMA是通过M_AXIS_MM2S中tuser和反馈回来的tready信号握手成功后来开始触发一帧的读写的。

GenLock Mode: 写通道设置为Dynamic-Master,读通道设置为Dynamic-Slave

为了保证视频图像的读写实时性,需要内部有着一定的机制,这个机制就是通过GenLock模块来完成的。

Dynamic的前缀意思是读写GenLock会互相锁定,而另外两种没有前缀的Master和Slave则需要一些额外的软件开销,或者不太符合我的功能要求,我就没有仔细研究了。

我所理解的动态互相锁定:首先读写通道会有一个各自正在操作的帧编号告诉对方,默认写是0,读是2(3 Frame Buffers),由于读写速率不同或者是内存存取上出现延迟等等问题,有可能会导致,读写的帧编号错位(我猜的)。当主(即写通道)写操作完成后,会看一下从通道正在操作的帧编号,假如从的帧编号和主准备下次操作帧编号相同,主会选择跳过这个帧,并去下一帧进行写操作。从(读通道)读操作完成后,会读取主通道上一次操作的帧编号,并直接进行下次的读操作。

机制就是这样了,保证了读写操作不会同时发生在一个帧,导致数据的错误。但是我在想,对于摄像头的读取和显示是否可以不用这样设置,而是直接让读写发生在同一帧上,读取速率相同的前提下,让读取操作比写操作晚上几行,这样系统将会有着更低的延时,但这样也会需要更加精确的数据流控制。

Allow unaligned Transfers:默认不选择,这种高级功能就先不研究了,不选

这样,我的VDMA就配置完成了,读写通道的速率都是1080P要求的148.5M。通过另外的Video Test Pattern Generator、AXI_Interconnect、Video On Screen Display、Video Timing Controller、AXI4-Stream to Video Out来共同实现了VDMA图像读写和1080P视频显示的逻辑架构。

下一次,写一下VDMA和上面提到的这些模块如何工作,让视频图像显示起来。