【连载】【FPGA黑金开发板】Verilog HDL那些事儿--系统建模(二十三)

声明:本文为原创作品,版权归akuei2及黑金动力社区(http://www.heijin.org)共同所有,如需转载,请注明出处http://www.cnblogs.com/kingst/

第六章 :低级建模 - 系统建模

在第五章之中,我们为各个资源都进行封装。在第五章的结尾笔者留了这样一个问题

“对模块的封装建模,是为什么后期而作准备?”然而这一章就是答案。对!关于模块的封装就是为“系统建模”而作准备。

在现实中,一个系统是由几个部门组成。然而在 Verilog HDL + FPGA 的建模,一个简单的系统是由几个接口和控制模块建立而成。

6.1 实验二十二:SOS系统

|

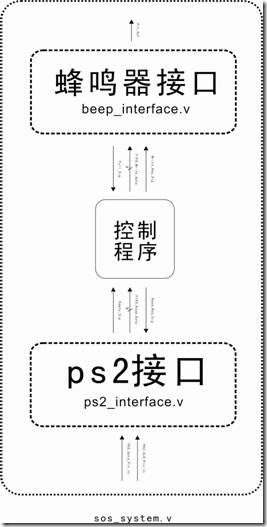

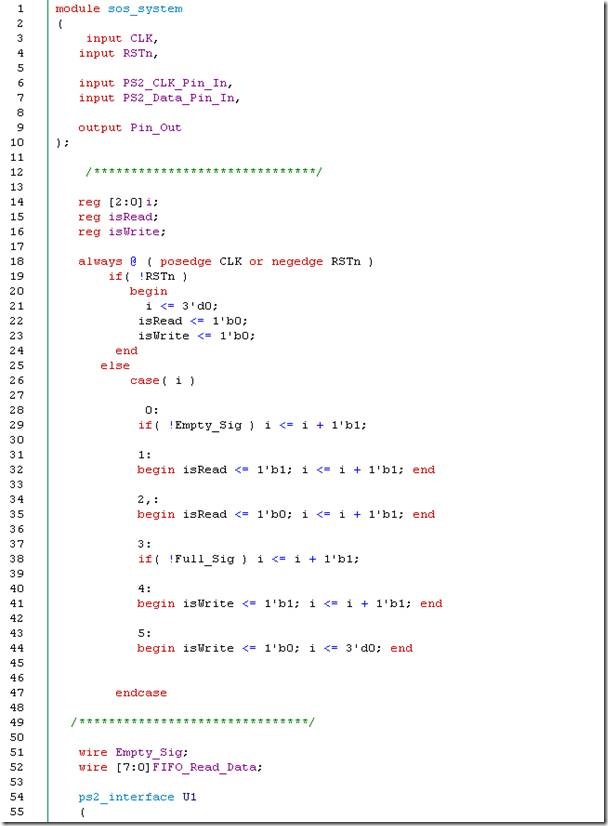

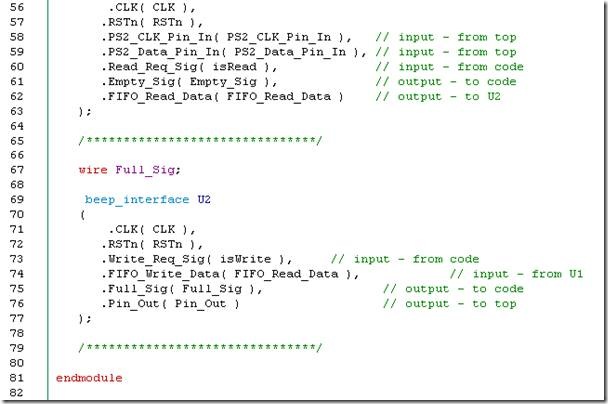

左图是SOS系统的“图形”。说得简单点,SOS系统就是 PS2接口 和 蜂鸣器接口 再加上控制程序组合而成。

该系统功能也很单纯,当你在键盘上按下S,它就会产生S摩斯码。如果你在键盘上按下O,它就会产生O摩斯码。

这个实验建立的初衷,是要给读者们更了解FIFO。如果只是单纯的“跨FIFO”数据传输而已,我们可以过于关心FIFO的“信息卡住”现象。因为上一波信息的最后一个信息,会被下一波的信息给挤出来。

相反的,如果是类似SOS系统,“跨FIFO”的数据传输,我们不得不谨慎看待。SOS的通码是一组的,假设我从PS2接口写入 SOS的通码蜂鸣器接口就得对SOS的通码作出反应。

所以说:

PS2接口扮演很重要的角色,因为断码不但在PS2接口的FIFO达到挤出的效果。然而断码同样也在蜂鸣器接口的FIFO里也达到挤出的效果。 |

实验二十二说明:

实验二十二也是挺简单的,笔者就不说什么了。在这里笔者对“FIFO信息卡住”现象考虑几个可能性:

1. 和接口的执行频率有关。

2. 读出时钟源和写入时钟源一样。

笔者也说不出实际的原因,但是死马也有死马的医疗方法 ... 哈哈!如果怕信息被卡住在FIFO里,就写入“无关紧要”的信息来达到挤出的效果就行了。

实验二十二将结论:

这个实验是给读者对“系统”一个概念。实际上很多初学者都被众多的“参考书”,的“系统”这一个概念搞得他们有许多误会。笔者以前也是如此,在笔者的概念中“系统”是“非常庞大,非常复杂”。其实是笔者被自己“想太多”愚弄了。在Verilog HDL 的世界里“系统”可以小得简单,大得复杂,最重要是设计的定义。

(⊙o⊙)!下载程序到黑金开发板后,就努力敲键盘的S键和O键,尽量求救吧。