PIO Core (译自Altera Quartus II Handbook, Volume 5 NII51007-9.0.0)

Quartus II Handbook, Volume 5

9.PIO Core

Altera Corporation March 2009

PIO核概述

具有Avalon接口的并行输入/输出(parallel input/output - PIO)核,在Avalon存储器映射(Avalon Memory-Mapped Avalon-MM)从端口和通用I/O端口之间提供了一个存储器映射接口。I/O端口既可以连接片上用户逻辑,也可以连接到FPGA与外设连接的I/O引脚。

PIO核提供容易的I/O访问用户逻辑或外部设备,在这种情况下“位控制”的方法是有效的。下面列举了几种应用的例子:

l 控制LED

l 获取开关数据

l 控制显示设备

l 片外设备的配置与通信,例如特定应用的标准产品(ASSP)。

PIO核中断请求(IRQ)输出能够确定一个基于输入信号的中断。PIO是SOPC Builder提供的并且易于集成到任何由SOPC Builder创建的系统中。这一章包含下面的部分:

l 功能描述

l 配置实例

l 在SOPC Builder中实例化PIO核

l 器件支持

l 软件编程模型

功能描述

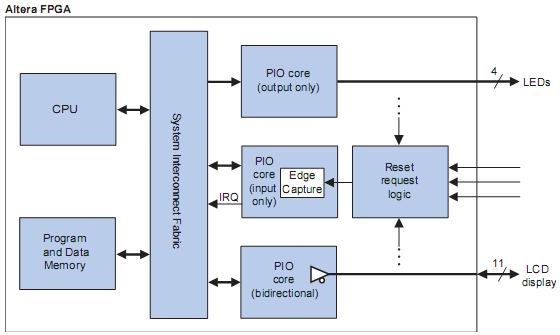

每个PIO核可以提供最多32个I/O端口。像微处理器这样的智能主机通过读/写寄存器映射的Avalon-MM接口控制PIO端口。在主机控制下,PIO核捕获输入端口的数据,并驱动数据到输出端口。当PIO端口直接与I/O引脚相连时,主机通过写PIO核中的控制寄存器对I/O引脚进行三态控制。图9-1是一个基于处理器系统使用多个PIO核的例子,其中,一个用于控制LED;一个用于捕获来自片上复位请求控制逻辑的边缘;另一个控制片外LCD显示。

在集成到SOPC Builder创建的系统时,PIO核有2种用户可见功能部件。

l 一个存储器映射的寄存器空间有4个寄存器:data、direction、interruptmask和edgecapture。

l 1~32个I/O端口。

I/O端口既可与FPGA内部逻辑相连接,也可驱动连接到片外设备的I/O引脚。寄存器通过Avalon-MM接口提供到I/O端口的接口。表9-2是这些寄存器的描述。在某些硬件配置中,某些不需要的寄存器不存在,读一个不存在的寄存器返回一个未定义值,而写一个不存在的寄存器无影响。

图9-1 使用多个PIO核的系统实例

数据输入/输出

PIO核的I/O端口既可以连接片上逻辑也可以连接片外逻辑,PIO核可以配置为输入、输出或双向。若用来控制双向I/O引脚,则PIO核提供具有三态控制的双向模式。

渎和写数据寄存器的硬件逻辑是独立的。读数据寄存器返回当前输入端口的值;写数据寄存器影响驱动输出端口的值。由于这些端口是独立的,因此读数据寄存器并不返回上次写入的数据。

边沿捕获

PIO核可配置为对输入端口进行边沿捕获(Edge Capture),它可以捕获低到高的跳变、高到低的跳变或者2种跳变均捕获。只要在输入端检测到边沿,该条件就会在edgecapture寄存器中指示。边沿的检测类型在系统创建时指明,且不能通过寄存器进行更改。

IRQ的产生

PIO核可以配置为在不同的输入条件下产生IRQ。IRQ产生的条件可以是下面两种:

l Level-sensitive(电平检测) — PIO核硬件能检测一个高电平,可在核的外部插入一个“非”门来检测低电平。

l Edge-sensitive(边沿检测) — PIO核的边沿捕获配置决定何种边沿类型能触发IRQ。

每个输入端口的中断可以分别屏蔽,中断屏蔽决定哪一个输入端口能产生中断。

配置实例

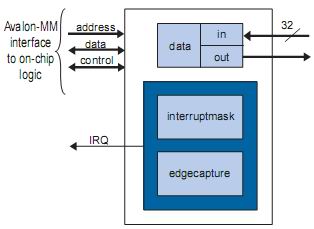

图9-2显示了一个带输入和输出端口以及支持IRQ的PIO核配置方框图。

图9-2 带输入端口、输出端口和IRQ支持的PIO核

图9-3显示了一个双向模式、不支持IRQ的PIO核配置方框图。

图9-3 带双向端口的PIO核

Avalon-MM接口

PIO核的Avalon-MM接口由一个单个的Avalon-MM从端口组成。从端口有Avalon-MM读写传输的基本功能,Avalon-MM从端口提供IRQ输出,使PIO核能够确定中断。

在SOPC Builder中实例化PIO核

设计者在SOPC Builder中使用MegaWizard向导来配置硬件特性设置。下面描述可用的选项。

MegaWizard向导有基本设置(Basic Settings)和输入选项(Input Options)两个标签。

Basic Settings(基本设置)

Basic Settings(基本设置)标签页允许设计者指定PIO端口的宽度和方向。

l Width(宽度)设置可以是1~32之间的任何整数值。如果设定值为n,则I/O端口宽为n位。

l Direction(方向)设置有4个选项,如表9-1所示。

表9-1 方向设置

|

设 置 |

描 述 |

|

Bidirectional (tristate) ports |

在这种模式下,每个PIO位共享一个设备引脚用于驱动或捕获数据。每个引脚的方向可以分别选择。如果设置FPGA I/O引脚的方向为输入,引脚的状态为高阻三态。 |

|

Input ports only |

在这种模式下,PIO端口只能捕获输入。 |

|

Output ports only |

在这种模式下,PIO端口只能捕获输出。 |

|

Both input and output ports |

在这种模式下,输入和输出端口总线是分开的,n位宽的单向总线。 |

Input Options(输入选项)

Input Options(输入选项)页允许设计者指定边沿捕获和IRQ产生设置。如果在基本设置页中选择了Output ports only(输出端口),Input Options(输入选项)页是不可用的。

边沿捕获寄存器

Synchronously Capture(同步捕获)

当Synchronously capture(同步捕获)打开时,PIO核包含边沿捕获寄存器, edgecapture。用户必须进一步指定边沿探测的类型:

l Rising Edge(上升沿)

l Falling Edge(下降沿)

l Either Edge(上升下降沿)

在输入端口,当一个指定类型的边沿出现时,边沿捕获寄存器允许核探测并且(可选)产生一个中断。

当Synchronously capture(同步捕获)关闭时,edgecapture寄存器不存在。

Enable Bit Clearing for Edge Capture Register(边沿捕获寄存器的使能位清除)

打开Enable bit-clearing for edge capture register(边沿捕获寄存器的使能位清除),允许你单独清除一个或多个边沿捕获寄存器中的位。为了清除给定的位,写1到边沿捕获寄存器的位。例如,为了清除边沿捕获寄存器的位6,可以写01000000到寄存器。

中断

当Generate IRQ(产生IRQ)被打开,且一个指定的事件在输入端口发生时,PIO核可以断言一个IRQ输出,用户必须进一步指定IRQ事件的原因:

l Level(电平)— 当一个指定的输入为高,并且在 interruptmask(中断掩码)寄存器中该输入的中断是使能的,核产生一个IRQ。

l Edge(边沿)— 当在边沿捕获寄存器中一个指定的位为高,并且在interruptmask(中断掩码)寄存器中该位的中断是使能的,核产生一个IRQ。

当Generate IRQ(产生IRQ)关闭时,interruptmask寄存器不存在。

仿真

Simulation页允许你在仿真期间指定输入端口的值。开启Hardwire PIO inputs in test bench以在测试工作台中设置PIO输入端口为一个特定的值,并且在Drive inputs to域中指定值。

器件支持

PIO核支持所有的Altera器件系列。

软件编程模型

这一节描述PIO核的软件编程模型,包括寄存器映射核用于访问硬件的软件结构。对于Nios II处理器用户,Altera提供了定义PIO核寄存器的HAL系统库头文件。PIO核不匹配由HAL支持的一般设备模型类型,所以不能通过HAL API或者ANSI C标准库访问。

Nios II嵌入式设计套件(Embedded Design Suite EDS)提供了几个例子设计,它们示范了PIO核的用法。特别是count_binary.c例子,使用PIO核驱动LED,并且用PIO边沿检测中断探测按钮按下。

软件文件

与PIO核相关的软件文件是altera_avalon_pio_regs.h,该文件定义了PIO核的寄存器映射,提供符号常量来访问底层硬件。

寄存器映射

Avalon-MM主外设,例如CPU,通过4个32位寄存器控制并与PIO核通信,表9-2假定PIO核的I/O端口被配置为n位宽度。

表9-2 PIO核的寄存器映射

|

偏 移 |

描 述 |

R/W |

(n-1) |

… |

2 |

1 |

0 | |

|

0 |

数据 |

读访问 |

R |

当前在PIO输入的数据值 | ||||

|

写访问 |

W |

驱动PIO输出的新值 | ||||||

|

1 |

Direction |

R/W |

对于每个I/O端口独立的方向控制,0设置方向为输入;1设置方向为输出 | |||||

|

2 |

Interruptmask |

R/W |

对每个输入端口IRQ允许/禁用。设置某位为1,允许相应端口的中断。 | |||||

|

3 |

edgecapture |

R/W |

对每个输入端口的边沿检测。 | |||||

|

4 |

outset |

W |

指定输出端口的某位置1 | |||||

|

5 |

outclear |

W |

指定输出端口的某位清0 | |||||

(1) 该寄存器是否存在取决于硬件配置,如果寄存器不存在,读寄存器返回一个未定义的值,写寄存器无影响。

(2) 写任何值到edgecapture,会清0所有位。

数据寄存器

读从Data寄存器返回的呈现在输入端口的值。如果PIO核硬件被配置为output-only(只输出)模式,读data寄存器将返回一个未定义的值。

写data寄存器将存储值到寄存器中以驱动输出端口。如果PIO核硬件被配置为input-only(只输入)模式,写data寄存器无影响。如果PIO核硬件被配置为双向模式,则仅当在 direction(方向)寄存器中相应的位被置1(输出)时,被寄存的值才会出现在输出端口上。

方向寄存器

direction(方向)寄存器控制每个PIO端口的数据方向,假定端口是双向的,当位n在方向寄存器中被置1时,端口n在data(数据)寄存器的相应位驱动输出值。

仅当PIO核硬件被配置为双向模式时,direction寄存器才存在。模式(输入、输出或双向)在系统创建时指定,并且在运行时不能修改。在输入或输出模式中,direction寄存器不存在,在这种情况下,读direction返回一个未定义的值,写direction无影响。

在复位后,方向寄存器的所有位都是0,所以所有双向I/O端口都被配置为输入。如果那些PIO端口被连接到FPGA器件的引脚,则这些引脚保持高阻状态。在双向模式,为了改变PIO端口的方向,要重新编程direction寄存器。

中断屏蔽寄存器

设置interruptmask Register(中断屏蔽寄存器)中的位为1允许相应PIO输入端口中断。中断行为取决于PIO核的硬件配置。见“中断行为”。

interruptmask寄存器仅当硬件被配置为能产生IRQ时才存在。如果PIO核不能产生IRQ,读interruptmask返回一个未定义的值,写interruptmask无影响。

在复位后,所有interruptmask寄存器的位都是0,所以所有的PIO端口中断都被禁用。

边沿捕获寄存器

如果edgecapture(边沿捕获)寄存器中的位n被设置位1,在输入端口n上的边沿将会被探测到。Avalon-MM主外设能够读edgecapture寄存器以确定是否有一个边沿出现在任何PIO输入端口。写任何值到edgecapture将清除寄存器中的所有位。

要探测的边沿的类型在系统创建时就已经选定在硬件中。edgecapture寄存器只能在硬件被配置位捕获边沿时存在。如果PIO核没有被配置成捕获边沿,读edgecapture将返回一个未定义的值,写edgecapture无影响。

输出置位和输出清零寄存器

你可以使用输出置位和输出清零(outset和outclear)寄存器置1或清0指定的输出端口的位。例如,要设置输出端口的第六位,可以写0x40(0100 0000)到outset寄存器。写0x08(0000 1000)到outclear寄存器可清0输出端口的第3位。

这些寄存器只有在选择Enable individual bit set/clear output register寄存器为开启时才可用。

中断行为

PIO核输出一个能够连接到任意在系统中的主外设的单个IRQ信号。主外设既能够读dagta寄存器,也能够edgecapture寄存器以确定那一个输入端口引发了中断。

当硬件被配置为电平敏感中断时,当data和interruptmask寄存器中相应的位是1时,IRQ被确定。当硬件被配置为边沿敏感中断时,当edgecapture和interruptmask寄存器中相应的位是1时,IRQ被确定。IRQ保持确定直到禁用interruptmask中相应的位或者写edgecapture相应的位以明确地确认为止。

软件文件

PIO核配套的软件文件如下。该文件提供了对硬件的底层访问。应用程序开发者不要修改这些文件。

l altera_avalon_pio_regs.h — 该文件定义了PIO核的寄存器映射,提供访问底层硬件的符号常数。该文件中的符号由设备驱动函数使用。

在默认安装Nios开发工具时,altera_avalon_pio_regs.h 文件在路径C:\altera\90\ip\altera\sopc_builder_ip\altera_avalon_pio\inc下。

altera_avalon_pio_regs.h 文件清单:

#ifndef __ALTERA_AVALON_PIO_REGS_H__

#define __ALTERA_AVALON_PIO_REGS_H__

#include <io.h>

#define IOADDR_ALTERA_AVALON_PIO_DATA(base) __IO_CALC_ADDRESS_NATIVE(base, 0)

#define IORD_ALTERA_AVALON_PIO_DATA(base) IORD(base, 0)

#define IOWR_ALTERA_AVALON_PIO_DATA(base, data) IOWR(base, 0, data)

#define IOADDR_ALTERA_AVALON_PIO_DIRECTION(base) __IO_CALC_ADDRESS_NATIVE(base, 1)

#define IORD_ALTERA_AVALON_PIO_DIRECTION(base) IORD(base, 1)

#define IOWR_ALTERA_AVALON_PIO_DIRECTION(base, data) IOWR(base, 1, data)

#define IOADDR_ALTERA_AVALON_PIO_IRQ_MASK(base) __IO_CALC_ADDRESS_NATIVE(base, 2)

#define IORD_ALTERA_AVALON_PIO_IRQ_MASK(base) IORD(base, 2)

#define IOWR_ALTERA_AVALON_PIO_IRQ_MASK(base, data) IOWR(base, 2, data)

#define IOADDR_ALTERA_AVALON_PIO_EDGE_CAP(base) __IO_CALC_ADDRESS_NATIVE(base, 3)

#define IORD_ALTERA_AVALON_PIO_EDGE_CAP(base) IORD(base, 3)

#define IOWR_ALTERA_AVALON_PIO_EDGE_CAP(base, data) IOWR(base, 3, data)

#define IOADDR_ALTERA_AVALON_PIO_SET_BIT(base) __IO_CALC_ADDRESS_NATIVE(base, 4)

#define IORD_ALTERA_AVALON_PIO_SET_BITS(base) IORD(base, 4)

#define IOWR_ALTERA_AVALON_PIO_SET_BITS(base, data) IOWR(base, 4, data)

#define IOADDR_ALTERA_AVALON_PIO_CLEAR_BITS(base) __IO_CALC_ADDRESS_NATIVE(base, 5)

#define IORD_ALTERA_AVALON_PIO_CLEAR_BITS(base) IORD(base, 5)

#define IOWR_ALTERA_AVALON_PIO_CLEAR_BITS(base, data) IOWR(base, 5, data)

/* Defintions for direction-register operation with bi-directional PIOs */

#define ALTERA_AVALON_PIO_DIRECTION_INPUT 0

#define ALTERA_AVALON_PIO_DIRECTION_OUTPUT 1

#endif /* __ALTERA_AVALON_PIO_REGS_H__ */

参考文献

[1] Altera Corp. Quartus II Handbook, Volume 5. NII51007-9.0.0. Altera Corporation. March 2009.

浙公网安备 33010602011771号

浙公网安备 33010602011771号