DUAL PORT RAM应用实例

作者:桂。

时间:2018-05-14 12:11:00

链接:http://www.cnblogs.com/xingshansi/p/9035522.html

前言

主要是Xilinx 常用模块汇总(verilog)【03】中双端口RAM的细节补充,限于篇幅,单独列出。

一、双端口RAM简述

具体细节参考ug473_7Series_Memory_Resources.pdf.

这里直接调用IP核。

二、IP核参数简述

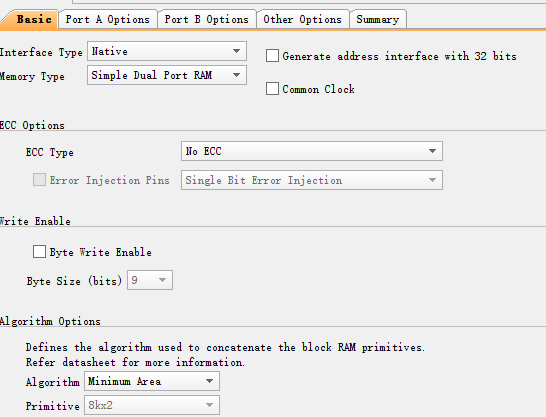

A-Page1

- Common Clock:同源时钟

- Generate adderss..:默认32bit地址,否则根据深度自动调节

- ECC:纠错

其他略.

B-Page2

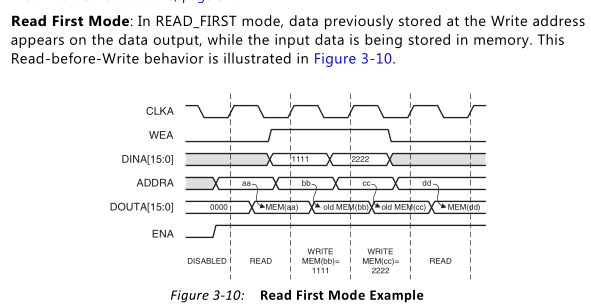

- Read First Operating Mode is supported when the Common Clock option is selected.

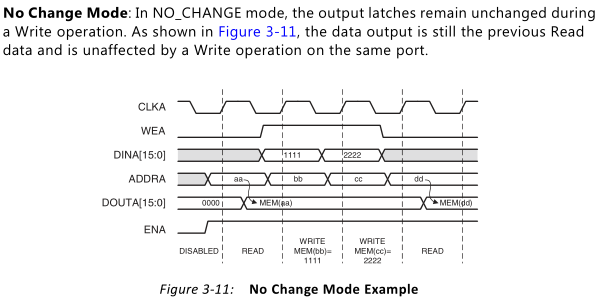

- no change mode

这里使用,通常选择no change mode。

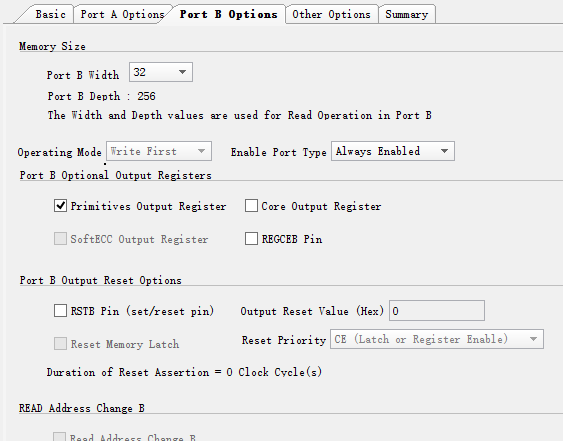

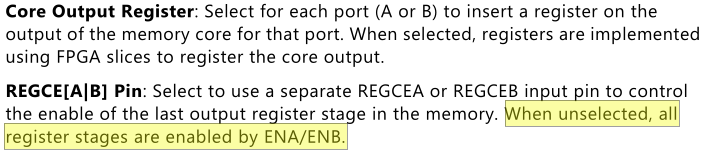

C-Page3

Port-A is used for write, and Port-B is used for read.(原语调用需要注意)

(PORT A/B同理):

在输出添加一个锁存器,即多延1拍,保证时序良好。

D-Page4

其他略。

E-Page5

略。

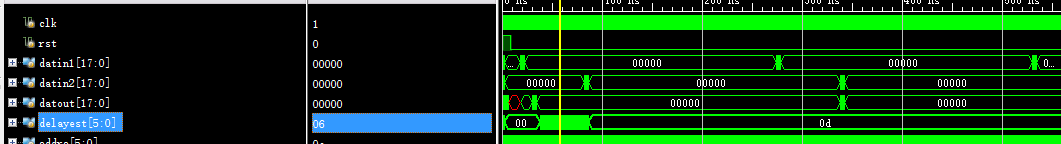

三、仿真验证

任务要求【简化】:

两路周期为64clocks【对应最大延迟数】的数据链,相差delay clocks,现在需要用DUAL PORT RAM进行对齐处理。

思路分析:

1)选1路为参考,一路进入DUAL PORT RAM修正;

2)修正思路:对于脉冲信号,信号高为有效->判断延拍数—>根据延拍数进行地址偏移->输出对齐的数据。

Testbench:

`timescale 1ns / 1ps /* Function: DPRAM for data aligned Author: Gui. Data: 2018年5月14日12:49:07 */ module dpram_tb; //parameter //parameter datwidth = 18; parameter delay = 16; parameter start = 2; //port logic clk,rst; logic [17:0] datin1; logic [17:0] datin2; logic [17:0] datout; logic [5:0] addra, addrb, counter, delayest; logic [1:0] flag;//FSM //initial initial begin clk = 0; rst = 1; #8 rst = 0; #2000 $stop; end always #2 clk = ~clk; always @(posedge clk) begin if(rst) begin datin1 <= 0; datin2 <= 0; counter <= 0; end else begin counter <= counter+1; if(counter == start) begin datin1 <= {1'b1,17'b0}; end else begin datin1 <= 0; end if (counter == (start + delay )) begin datin2 <= {1'b1,17'b0}; end else begin datin2 <= 0; end end end //flag control always @(posedge clk) begin if(rst) begin delayest <= 0; addra <= 1; //for primitive output register addrb <= 0; flag <= 0; end else begin if (flag == 2'b00) begin if(datout[17]) begin delayest <= 0; flag <= 2'b01; end end if (flag == 2'b01) begin delayest <= delayest + 1; end if ((flag == 2'b01) & datin2[17]) begin flag <= 2'b10; end if (flag == 2'b10) begin addra <= addra + delayest + 1; flag <= 2'b11;//next flag state end else begin addra <= addra + 1; end addrb <= addrb + 1; end end //IP blk_mem_gen_0 uut( .clka(clk), .wea(1'b1), .addra(addra), .dina(datin1), .clkb(clk), .addrb(addrb), .doutb(datout) ); endmodule

datout是datin1的修正,可见datin1修正后的结果—>datout 已经与datin2对齐。