FPGA设计——inout端口

最近在把zedboard的项目工程搬到性能更好的器件上,除了改zynq核和相应管教外,还需要改几个inout端口和差分LVDS端口。本篇便对inout端口做一个小结。

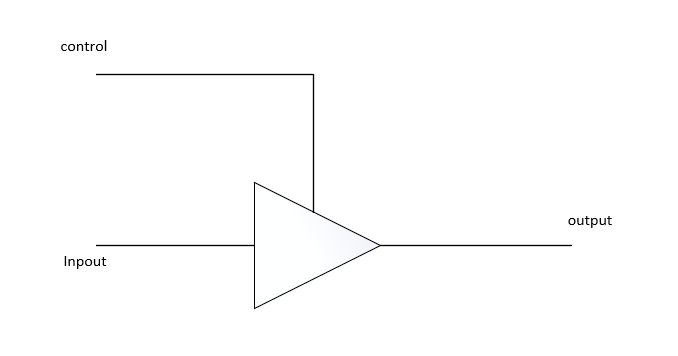

FPGA设计中,大家常用的一般时input和output端口,且在vivado中默认为wire型。而inout端口,正如其名,即可以做输入,也可以做输出端口。其基础是一个三态门构建,由一个控制信号控制输入和输出。

用verilog描述为:

module three_state( din, ctr, dout ); input din,ctr; ouput dout; assign dout = (ctr)?1'bz:din; endmodule

三态门表示存在高电平,低电平和高阻态三种状态,由control信号控制。高低电平大家都了解了,注重看看高阻态。百度解释为:

读完这段话,总结出以下信息:

1)高阻态对下级电路无任何影响,即高阻态不能作为输入了。

2)高阻态是高电平还是低电平是由它后面接的东西定,那说明它能被接,也即可以作为input端口。

那理解完毕,来看看inout端口的应用吧。代码选自ad9361 no-os HDL,为ADI工程师编写

//代码选自ad9361 no-os HDL,为ADI工程师编写

module ad_iobuf ( dio_t, dio_i, dio_o, dio_p); parameter DATA_WIDTH = 1; input [(DATA_WIDTH-1):0] dio_t; input [(DATA_WIDTH-1):0] dio_i; output [(DATA_WIDTH-1):0] dio_o; inout [(DATA_WIDTH-1):0] dio_p; genvar n; generate for (n = 0; n < DATA_WIDTH; n = n + 1) begin: g_iobuf assign dio_o[n] = dio_p[n]; assign dio_p[n] = (dio_t[n] == 1'b1) ? 1'bz : dio_i[n]; end endgenerate endmodule

| 端口 | 含义 |

| dio_t | 视为control |

| dio_i | 视为din |

| dio_o | 视为dout |

| dio_p | 主角,控制端口方向 |

各端口含义如上表所示,该段代码含义为如果dio_t为高电平,dio_p=输入dio_i;

也即dio_o = dio_i,此时为inout端口为output属性;

当dio_t为低电平时,dio_p为高阻态,刚才分析过了,高阻态是高电平还是低电平由后面接的东西定,dio_p可以被外界驱动,视为input端口,也即dio_o会输出dio_p输入的值。

浙公网安备 33010602011771号

浙公网安备 33010602011771号