CUBE配置

一.配置TIM1 6路pwm

1.TIM1 mode选项卡:

slave mode:不同定时器之间同步时用的,disable。

trigger source:见F7中文手册 图 133.连主TIM的TRGO。因为只用TIM1,所以这里disable。

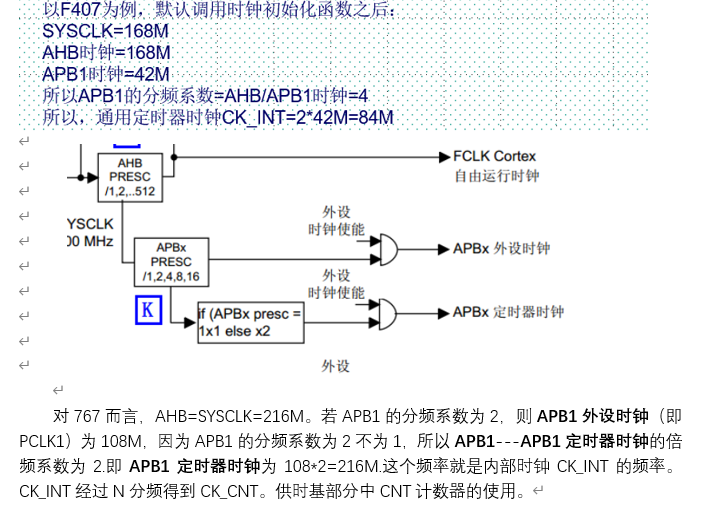

clock source:一般选内部时钟。(CK_INT)。TIM1 TIM8 高级定时器,是挂在APB2时钟线上的,其他定时器是挂在APB1时钟总线上的。中文手册664页。

channel1:选择通道模式,有输出比较模式、pwm模式、输入捕获模式等等。这里选:PWM generation CH1 CH1N。一个通道发出两路互补的PWM。

2.configuration-parameter setting:

counter settings: PSC:预分频器。指的是上文得到的CK_INT ,经过N分频得到CN_CNT。

//定时器时钟:CK_INT。分频系数:PSC。计数个数:ARR。500ms:溢出时间。

//定时器时钟:CK_INT。分频系数:PSC。计数个数:ARR。500ms:溢出时间。

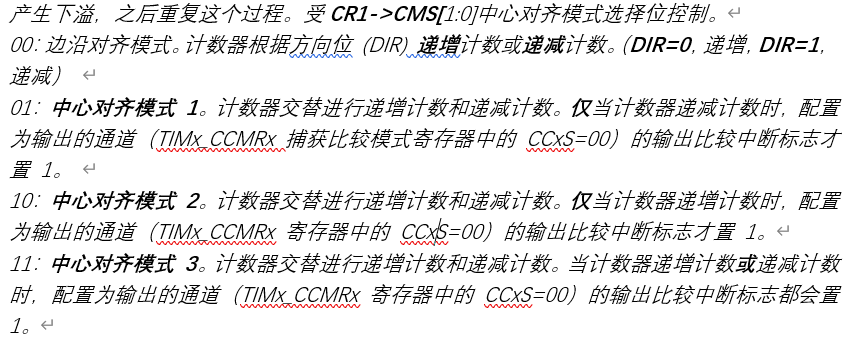

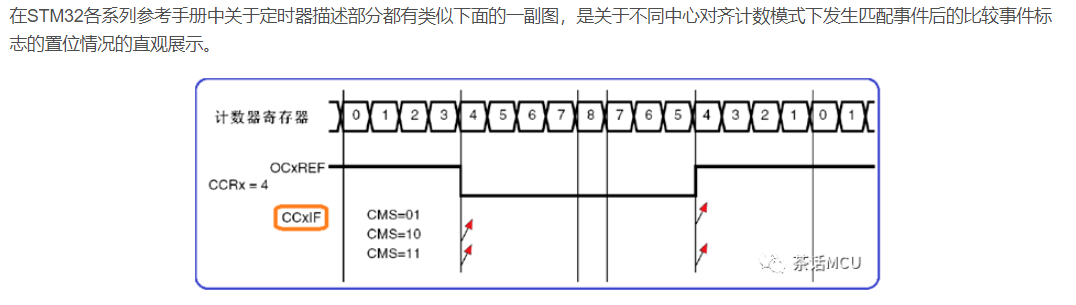

counter mode:向上计数、向下计数、中心计数模式1、2、3。中心计数123区别为:

//中断产生的位置不同。这里选择中心计数模式1.

//中断产生的位置不同。这里选择中心计数模式1.

CKD:这个分频指的是从CK_INT得到tDTS,后者是死区及采样时钟。这里不分频。No division

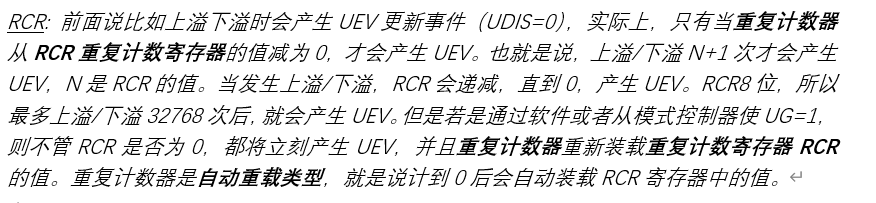

RCR:重复计数器,

//中心对齐模式123指的是 CNT = CCR,在一个周期内,有两个点,决定哪个点产生更新。通常可结合RCR确定adc触发位置。

//中心对齐模式123指的是 CNT = CCR,在一个周期内,有两个点,决定哪个点产生更新。通常可结合RCR确定adc触发位置。

这里设为1. //RCR指的是,发生几次溢出(上溢/下溢,CNT到0或ARR),更新一次事件。通常可作为ADC的触发信号。

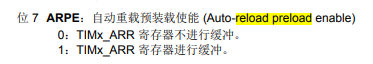

auto reload preload:enable。决定arr寄存器有没有缓冲。

//进行缓冲指的是发生更新事件时才把arr的内容送到影子寄存器。

//进行缓冲指的是发生更新事件时才把arr的内容送到影子寄存器。

trigger output(TRGO) parameters:

MSM bit:enable,用tim1产生一个TRGO信号给到其它定时器(TRGO0)或DAC/ADC(TRGO2)。这里是给到ADC。

TRGO:

TRGO2:选择给到谁。 //不用内部adc的话,这个没啥用。

Break and dead time management (BRK): //需要设置tim bkin引脚。将此引脚连至电压电流(对三相桥过压、过流保护)

BRK state:enable。

BRK polarity:low。即刹车引脚输入低电平的时候,Pwm输出关闭(两路)。

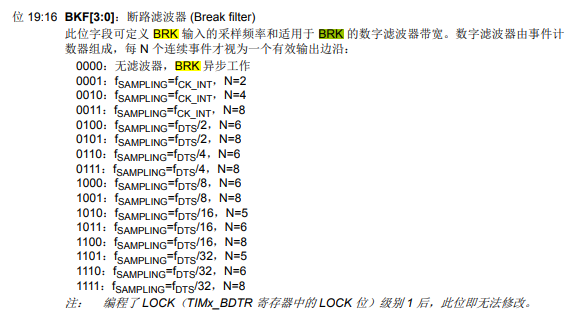

BRK filter:

BRK sources configuration:digital input enable。 digital input polarity:high 。DFSDM:数字滤波,这里没用到(具体功能百度)。

Break and dead time management (BRK2):disable。

Break and dead time management output configuration:

automatic output state:disable。 enable 的意思是检测到低电平了(前边设置的是低电平),就自动关闭pwm。

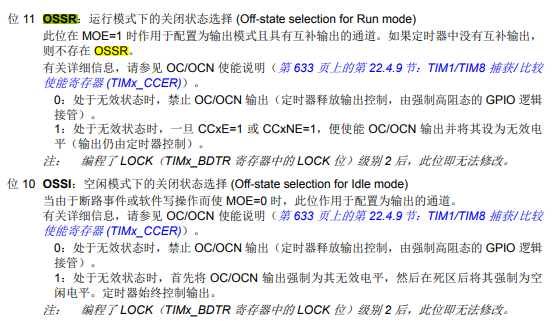

OSSR:enable

OSSI:enable

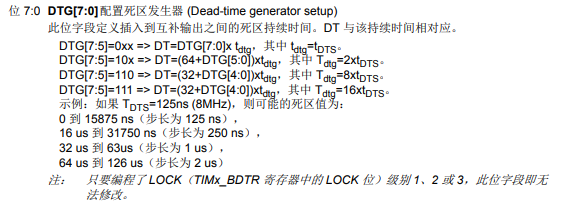

lock configuration:上锁设置,上锁后某些参数就不能更改了。

Dead time :125.

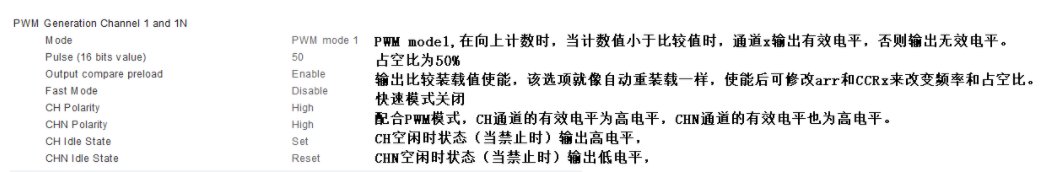

pwm generation chanel1 and 1N:

mode:pwm mode 1 模式12 只是极性不同。

pulse:这个就是占空比。

网上一个图:

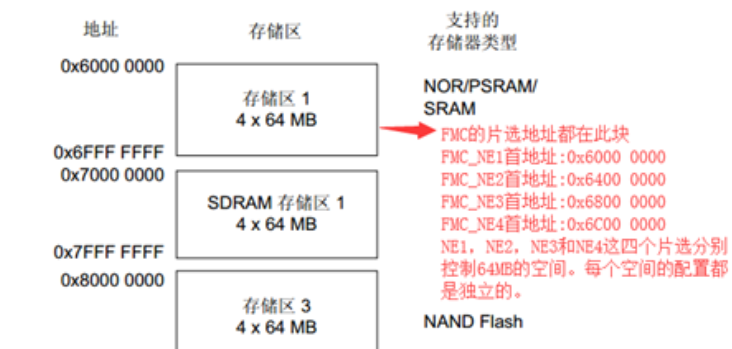

二. H745的FMC

https://blog.csdn.net/Calvin790704/article/details/83866997?utm_medium=distribute.pc_relevant_download.none-task-blog-baidujs-1.nonecase&depth_1-utm_source=distribute.pc_relevant_download.none-task-blog-baidujs-1.nonecase

1.使用HCLK3时钟,200M(H7最高FMC频率)。(与fpga的自己写的bus模块的输入频率一致频率)

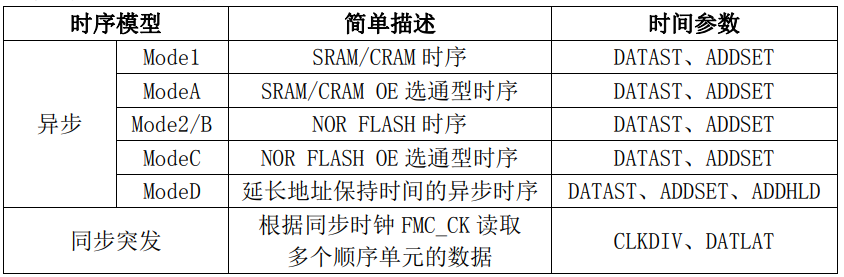

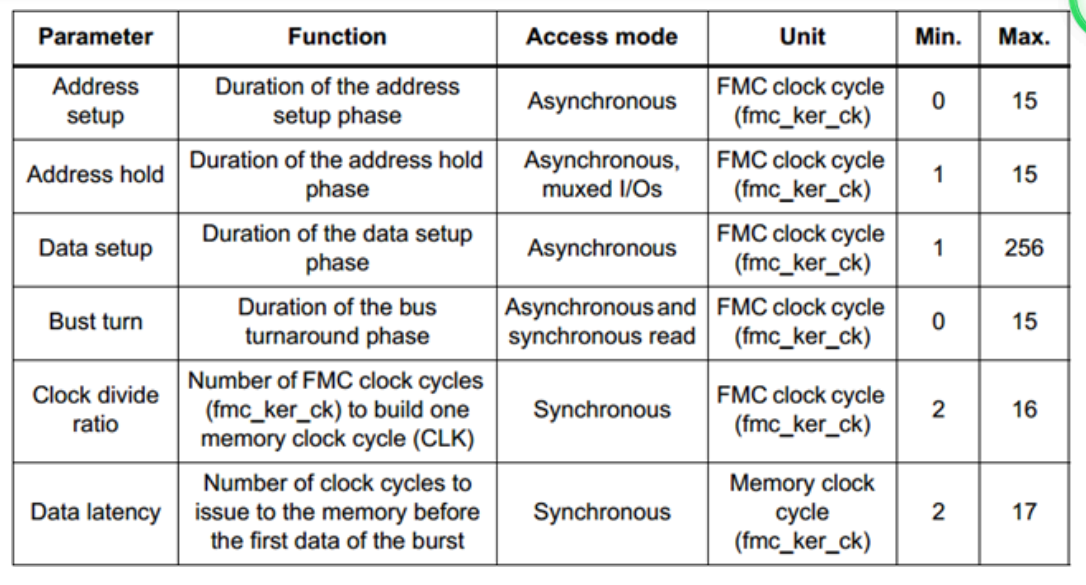

2. 连接斯巴达6。FMC采用突发访问模式.(ADDSET DATASET ADDHOLD).

//同步访问模式:fmc发出一个时钟,给到fpga,主要设置时钟分频参数得到

突发访问模式:fmc和fpga之间无时钟线,主要设置ADDSET DATASET ADDHOLD 等

在实际扩展时,根据选用存储器的特征确定时序模型,从而确定各时间参数与存储器读/ 写周期参数指标之间的计算关系;利用该计算关系和存储芯片数据手册中给定的参数指标,可 计算出 FMC 所需要的各时间参数,从而对时间参数寄存器进行合理的配置。

3.选择SRAM 。

4.选择NE1区。

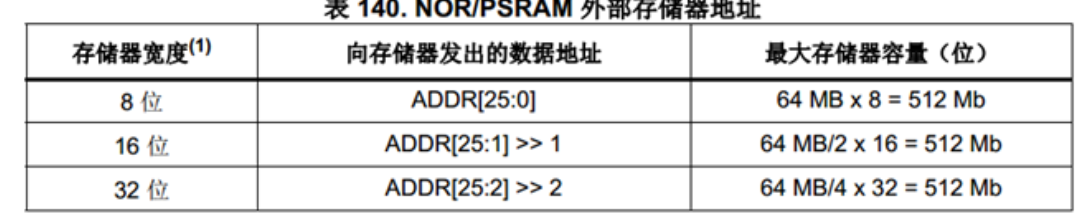

5.地址线8bit(0-26),数据线32bit,与fpga程序一致。实际上还有2条ADDR[27:26],是管理地址映射的,选定NE1后,自动设置成了00。上图所示的0x6_ _ _ _ _ _ _,高四位为6不变,次高4位的前两位就是27:26这两条。

/* 关于地址映射: fmc支持的地址是按字节访问的。如访问0x6 0 0 0 0 0 0 0地址时,是以 一个字节为单位进行读数写数的。如果存储器是只能以16bit数宽进行读写, fmc提供了一种解决方法——地址映射。 (FMC在硬件设计上就提供了一种解决办法,将内部总线ADDR[25:0]措位后接到FMC_A地址引脚上。) */

https://blog.csdn.net/qq_41909909/article/details/107267583 地址移位的理解。

其实就是计组原理中讲得按字节寻址、按字寻址的区别。

如配置外部存储器的宽度为16位, FMC将使用内部的ADDR[25:1]地址来作为对外部存储器的寻址地址FMC_A[24:0]。如果存储器宽度为32位, FMC将使用内部的ADDR[25:2]地址进行外部寻址。

但是不管存储器的宽度是多少, FMC_A[0]都应连接到外部存储器地址A[0]。

这里有一点要补充下,如果外接SDRAM/SRAM配置为16位或者32位带宽的时候,如何实现字节方式的读写。针对这个问题,SDRAM/SRAM都有专门的字节控制引脚,所以操作起来比较方便。

这里fpga是32bit数据总线,但是一共不到10个地址(一个功能一个地址)。

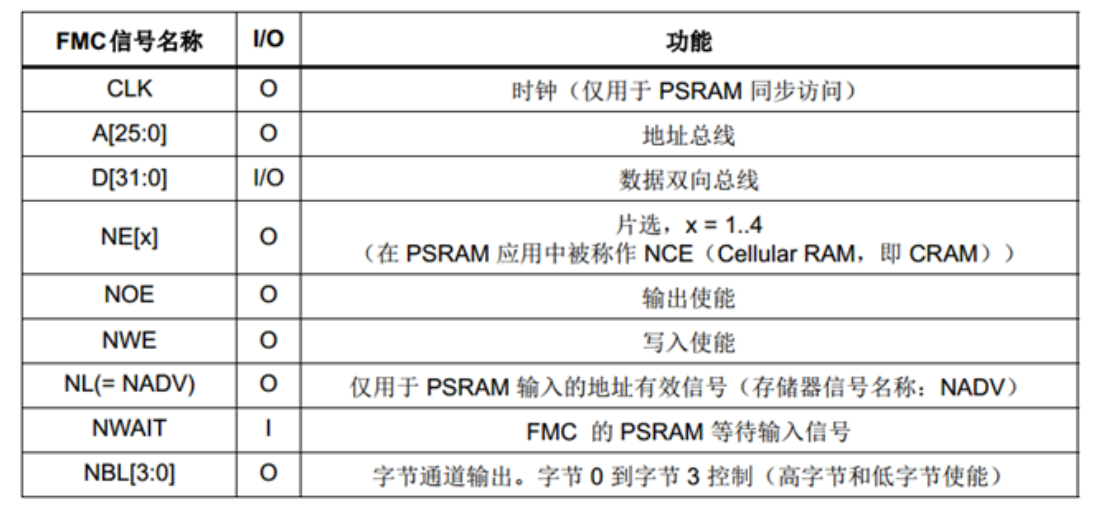

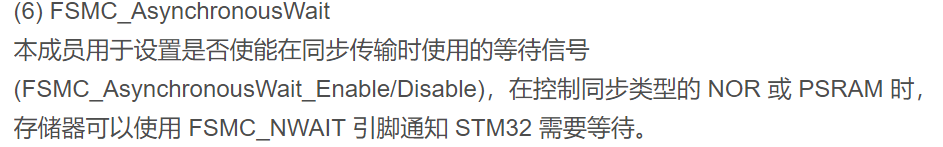

6.wait设置:

我veriloog程序中没有用到FMC_NWAIT,相当于没有这种功能,所以设为0.中文参考手册f7 的315页

7.byte enable设置:

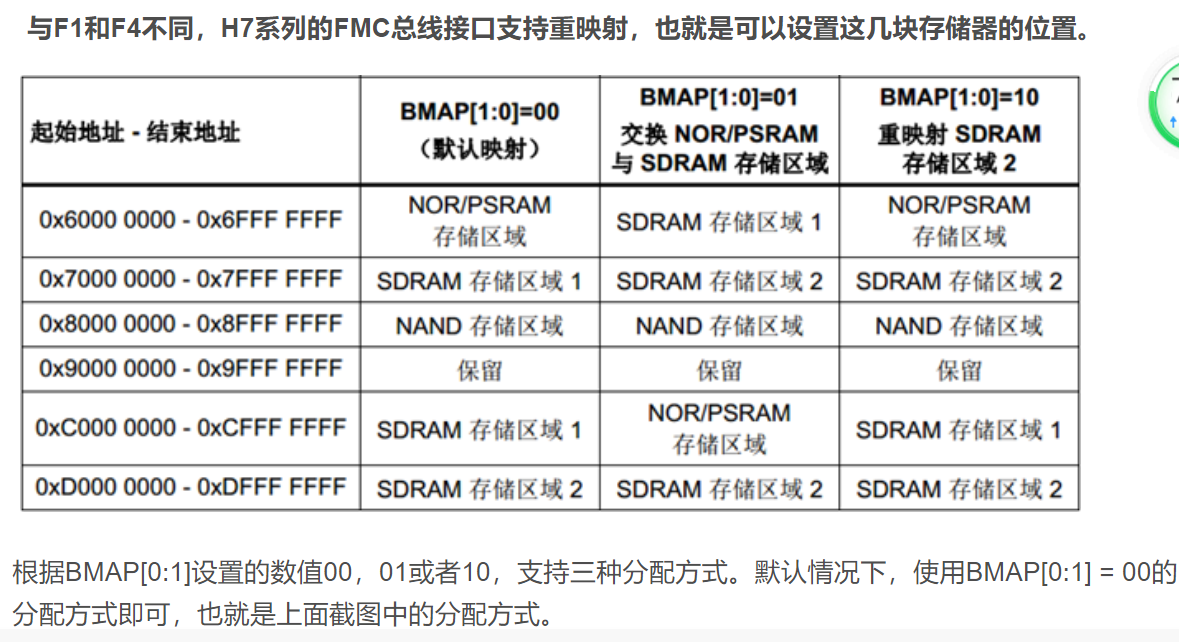

8.bank mapping:H7的地址支持重映射,这里使用默认映射就好。

fpga分配地址(给变量define数)的时候,范围要在这里边。

我fpga中使用8bit作为地址总线。FMC_NE1:首地址0x6000 0000,可以管理的地址范围0x6000 0000到0x63FF FFFF,64MB。

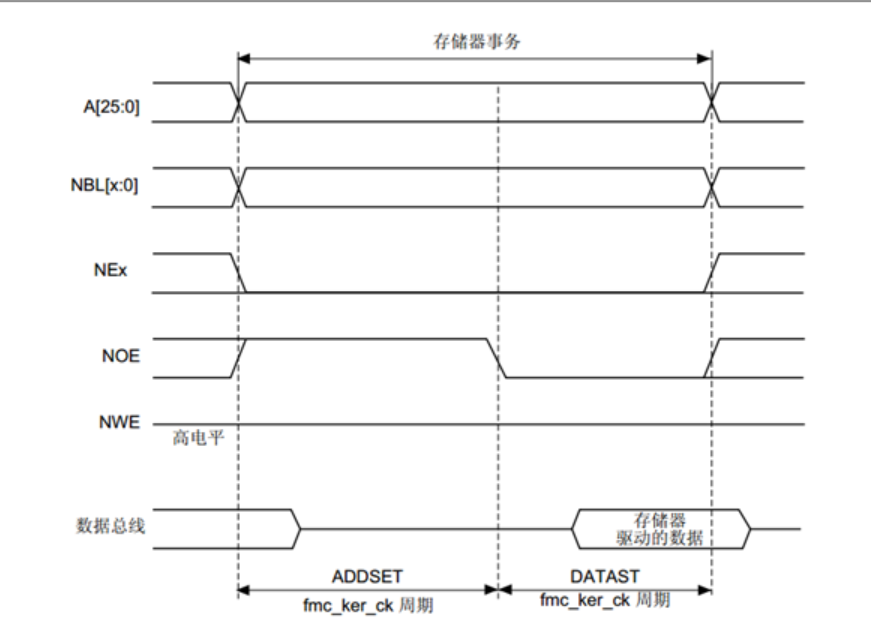

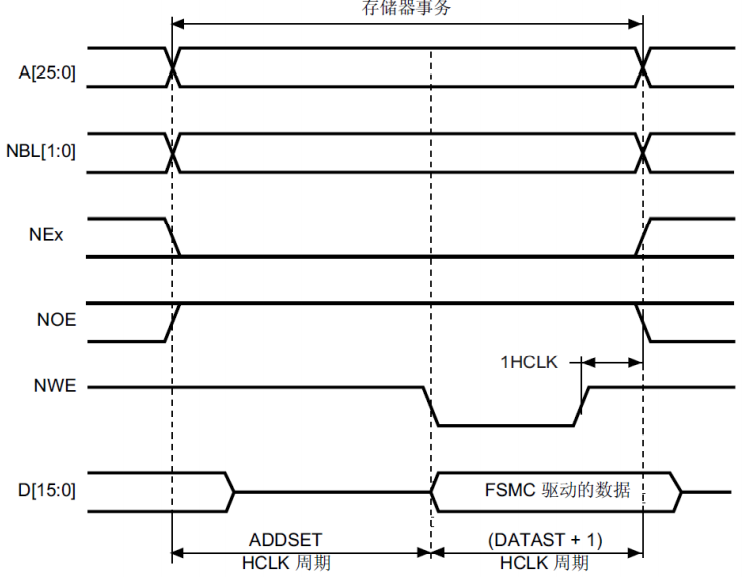

9.模式A时序:

左边是fmc从fpga中读,右边是fmc向fpga中写(模式A)

NBL[x:0]高低字节控制信号,NEx片选信号,NOE读使能信号和NWE写使能前面的字母N(Ngative)示这几个信号低电平有效。

地址信号A[25:0],NBL[x:0]高低字节控制信号,要在NEx片选信号使能前准备就绪。整个读取过程中,NWE写使能信号是不起作用的,被设置为高电平。

NEx片选后,NOE要保持一段时间的高电平,这个时间就是ADDSET地址建立时间(通过寄存器FMC_BTRx可配置)。之后NOE变为低电平,读使能。低电平保持的时间由DATAST数据建立时间(通过寄存器FMC_BTRx可配置)决定。

读取完毕数据后,NOE变成高电平,NEx变成高电平。

A模式没有用到地址保持时间。

9.extended mode:

读取数据、写入数据用一样的时序,所以设为0

10.bus turn around time

没用到,随便设。这个是数据线复用地址线时候用的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号