System Generator简介

前言

System generator 安装之后会在Simulin模块库中添加一些Xilinx FPGA专用的模块库,包括Basic Element,Communication,Control Logic,DataTypes,DSP,Math,Memory,Shared Momory,Tool等模块库,只有使用这里的模块才能进行FPGA算法的仿真以及进行综合等等。

使用这些模块就可以简单的选一些模块,连一些线就能自动生成你需要的HDL代码,将开发人员从底层枯燥的代码编写中解脱出来,将更多的精力放在算法上,非常完美的体现了工具为人服务的理念。

原文地址:http://blog.csdn.net/renshengrumenglibing/article/details/8144170

一、System Generator快速入门

A-Xilinx Blockset库的基本介绍System Generator和Simulink是无缝链接的,可以在MATLAB标准工具栏中直接启动,如图1所示。这些模块都根据其功能划分为不同的库,为了易于使用,又在某些库中添加了部分有广泛应用的模块,所有的模块都按字母顺序排列在Xilinx Index库中。读者需要注意的是:在Simulink环境中,只有通过Xilinx模块搭建的系统才能保证硬件可实现,其地位类似于HDL语言中的可综合语句。

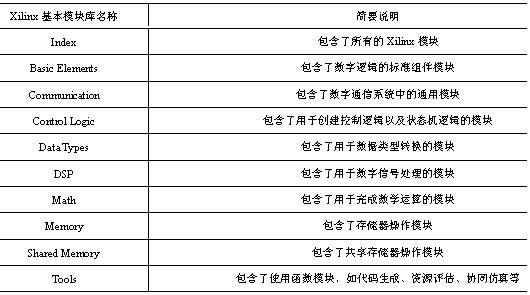

从设计流程中可以看出,熟悉Xilinx DSP基本模块库是设计流程中的关键环节,只有掌握了基本模块的特性和功能,才能更好地实现算法。由Xilinx模块库和System Generator一起,可生成Xilinx可编程器件的最优逻辑,这属于最低层的设计模块,地位等效于IP Core,共有90多个。Xilinx模块库简要说明如表1所列。

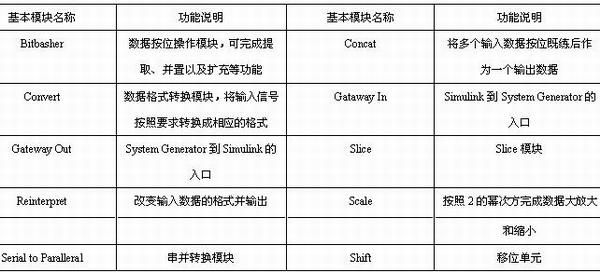

表1 System Generator库的简要说明

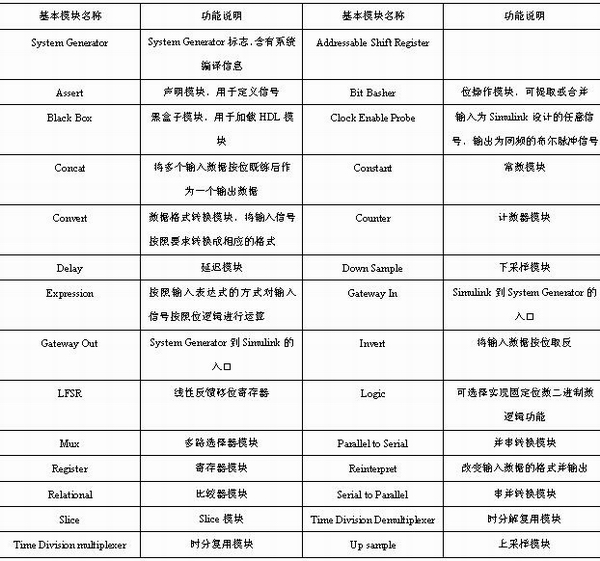

1.基本单元模块

基本单元模块库中包含了数字逻辑的标准组件模块,使用这些模块可插入时间延迟、改变信号速率、引入常数、计数器以及多路复用器等。此外,还包含了3个特殊的模块System Generator标志、黑盒子模块(Black Box)以及边界定义模块,后文将对其进行详细说明。该库中简要的模块说明如表2所列。

表2 基本单元模块的说明列表

2.通信模块

通信应用是FPGA的主要应用领域之一,因此Xilinx的通信模块库提供了用于实现数字通信的各种函数,包括卷积编解码、RS编解码以及交织器等模块。该库中简要的模块说明如表3所列。

表3 通信模块的说明列表

3.控制逻辑模块

控制逻辑主要包括了用于创建各种控制逻辑和状态机的资源,包括了逻辑表达式模块、软核控制器、复用器以及存储器,其简要说明如表4所列。

表4 控制逻辑模块的说明列表

4.数据类型模块

数据类型模块主要用于信号的数据类型转换,包括移位、量化、并/串、串/并转换以及精度调整模块,其简要说明如表5所列。

表5 数据类型模块的说明列表

5.DSP模块

DSP模块是System Generator的核心,该库包含了所有常用的DSP模块,其简要说明如表6所列。

表6 DSP模块的说明列表

6.数学运算模块

数学运算是任何程序所不可避免的,Xilinx提供了丰富的数学运算库,包括基本四则运算、三角运算以及矩阵运算等,其简要说明如表7所列。

表7 数学运算模块的说明列表

7.存储器模块

该库包含了所有Xilinx存储器的Logic Core,其简要说明如表8所列。

表8 存储器模块的说明列表

8.共享储存器模块

表9 共享存储器模块的说明列表

9.工具模块

工具模块包含了FPGA设计流程中常用的ModelSim、ChipScope、资源评估等模块以及算法设计阶段的滤波器设计等模块。该库的模块在设计中起辅助作用,都是设计工具,一般不能生成HDL设计,其简要说明如表10所列。

表10 工具模块的说明列表

B-其他模块

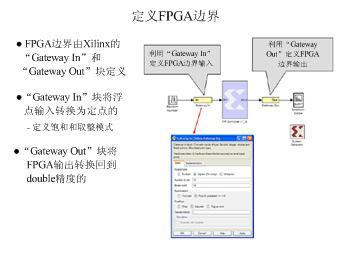

1.FPGA边界定义模块

System Generator是FPGA实现和算法开发之间桥梁,通过两个标准模块“Gateway In”和“Gateway Out”来定义Simulink仿真模型中FPGA的边界。“Gateway In”模块标志着FPGA边界的开始,能够将输入的浮点转换成定点数。“Gateway Out”模块标志着FPGA边界的结束,将芯片的输出数据转换成双精度数。在Simulink环境中双击这两个模块会弹出配置对话框,可以设定不同的转换规则,如图10所示。

图10 转换模块示意图

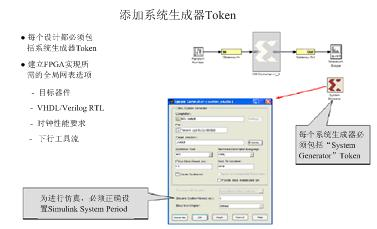

2.System Generator标志

每个System Generator应用框图都必须至少包含一个System Generator标志,如图11所示,否则会提示错误。标志模块用来驱动整个FPGA实现过程,不与任何模块相连。双击标志模块,可以打开属性编辑框,能够设置目标网表、器件型号、目标性能以及系统时钟频率等指标。

3.建立简易的DSP设计

一旦定义了FPGA边界就可以通过Xilinx DSP模块集合来建立各种DSP设计,包括滤波器、存储器、算术运算器、逻辑和比特操作器等丰富资源,每个模块都有详细的工作频率和比特宽度定义。标准的Simulink模块不能在“Gateway In”和“Gateway Out”之间使用,但常用来产生测试数据以及对FPGA的输出数据进行处理和分析。下面给出一个简单的FPGA系统设计实例。

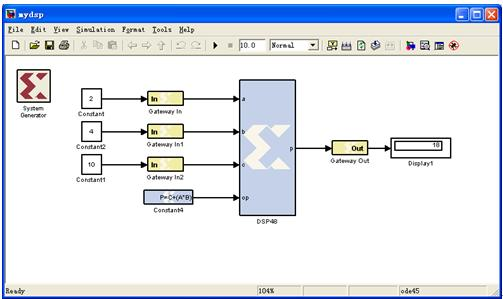

例:使用System Generator建立一个3输入(a、b、c)的DSP4模块的计算电路,使得输出p=c+a*b,并利用标准的Simulink模块对延迟电路进行功能验证。

1)打开Simulink库浏览器并建立一个新的Simulink模型,并保存为mydsp.mdl。

2)在浏览器中选择Xilinx DSP48模块,并将其拖拽到mydspmydelay.mdl;按照同样的方法添加边界定义模块以及System Generator标志模块。

3)为了测试DSP计算电路,添加Simulink标准库中的常数模块(Constant)和显示器(Display)模块。其中常数模块用于向DSP计算电路灌数据,作为测试激励;显示器则用于观测输出数据。

4)连接模块,将所有的独立模块连成一个整体。其中Xilinx模块之间的端口可以直接相互连接,直接从一个端口拖拽鼠标到另一个端口来完成,或选中目标模块,按住Ctrl键,再点击要连接的模块,Simulink即可自动将两个模块连接起来;而Xilinx模块和非Xilinx模块之间的连接则需要边界模块(Gateway)来衔接。经过连接的设计如图12所示。

图12 延迟模块以及测试平台的组成架构

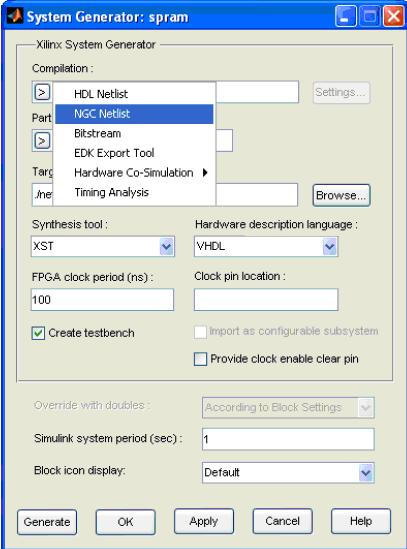

5)设定系统参数。双击“System Generator”模块,会出现系统设定对话框,如图13所示。其中“Compilation”栏选择编译生成对象,包括HDL网表、FPGA配置比特流、NGC网表、EDK导出工具、硬件协仿真类型以及时序分析文件等6种类型,本例选择HDL网表类型,会生成ISE工程以及相应的HDL代码;“Part”栏用于选择芯片型号,本例选择Spartan3E xc4vsx55-12ff1148。“Target”栏用于选择目标文件存放路径,本例使用默认值,则会在mydelay.mdl所在文件夹中自动生成一个netlist的文件夹,用于存放相应的输出文件。综合工具选择XST,HDL语言选择Verilog类型,系统时钟设的周期为100ns,即为10MHz。 “Clock Pin Location”栏的文本框中输入系统时钟输入管脚,则会自动生成管脚约束文件(由于本例只是演示版,所以该项空闲)。此外,可选中“Create testbench”选项,自动生成设计的测试代码。各项参数确认无误后,单击“OK”键,保存参数。

图13 系统参数设定对话框

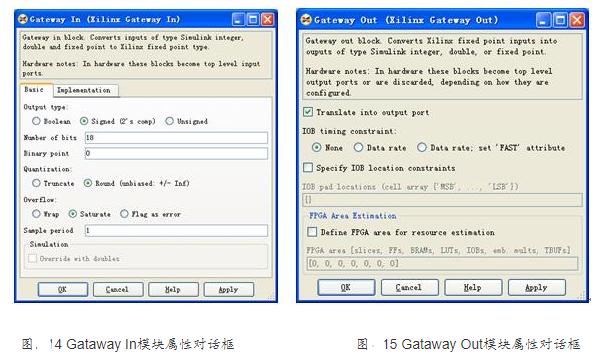

6)设置关键模块参数。双击“Gataway In”、“Gataway Out”模块,会弹出图14和图 15所示的对话框。Gataway In模块属性可查看输入数据位宽和量化规则。

7)运行测试激励。当参数设置完成后,点击工具栏的“ ”按键,即可运行Simulink仿真,可以看到显示器输出为18,表明设计的功能是正确的。

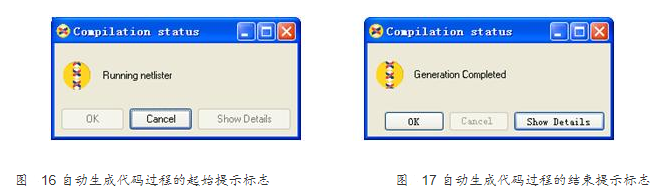

8)生成HDL代码。单击图13中的“Generate”按键,System Generator可自动将设计转化成HDL代码。整个转化过程的起始和结束提示界面分别如图16和图 17所示。

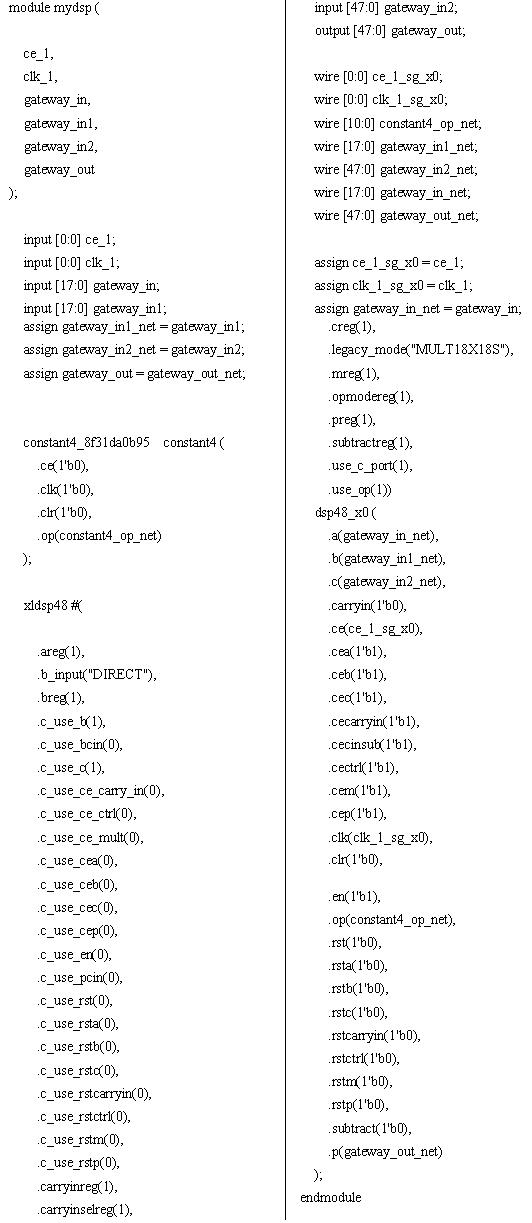

读者可在相应的文件夹的“netlist sysgen”子目录中打开“nonleaf_results.v”文件,查看相应的代码,如下所示(为了节约篇幅,分栏显示),用户可将其作为子模块直接使用。

二、System Generator中的信号类型

System Generator是面向硬件设计的工具,因此数据类型只能是定点的,而Simulink中的基本数据类型是双精度浮点型,因此Xilinx模块和Simulink模块连接时需要通过边界模块来转换。“Gateway In”模块把浮点数转换成定点数,“Gateway Out”把定点数转换成浮点数。此外,对于Simulink中的连续时间信号,还必须经过“Gateway In”模块的采样转换才能使用。

System Generator中的数据类型命名规则是非常简易且便于记忆的形式,如Fix_8_6表示此端口为8比特有符号数,其中6比特为小数部分。如果是无符号数,则带有“Ufix”前缀。在System Generator中,可通过选择 “Format” 菜单中的“Port/Signal Display Port Data Types”命令,来显示所有端口的数据类型,形象显示整个系统的数据精度。

Xilinx模块基本上都是多形态的,即可根据输入端口的数据类型来确定输出数据类型,但在有些情况下需要扩展信号宽度来保证不丢失有效数据。此外,也允许设计人员自定义模块的输入、输出数据的量化效果以及饱和处理。在图14所示的“Gateway In”模块属性对话框中,“Output type”选择数据为布尔型、有符号数还是无符号数;“Number of bits”即为定点数的位宽;“Binary point”为小数部分的宽度;“Quantization”选择定点量化模式;“Overflow”用于设定饱和处理模式;“Sample period”用于对连续时间信号的采样。因此按照System Generator的数据形式命名规则,“Gateway In”模块的数据类型为Fix/Ufix_(Number of bits)_(Binary point )。

此外,还有DSP48 instruction,显示为“UFix_11_0”,是Xilinx针对数字信号处理的专用模块,用于实现乘加运算。

三、 自动代码生成

System Generator能够自动地将设计编译为低级的HDL描述,且编译方式多样,取决于System Generator标志中的设置。为了生成HDL代码,还需要生成一些辅助下载的文件工程文件、约束文件等,和用于验证的测试代码(HDL testbench)。A-编译并仿真System Generator模块

前面已经提到要对一个System Generator的设计进行仿真或者将其转化成硬件,则设计中必须包含一个System Generator生成标志。也可以将多个生成标志分布于不同的层中(一层一个),在层状结构中,处于别的层下的称为从模块,不属于从模块的则为主模块。但是特定的参数(如系统时钟频率)只能在主模块中设置。

对于任一添加的模块,都可以在System Generator模块中指定其代码生成方式和仿真处理形式,要编译整个系统,在顶层模块中利用System Generator模块生成代码即可。

不同编译类型的设定将会产生不同的输出文件,可选的编译类型包括两个网表文件类型(HDL网表和NGC网表)、比特流文件类型、EDK导出工具类型以及时序分析类型等4类。

- HDL网表类型是最常用的网表结构,其相应的输出结果包括HDL代码文件、EDIF文件和一些用于简化下载过程的辅助文件。设计结果可以直接被综合工具(如XST等)综合,也可以反馈到Xilinx物理设计工具(如ngdbuild、map、par和bitgen等)来产生配置FPGA的比特流文件。编译产生的文件类型如ISE中是一致的。NGC网表类型的编译结果和HDL网表类似,只是用NGC文件代替了HDL代码文件。

- 比特流文件类型的编译结果是直接能够配置FPGA的二进制比特流文件,并能直接在FPGA硬件平台上直接运行的。如果安装了硬件协仿真平台,可以通过选择“Hardware Co-simulation > XtremeDSP Development Kit > PCI and USB”,生成适合XtremeDSP开发板的二进制比特流文件。

- EDK导出工具类型的编译结果是可以生成直接导入Xilinx嵌入式开发工具(EDK)的工程文件以及不同类型的硬件协仿真文件。

- 时序分析类型的编译结果是该设计的时序分析报告。

B-编译约束文件

在编译一个设计时,System Generator会根据用户的配置产生相应的约束文件,通知下载配置工具如何处理设计输入,不仅可以完成更高质量的实现,还能够节省时间。

约束文件可控的指标包括:

- 系统时钟的周期;

- 系统工作速度,和系统时钟有关、设计的各个模块必须运行的速度;

- 管脚分配;

- 各个外部管脚以及内部端口的工作速度。

约束文件的格式取决于System Generator模块的综合工具:对于XST,其文件为XCF格式;对于Synplify/Synplify Pro,则使用NCF文件格式。

系统时钟在System Generator标志中设定,编译时将其写入约束文件,在实现时将其作为头等目标。在实际设计中,常常包含速度不同的多条路径,其中速度最高的采用系统时钟约束,其余路径的驱动时钟只能通过系统时钟的整数倍分频得到。当把设计转成硬件实现时,“Gateway In”和“Gateway Out”模块就变成了输入、输出端口,其管脚分配和接口数据速率必须在其参数对话框中设定,编译时会将其写入I/O时序约束文件中。

C-HDL测试代码

通常System Generator设计的比特宽度和工作频率都是确定的,因此Simulink仿真结果也要在硬件上精确匹配,需要将HDL仿真结果和Simulink仿真结果进行比较,才能确认HDL代码的正确性。特别当其包含黑盒子模块时,这样的验证显得格外重要。System Generator提供了自动生成测试代码的功能,并能给出HDL代码仿真正确与否的指示。

假设设计的名字是<design>,双击顶层模块的System Generator标志,将Compilation选项设为HDL Netlist,选中Create Testbench选项,然后点击Generate选项,不仅可以生成常用的设计文件,还有下面的测试文件:

- <design>_tb.vhd/.v文件,包含完整的HDL测试代码;

- Various.dat文件,包含了测试代码仿真时的测试激励向量和期望向量;

- 脚本Scripts vcom.do和vsim.do文件,用于在Modelsim中完成测试代码的编译和仿真,并将其结果和自动编译产生的HDL测试向量进行比较。

Various.dat文件是System Generator将通过“Gataway In/Out”模块的数据保存下来而形成的,其中经过输入模块的数据是测试激励,而通过输出模块的数据就是期望结果。测试代码只是简单的封装器,将测试激励送进生成的HDL代码,然后对输出结果和期望结果完成比较,给出正确指示。

四、 编译MATLAB设计生成FPGA代码

Xilinx公司提供了两种方法将MATLAB设计.m文件转化为HDL设计,一种就是利用AccelDSP综合器;另一种就是直接利用MCode模块。前者多应用于复杂或高速设计中,常用来完成高层次的IP核开发;而后者使用方便,支持MATLAB语言的有限子集,对实现算术运算、有限状态机和逻辑控制是非常有用的。本节内容以介绍MCode模块为主。

MCode模块实现的是装载在里面的.m函数的功能。此外,还能够使用Xilinx的定点类型数对.m函数进行评估。该模块使用回归状态变量以保证内部状态稳定不变,其输入、输出端口都由.m函数确定。

要使用MCode模块,必须实现编写.m函数,且代码文件必须和System Generator模型文件放在同一个文件夹中,或者处于MATLAB路径上的文件夹中。下面用两个实例来说明如何使用MCode模块。

例:使用MATLAB编写一个简单的移位寄存器完成对输入数据乘8以及除以4的操作,并使用MCode将其编译成System Generator直接可用的定点模块。

1.相关的.m函数代码为:function [lsh3, rsh2] = xlsimpleshift(din) % [lsh3, rsh2] = xlsimpleshift(din) does a left shift 3 bits and a % right shift 2 bits. The shift operation is accomplished by % multiplication and division of power of two constant. lsh3 = din * 8; rsh2 = din / 4;

2.将.m函数添加到下列三个位置之一:

- 模型文件存放的位置;

- 模型目录下名字为private的子文件夹;

- MATLAB路径下。

然后,新建一个System Generator设计,添加MCode模块,双击模块,在弹出页面中,通过Browse按键将.m函数和模型设计关联起来,如下图所示。

3.添加边界模块、Sytem Generator模块、正弦波测试激励以及示波器模块构成完整的设计,如下图所示。

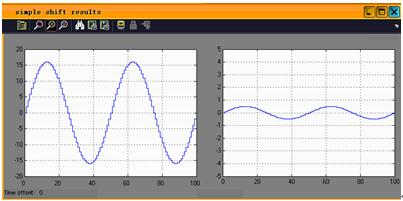

4.运行仿真,得到的结果如下图所示,从中可以看出,设计是正确的,正确实现了.m文件的功能。左图将信号放大了8倍,右图将信号缩小了4倍。

5.自动生成代码,得到的Verilog文件如下所列。

module myshift ( din, dout1, dout2 ); input [15:0] din; output [15:0] dout1; output [15:0] dout2; wire [15:0] din_net; wire [15:0] dout1_net; wire [15:0] dout2_net; assign din_net = din; assign dout1 = dout1_net; assign dout2 = dout2_net; mcode_6b96190926 mcode ( .e(1'b0), .lk(1'b0), .lr(1'b0), .in(din_net), .sh3(dout1_net), .sh2(dout2_net) ); endmodule

五、子系统的建立和使用

System Generator设计经常作为大型HDL设计的一部分,本节就介绍如何使用System Generator来建立子系统模块,以及如何在整个系统中对其进行仿真。

A-子系统的建立以及仿真方法

子系统就是HDL语言中的模块,也类似于C++语言中的函数,是有效执行自顶向下设计的必备手段。如果将一个复杂设计完全在一个单独设计中实现,则该设计的验证和复查工作将是设计人员的噩梦。此外,从设计复用的角度讲,子系统可以IP核的方式为多个设计使用,具有高的可重用性,能节省大系统的开发时间。

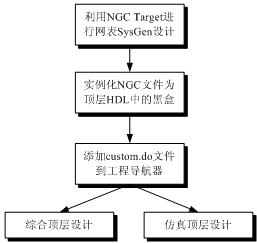

建立子系统最简单的方法就是利用NGC二进制网表文件,将System Generator设计封装成一个单独的二进制模块,这样综合工具将其作为黑盒子看待。在建立子系统时,管脚约束不能在Gataway模块中定义,同样时钟管脚也不能在System Generator模块中定义,应通过网表编辑器来指定物理约束,这是因为NGC网表中不仅包括了逻辑设计,还包括了设计的约束信息。在复杂系统中建立子系统的设计流程如下所示:

1.NGC网表文件

生成NGC网表是建立子系统的第一步。在System Generator标志中将编译生成文件类型选为NGC List。如果设计中有时钟驱动电路,点击Generate后,会在目标文件夹生成“<design>_cw.ngc”文件,否则会生成“<design>.ngc”文件,其中<design>就是设计的名字。NGC网表文件包括设计中所有的逻辑和约束信息,这意味着将System Generator生成的所有HDL文件、内核以及约束等文件封装成一个单独的文件。

2.设计规则

在复杂系统中使用子模块时,必须遵循下面两条规则。

首先,不能在子模块设计文件中出现“Gateway In”、“Gateway Out”以及System Generator标志模块,否则NGDBuild工具会产生下面的警告:

WARNING: NgdBuild:483 - Attribute "LOC" on "clk" is on the wrong type of object. Please see the Constraints Guide for more information on this attribute.

其次,不能在综合的时候往NGC网表文件中插入I/O缓存器,否则会报错。I/O缓存器只能在顶层模块中使用。

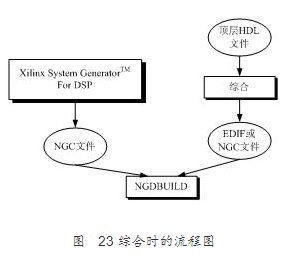

3.逻辑综合

当使用子系统的NGC网表文件综合时,其流程如图23所示。NGC模块可在顶层模块中以黑盒子的方式直接例化。为了简化该过程,当通过NGC目标编译后,System Generator提供了HDL例化模板,保存在设计路径,且以“<design>_cw.veo”命名。当选择VHDL语言时,则其模板名为“<design>_cw.vho”。

4.仿真

把System Generator模型编译成NGC目标后,生成的HDL文件却只能完成HDL仿真,不能在ISE中综合。由于HDL文件不能包含在工程中,如果要在HDL仿真器中运行整个设计,就必须指定用户.do文件。除了HDL文件之外,还需要将内存初始化文件(.mif)和系数文件(.coe)和HDL文件放在同一文件夹中。

B-可配置子系统的建立

可配置子系统是一类可以作为标准元件使用的Simulink模块,但又和标准元件模块不同,其存在多种可选功能,每一种功能都可以实现,可以让用户灵活选择。以可配置FIR滤波器为例,实现快速滤波器需要很多资源,而许多低速的滤波器却只需要相对很少的资源,将其做成可配置的模块,就可以允许用户根据实际情况在速度和硬件代价之间做出最优平衡。这体现了可配置子模块最大的优势。

1.定义一个可配置子模块

可通过新建Simulink库来定义可配置子系统,且可选模块的实现也由库来管理。下面给出新建建库的具体步骤:

(1)新建一个空白库,如图24所示。

(2)在库里添加基本实例模块,如图25所示。基本实例模块可以是System Generator中的任意组件。

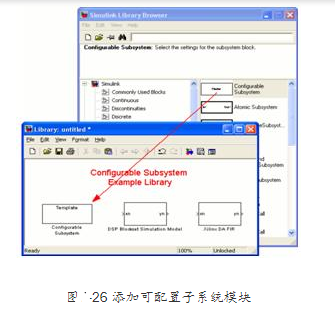

(3)在库里面添加可配置子系统模版,如图26所示。模版可以在Simulink库浏览器中找到,其具体位置为“Simulink/Ports & Subsystems/Configurable Subsystem”。如果有需要,用户可以修改该模版的名字。

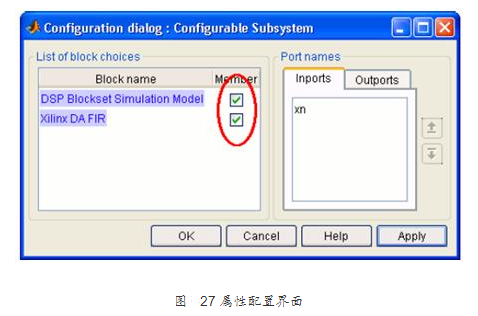

(4)保存库文件,然后双击模版模块,会弹出如图27所示的属性配置界面。根据实现的需要选中相关模块的检验框。最后单击“OK”再次保存库文件。

2.使用可配置子系统

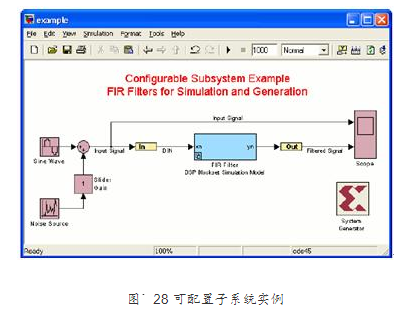

要在设计中使用可配置子系统,先按照上面的步骤定义子系统,然后打开库,将需要的模版模块拖到设计中合适的位置,这样设计中就有了可配置子系统的实例,如图28所示的FIR滤波器模块。

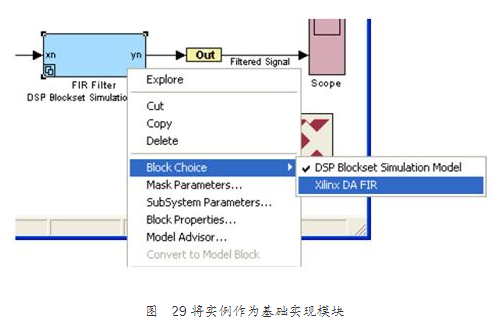

在实例模块上点击右键,然后选择Block Choice选项中的Xilinx DA FIR,将实例作为基础实现模块使用。如图29所示。

3)在可配置子模块中添加和删除实例模块

添加和删除子系统是编辑、修改可配置子系统的基本操作,按照下面的步骤可以从可配置子系统中删除实例模块:

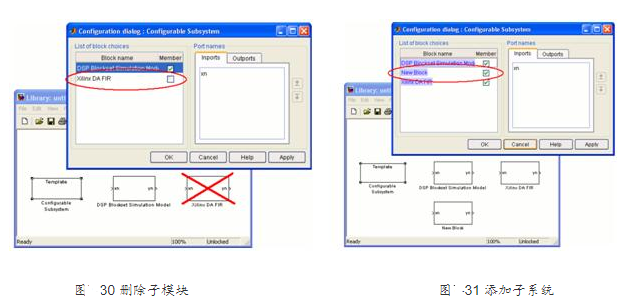

- 打开并解锁子系统的库;双击模版模块,然后在弹出的用户界面中取消相应模块检验框的选定,单击“OK”就可以删除掉相应的子模块,如图30所示;再保存库,重新编译即可;最后仍需要在设计更新子系统。

对于添加实例模块的步骤如下:首先,打开并解锁子系统的库;然后将实例模块拖到子系统设计中,双击模版模块;在弹出的用户界面中选中所需模块检验框,单击“OK”即可,如图31所示;再保存库,重新编译;在已有的设计中更新子系统。

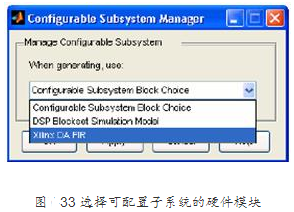

- 生成可配置子模块的硬件电路

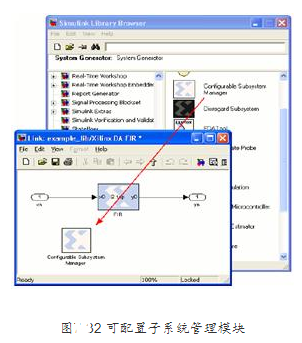

在System Generator中,模块可用于仿真和产生硬件。有时对于一个可配置子系统,最佳的方式是其既可以成为仿真基础模块,也可以用来生成硬件电路。例如将可配置子系统在仿真时作为普通的模块来产生仿真结果,在实现时作为黑盒子产生功能电路的HDL代码,就是一种常用方式。System Generator提供了可配置子系统管理模块来达到上述目的,其使用方法如下:

首先,打开、解锁可配置子系统的库文件(除了模版模块),然后双击该模块;

其次,将可配置子系统管理模块拖到打开的库中,该管理模块可以在“Xilinx Blockset/Tools/ Configurable Subsystem Manager”路径中找到,如图32所示。

最后,双击管理模块打开其属性配置GUI,选择可配置子系统中生成硬件电路的模块,如图33所示。单击“OK”保存子系统和库文件退出即可。