时钟的相关概念

主要是PLL、DCM:

PLL,即锁相环。是 FPGA 中的重要资源。由于一个复杂的 FPGA 系统往往需要多个不同频率,相位的时钟信号。所以,一个 FPGA 芯片中 PLL 的数量是衡量 FPGA 芯片能力的重要指标。FPGA 的设计中,时钟系统的 FPGA 高速的设计极其重要。

DCM(digital clock manager)是较高级FPGA产品中集成的专门用于时钟综合、消除时钟偏斜和进行时钟相位调整的固件资源,利用DCM完成时钟倍频、分频、相移十分方便。

本文参考:维基百科。

这就说明,通过锁相环得到的信号。通常有一个clk输入,可能会有如下输出:

- clk_out,跟clk相同,用于feedback

- clk_2x,2倍的clk信号

- clk_90,跟clk差90度的时钟

- clk_180,跟clk差180度的时钟

- clk_270,跟clk差270度的时钟

- clk_div,clk乘以N再除以M得到的时钟,N、M为正整数(也是有一定范围的)。

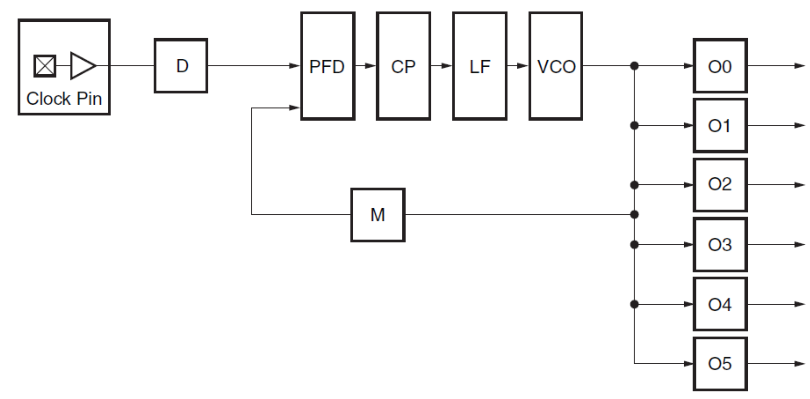

一个锁相环电路通常由以下模块构成:

A-鉴相器

鉴频鉴相器(Phase Frequency Detector)是一种能将两种输入信号的相位进行比较并输出频率误差和相位误差信息的设备,它有两个不同的输入信号。在锁相环中,输入信号通常一个来自压控振荡器,另一个由外部信号源提供,其输出信号将指导后续环路如何调整来继续锁相。

B-低通滤波器

将PFD中生成的差异信号的高频成分滤除,保留直流部分。

C-压控振荡器

根据输入电压,输出对应频率的周期信号。利用变容二极管(偏置电压的变化会改变耗尽层的厚度,从而影响电容大小)与电感构成的LC谐振电路构成,提高变容二极管的逆向偏压,二极管内耗尽层变大,电容变小,LC电路的谐振频率提高,反之,降低逆向偏压时,二极管内电容变大,频率降低。

D-反馈回路

通常由一个分频器实现。将VCO的输出降低到与基准信号相同级别的频率才能在PFD中比较

Spartan-6中的PLL结构:

总结一下——

PLL工作的基本原理就是将压控振荡器的输出经过分频后与基准信号输入PFD,PFD通过比较这两个信号的频率差,输出一个代表两者差异的信号,再经过低通滤波器转变成一个直流脉冲电压去控制VCO使它的频率改变。这样经过一个很短的时间,VCO的输出就会稳定下来。

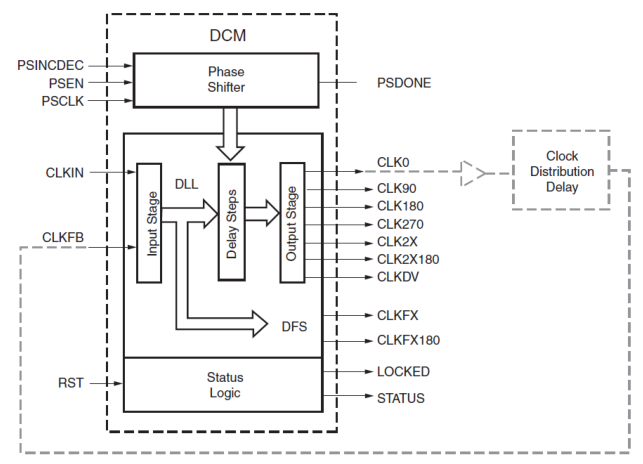

三、DCM基本概念

数字时钟管理器(DCM)是一种用于管理时钟架构并有助于时钟信号成形和操控的模块。DCM 内含一个延迟锁相环(DLL),可根据输入时钟信号,去除 DCM 输出时钟

信号的歪斜,从而避免时钟分配延迟。DLL 内含一个延迟元件和控制逻辑链路。延迟元件的输出是输入时钟延迟所得。延迟时间取决于延迟元件在延迟链路中的位置。这种延迟体现为针对原始时钟的相位改变或相移,这就是所谓的“数字相移”。DCM 内部的功能框图如下图所示:

其他

程序中添加了一个 ODDR2,使得 pll_ip 的BUFG 输出的时钟信号能够输出到 FPGA 的普通 IO。因为如果直接从 BUFG 上连接到 OBUF上,在编译器 map 的过程中就会出现错误, 为避免这个错误,另一种方法就是在约束文件中加上一条约束,让编译器忽略时序约束的要求,直接通过普通逻辑资源连接。但这样 Clock输出的时延和 Jitter 都会变差。

///////////////调用 ODDR2 使时钟信号通过普通 IO 输出//////////////////

ODDR2 #(

.DDR_ALIGNMENT("NONE"), // Sets output alignment to "NONE", "C0" or "C1"

.INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1

.SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset

) ODDR2_inst (

.Q(clk_out), // 1-bit DDR output data

.C0(pll_clk_o), // 1-bit clock input

.C1(~pll_clk_o), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D0(1'b1), // 1-bit data input (associated with C0)

.D1(1'b0), // 1-bit data input (associated with C1)

.R(1'b0), // 1-bit reset input

.S(1'b0) // 1-bit set input

);